- 全部

- 默认排序

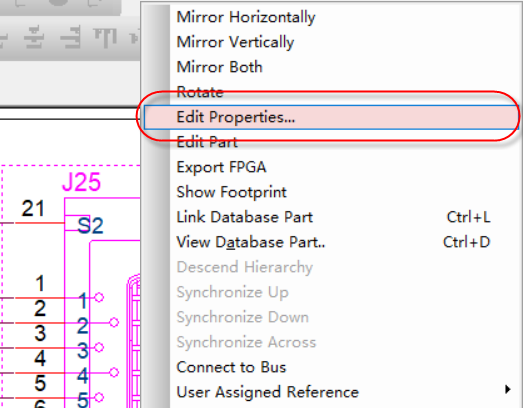

答:第一步,切换到原理图目录页,选中原理图根目录或者是其中某一页的原理图,点击右键,编辑器件属性,如图3-48所示; 图3-48 编辑元器件属性示意图第二步,打开器件的属性框,找到PCB Footprint这一栏,批量填入元器件的封装即可,这样原理图中所有的器件封装都匹配了,如图3-49所示: 图3-49 编辑元器件属性示意图第三步,对于所有的封装,我们可以在原理图绘制页面进行显示,操作如下:任意打开一页原理图页面,框选所有的元器件,点击右键

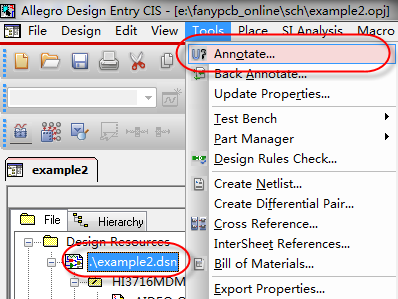

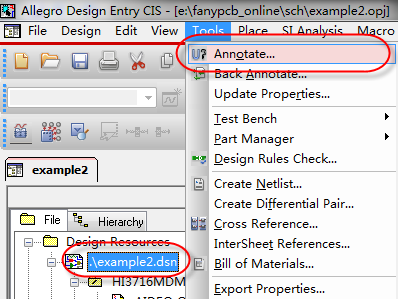

答:第一步,选中整个原理图的根目录,然后执行菜单Tools-Annotate,如图3-52所示,进行原理图选项的编辑; 图3-52 原理图编译示意图第二步,在弹出的原理图编译界面中,如图3-53所示,在Action选项中,现将原理图本身已经存在的位号全部复位,点击Reset Part References to “?”,则全部的位号则变成的问号,如图3-54所示; 图3-53 原理图编译界面设置示意图 图3-54 原理图所有位号复

答:第一步,选中整个原理图的根目录,然后执行菜单Tools-Annotate,如图3-56所示,进行原理图选项的编辑;图3-56 原理图进行编译示意图第二步,然后对器件的位号进行复位的操作。在弹出的原理图编译界面中,如图3-57所示,在Action选项中,现将原理图本身已经存在的位号全部复位,点击Reset Part References to “?”,则全部的位号则变成的问号,可参照图3-57所示。 图3-57 原理图编位号复位设置示意图第三步,把所有的位号进

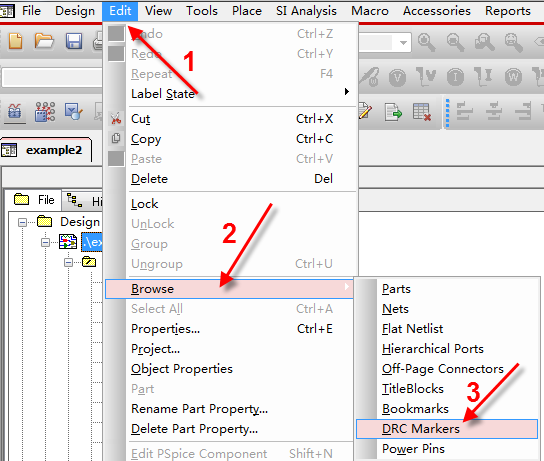

答:对原理图文件进行DRC检测以后,按照设置的DRC检测的选项,会在原理图中留下DRC的标记,对于分页的原理图来说,每一页每一页的去查看DRC的标记,比较繁琐,这里可以运用Browse功能,查看所有的DRC,操作方法如下:第一步,选中原理图的根目录,执行菜单Edit→Browse功能,然后选择DRC Marks,进行DRC标记的查看,如图3-66所示: 图3-66 浏览DRC Marks设置示意图第二步,执行命令以后,如图3-67所示,DRC ERROE显示的是错误的类型说明,DRC

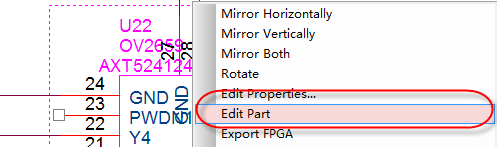

答:在使用Orcad软件输出Allegro第一方网表,出现如下错误:#1 ERROR(ORCAP-36041): Duplicate Pin Name "GND" found on Package LCM0200CE1A0_3 , U22 Pin Number 25: SCHEMATIC1, 23.Camera (129.54, 50.80). Please renumber one of these.解决的办法如下所示:第一步,找到报错的器件U22,然后选中U22这个器件,点击右键,选择Edi

答:在使用Orcad软件输出Allegro第一方网表,出现如下错误:#1 ERROR(ORCAP-36022): Pin number missing from Pin "1" of Package TEST , P3: SCHEMATIC1, 05.RC5T620-System Power (15.60, 8.00). All pins should be numbered.解决的办法如下所示:第一步,找到管脚缺失的器件P3,然后选中P3这个器件,点击右键,选择Edit Part属性

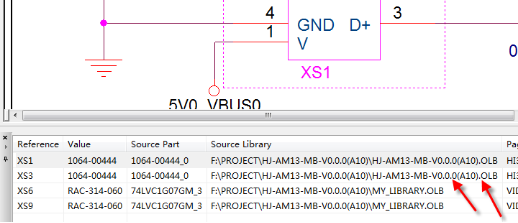

答:在使用Orcad软件输出Allegro第一方网表,出现如下错误:#1 ERROR(ORCAP-36055): Illegal character in \hj-am13-mb-v0.0.0(a10)\.解决的办法如下所示:第一步,错误的提示标明的含义的表示有非法字符, 跟这个的就是一串的非法字符,我们要做的就是把非法字符改掉;第二步,首先定位非法字符的位置,选中原理图根目录,在搜索栏输入* 非法字符*进行搜索,这个就是* hj-am13-mb-v0.0.0(a10)*,如

答:我们在运用Orcad软件进行原理图的设计完成以后,需要通过Orcad软件进行物料清单的输出、然后对BOM清单进行整理。下面我们列一下,运用Orcad软件进行BOM清单输出的步骤如下:第一步,打开原理图主目录的界面,关闭掉其它的分界面,然后选中原理图的根目录,进行下一步的操作,如图3-90所示: 图3-90 原理图根目录选中示意图第二步,选中根目录以后,执行菜单命令Tools-Bill of Materials…命令,来进行BOM清单的输出,如图3-91所示: 图3-91

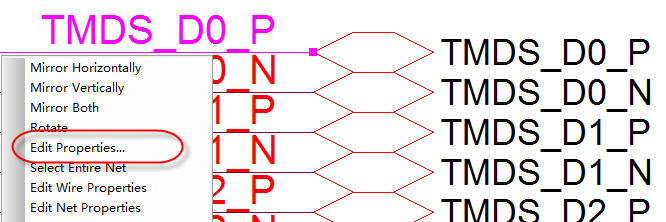

答:很多人很好奇,我们PCB文件可以添加差分信号属性,来进行走线,那原理图中可以对信号添加差分属性吗?这个当然也是可以的,下面就我们一步一步来给大家演示如何在原理图中进行差分属性的添加:第一步,首先需要在原理图中添加差分属性,选中差分信号的一根网络,然后点击鼠标右键,执行命令Edit Properties…,进行属性编辑,或者双击鼠标左键,也是一样的效果,如图3-99所示: 图3-99 信号差分属性编辑示意图第二步,进入信号属性编辑的界面,下边栏选中Schematic Ne

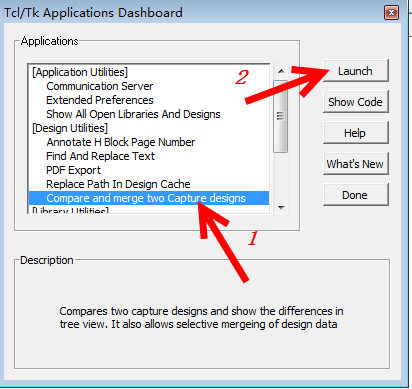

答:在电子设计中, 电路图的修改是非常频繁的,改动的多了,有时候会出现要改回去的情况,所以有时就会需要对两份原理图进行差分化的对比,操作步骤如下:第一步,首先,我们对一份原理图进行修改,修改一点点内容,做为测试之用,如图3-123与图3-124所示,方便后期查找; 图3-123 修改后的原理图示意 图3-124 修改前的原理图示意第二步,我们打开其中的任意一份原理图,选中原理图的根目录,然后执行菜单命令Accessories-Cadence TcL/Tk Utilities命

扫码关注

扫码关注