- 全部

- 默认排序

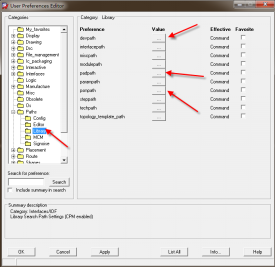

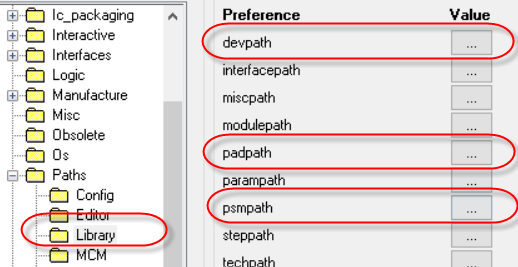

一般我们会在Allegro软件中指定这几个与封装库有关的路径。第一步,点击Allegro软件的Setup命令的最后一项User Preferences...,如图4-25所示; 图4-25 用户参数设置示意图第二步,在弹出的对话框中,选择Library中的devpath、padpath、psmpath三项设置路径,如图4-26所示; 图4-26 封装库路径指定示意图Ø Devpath:第三方网表(Other方式导出的网表)导入PC

爬电距离:沿绝缘表面测得的两个导电零部件之间或导电零部件与设备防护界面之间的最短路径。 电气间隙:在两个导电零部件之间或导电零部件与设备防护界面之间测得的最短空间距离。即在保证电气性能稳定和安全的情况下,通过空气能实现绝缘的最短距离。

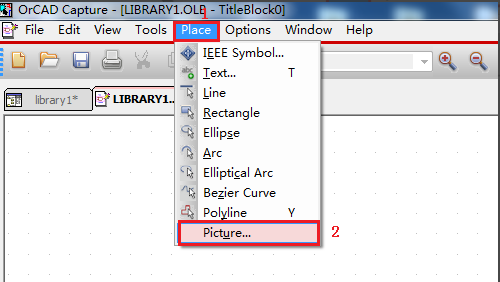

一般来说,Title Block都是调用系统本身自带的,或者是修改自带的文件,所以这里我们直接复制一个系统自带的Title Block,修改后保存在路径下,进行关联即可。 第一步,从系统自带的模板Capsym.olb中复制一个TitleBlock0到自己创建的库的路径下,选中这个元件,按Ctrl+C进行复制,然后复制到自己创建的库路径下,如图2-33所示: 图2-33 复制系统自带库示意图第二步,将复制的Title B

Allegro的封装包含的文件有dra文件、psm文件、pad文件、device文件(如果是第三方网表才需要)。打开Allegro软件,菜单栏点击Setup-User Preference,进入用户设置界面,然后点开Paths,选中下一级菜单的Library

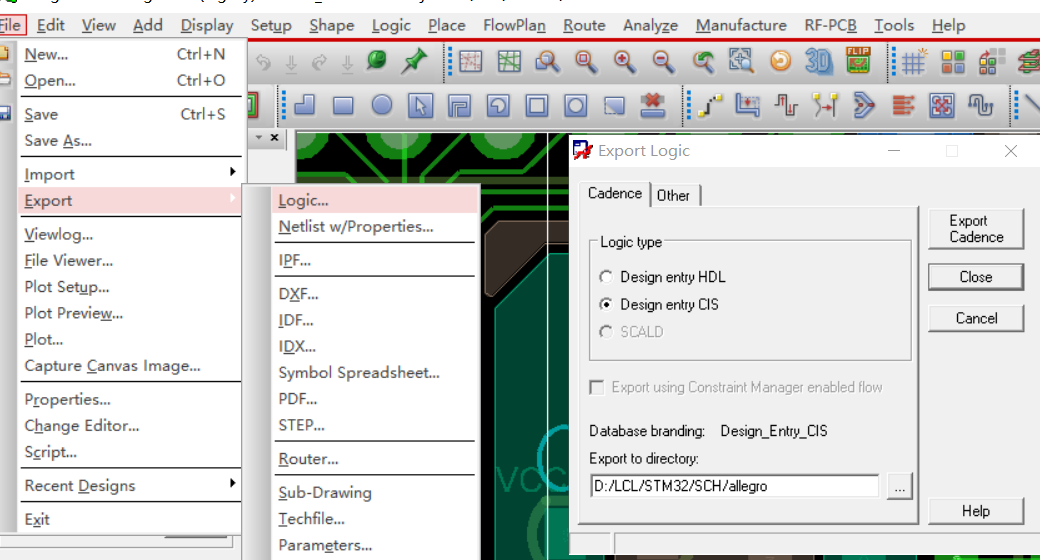

弹出export logic对话框,选择design entry CIS选项,export directory选择输出网表的路径,然后单击export directory按钮。导出完毕后,单击close按钮,关闭对话框。用orcad打开与PCB相对应的原理图,执行菜单命令tools→back annotate.....,在弹出的back annotate对话框中打开PCB editor选项卡,如图:

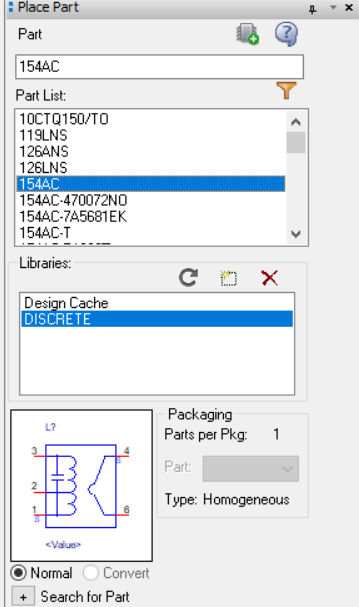

orcad绘制原理图时怎么放置器件?orcad在绘制原理图时,需要从库中把元器件放置到原理图中,放置的方法如下:第一步,执行菜单Place→Part,或者按快捷键P、或者点击右侧菜单栏放置元器件的图标,来调出放置元器件的窗口,如图3-9所示; 图3-9 放置元器件窗口示意图第二步,在放置元器件之前,需要在下面的库路径下指定封装库的路径,如图3-10所示,点击Add Library命令添加库路径; 图3-10 添加库路径示意图第三步,在库路径下选中改元器

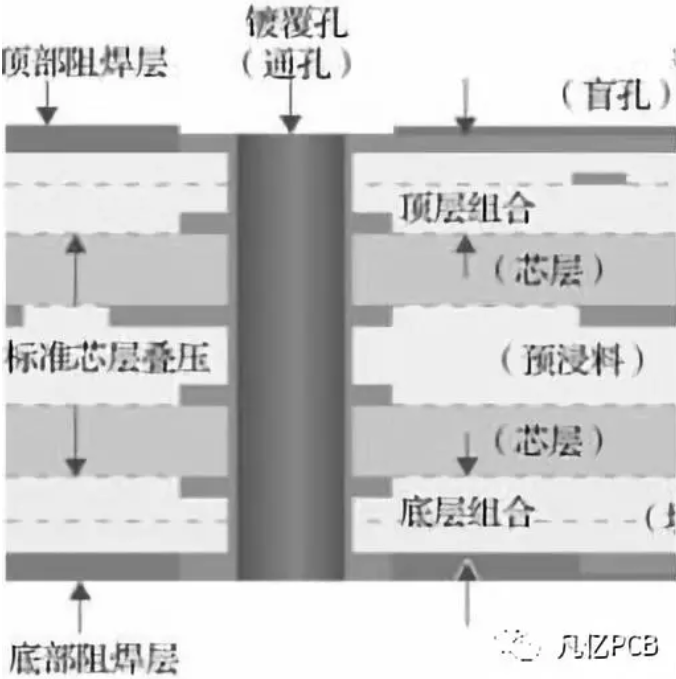

作为一个做设计的新手,在刚学PCB设计时,经常会由于电源通道处理不当(过孔数量打的不够、电源通道路径不够宽),而导致PCB设计不合格,生产出来的PCB报废。那么,我们在做PCB设计时电源通道处过孔需要怎么打哪个类型的?过孔数量要打多少个?

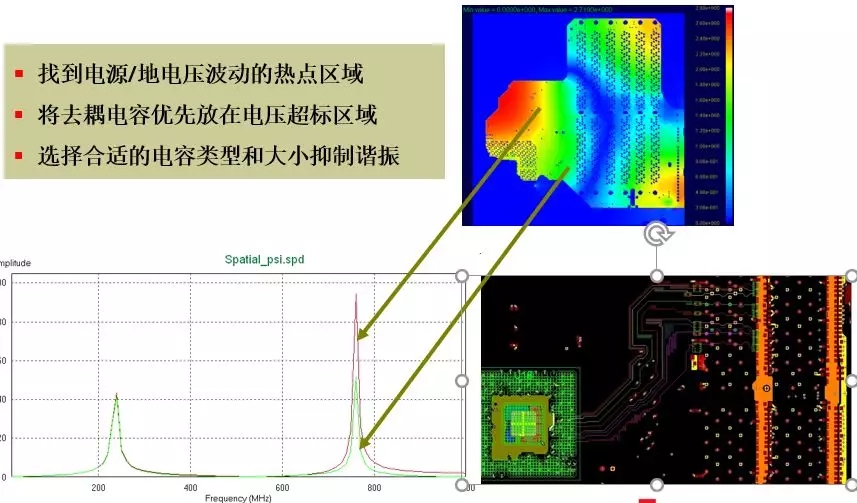

Sigrity PowerSI是IC封装和PCB设计快速准确的全波电磁场分析,作为专业的频域分析工具,为当前高速电路设计中面临的各种信号完整性(SI)、电源完整性(PI)和电磁兼容(EMI/EMC)分析提供快速准确的全波电磁场分析,并提供宽带 S参数提取以及频域仿真。PowerSI可以为IC封装和PCB设计提供快速准确的全波电磁场分析,从而解决高速电路设计中日益突出的各种PI和SI问题:如同步切换噪声(SSN)问题,电磁耦合问题,信号回流路径不连续问题,电源谐振问题,去耦电容放置不当问题以及电压

扫码关注

扫码关注