- 全部

- 默认排序

在PCB设计中,布局布线和电路性能息息相关,不正确的走线设计,尤其是信号线长度与信号频率之间不匹配,容易引发谐振干扰,进而影响电路的稳定性和可靠性,那么这是为什么?1、布线长度与信号波长的关系当信号线的长度恰好为信号波长的1/4或其整数倍时

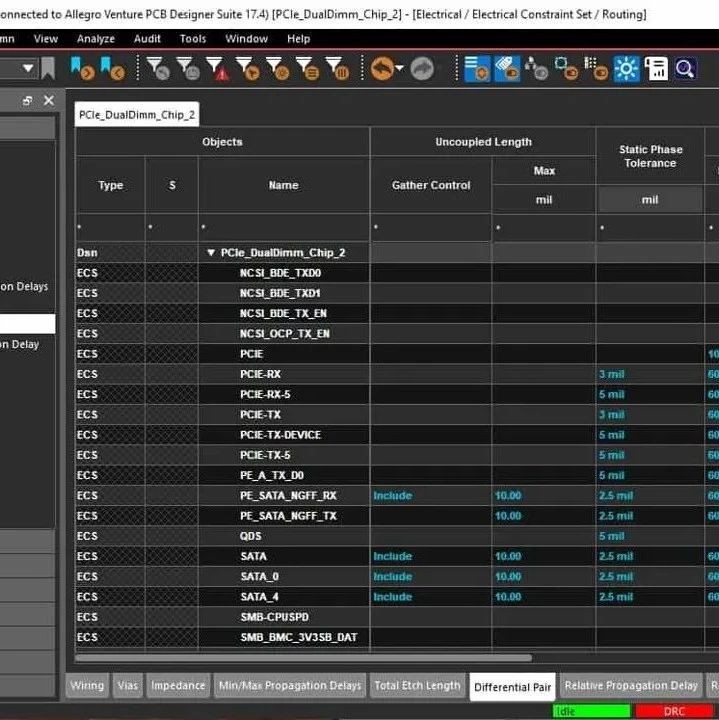

本文要点PCB 差分对的基础知识。差分对布线指南,实现更好的布线设计。高效利用 PCB 设计工具。“众人拾柴火焰高” ——资源整合通常会带来更好的结果。毕竟 “三个臭皮匠,顶个诸葛亮”,在电子领域也是如此:较之单一的走线,差分对布线更受青睐。不过,差分对布线可能没那么容易,因为它们必须遵循特定的规则

虽然工程师很少撞见关于大电流的电路设计,但如果碰见了,其走线是需要耗费许多心血,若是走线处理不当,很容易导致发热、电阻增大甚至线路烧毁等,需要采取具体措施解决!1、设置焊盘属性走线将需要处理的大电流走线设置为焊盘属性,确保线路板制造时该走线

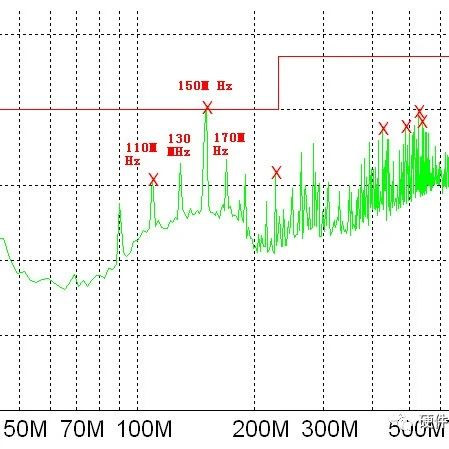

【摘要】某产品EMC辐射骚扰测试超标,通过近远场扫描配合定位分析,逐步找出骚扰源、传播路径,最终通过修改 PCB 走线切断传播路径解决此问题。1 故障现象某产品在进行 EMC 研发摸底测试时发现,整机辐射骚扰垂直方向测试超标,超标点频率为 150M Hz,同时伴有 20M Hz 间隔的脉冲

在射频(RF)电路设计中,信号间的干扰与耦合是影响电路性能的关键因素。为了最小化这种干扰,特别是在RF信号与其他信号(如中频IF信号或电源线)的交互中,十字交叉处理成为了一种重要的设计策略。1、减少干扰RF信号与IF信号或其他信号走线十字交

本文要点电气系统中电源分配网络(PDN)的各个部分都有自己的环路电感,这将增加电路结构的总阻抗。各种元件的环路电感会导致 PDN 阻抗谱中出现谐振和反谐振。设计人员应认真计算 PDN 阻抗,以便更好地了解电源轨上的纹波。由于摆放着器件、走线、过孔、焊盘、平面等,PCB 都具有复杂的几何形状。使用了多

在PCB设计中,我们总会碰见各种设计策略,其中3W规则可减少走线间串扰、提高信号传输稳定性,提升电路板的可靠性,是重要布线原则之一,被广泛应用。那么它适合哪些场景?1、高速信号线的长距离走线时钟线:时钟信号对时序要求高,3W规则能有效减少时

扫码关注

扫码关注