- 全部

- 默认排序

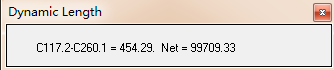

答:使用Allegro走线的时候,可以动态地显露走线的长度信息,具体操作的步骤如下所示:首先,点击Setup-User Preferences,在弹出的User Preferences Editor选项卡中勾选

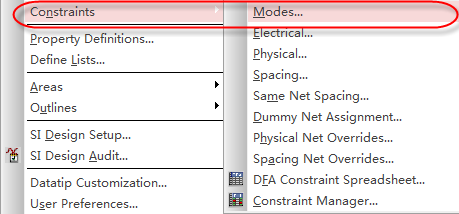

答:PCB设计中有一些信号组需要进行等长处理,以保证组内信号时序要求。第一步,点击Setup-Constraints-Constraint Manager选项,调出规则管理器,如图6-269所示;

答:我们在PCB设计中经常听到需要漏铜处理,或者是这里我要铺白油,这在PCB板上非常好理解,生产出来黄色的就是铜,白色一块的就是白油。我们这里讲解一下,在Allegro软件中如何处理,具体操作如下所示:

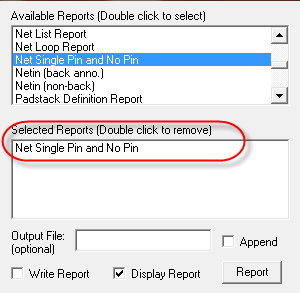

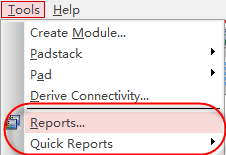

答:每次进行PCB设计时,在设计之前,都会对项目进行单端网络检查。首先,点击Tools-Reports选项,如图6-277所示;

答:使用Allegro进行设计时,焊盘间飞线有2种显示方式,一种是焊盘到焊盘,一种是按最短距离显示,按最短距离显示,可在走线的时候让飞线指示到离另一连接点最近的位置。

答:我们在PCB设计时,都会进行规则的设置,然后使用规则来约束设计,进行DRC的监测。我们这里讲解一下,soldemask也就是阻焊到其它元素的间距应该如何设置呢,具体操作的方法如下所示:

答:我们在进行PCB设计的时候,对于差分信号换层,都是双击进行打孔,但是双击打孔的间距是系统默认的,有时候会导致过孔间距太近,影响信号的质量,如图6-283所示,我们是否可以手动去控制差分过孔之间的间距呢,当让是可以的,我们这里讲解一下具体的处理方法,如下所示:

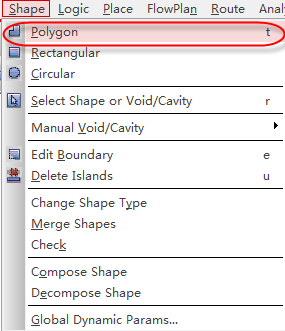

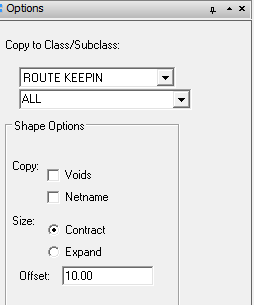

答:我们在PCB设计中,经常会遇到一些异形的板框,比如做FPC设计、LED灯板设计,如图6-286所示,我们PCB走线都是按45度走线,直接去走,很能走的规范,到板边的间距是一致的,这里讲解一下,如何设置一下,让走线沿着PCB板框按一定的规律进行布线,具体操作如下所示:

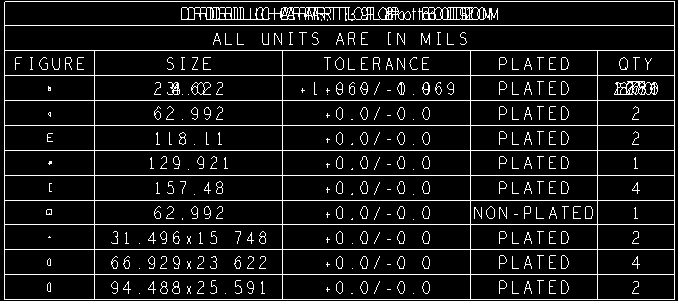

答:添加钻孔表格时,有时候系统自动生成的表格数据是重叠的,如图6-291示。

答:在PCB设计完成后,需要导出器件物料BOM表单,以方便公司采购人员采购项目内使用到的电子元器件。可以在原理图中导出BOM,也可以在PCB中导出BOM,在PCB中导出BOM可按以下步骤进行:

扫码关注

扫码关注