- 全部

- 默认排序

我们在Allegro软件中,我们在铺铜的时候,需要事先对铜皮与焊盘的连接方式进行设置,有全连接、十字连接等多种连接方式,我们需要对全局的铜皮的连接方式进行一个设置,具体的操作步骤如下所示:

一、4层 PADS 路由器产品设计视频教程课程目录 01、视频内容介绍及设计资料准备 02、原理图分析及电源二叉树分析 03、原理图导入 PCB 04、PCB 板框导入及布局布线区域设置 05、PCB 设计默认设置及颜色方案设置

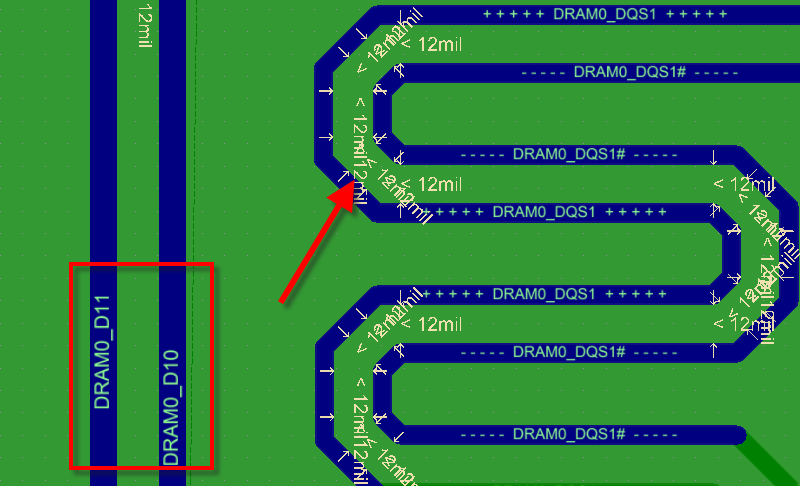

我们在用allegro进行PCB设计完成以后,都需要对一组传输的总线进行时序等长,在做时序等长的时候,分为绝对传输延迟与相对传输延迟。绝对传输延迟,顾名思义,信号传输在PCB设计中都是有一个走线的长度,我们通过设置这个信号线传输的最大值与最小值,来实现等长的方法,就称之为绝对传输延迟。

在进行原理图设计时,经常需要对视图进行缩小放大等操作。PADS Logic的【设置】菜单提供了可以用于视图操作的基本命令,可以使用这些命令来进行缩放等操作,也可以使用鼠标进行相应的操作。

下面为大家总结了39条Allegro操作指令,涉及鼠标设定、Text path设置、Stroke的使用等,无论是新手还是老司机,这些常用操作指令都必须熟记在心!

一般我们会在Allegro软件中指定这几个与封装库有关的路径。第一步,点击Allegro软件的Setup命令的最后一项User Preferences...,如图4-25所示; 图4-25 用户参数设置示意图第二步,在弹出的对话框中,选择Library中的devpath、padpath、psmpath三项设置路径,如图4-26所示; 图4-26 封装库路径指定示意图Ø Devpath:第三方网表(Other方式导出的网表)导入PC

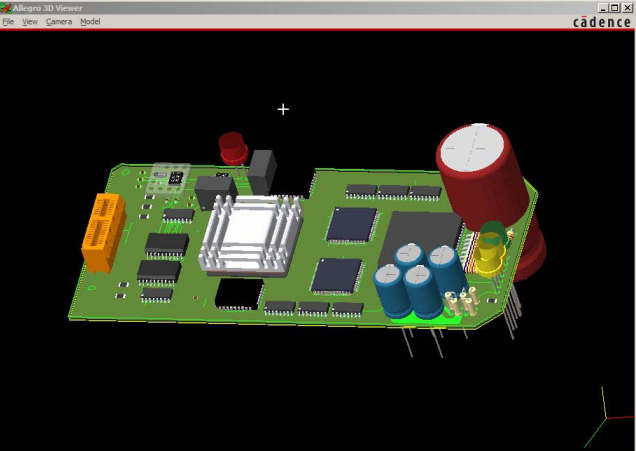

分别在上图示位置选择需要显示3d效果的器件进行匹配,对各参数进行设置以达到理想效果。设置好后点击Save进行保存。然后可点击Report进行查看匹配结果

为了尽量减小单板设计的串扰问题,PCB设计完成之后一般要对线间距3W规则进行一次规则检查。一般的处理方法是直接设置线与线的间距规则,但是这种方法的一个弊端是差分线间距(间距设置大小不满足3W规则的设置)也会DRC报错,产生很多DRC报告,难以分辨

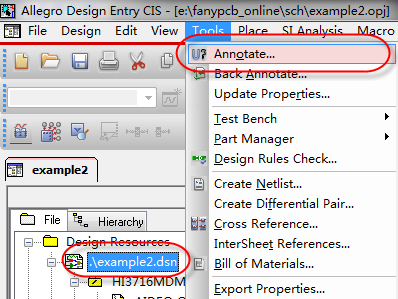

第一步,选中整个原理图的根目录,然后执行菜单Tools-Annotate,如图3-56所示,进行原理图选项的编辑; 图3-56 原理图进行编译示意图第二步,然后对器件的位号进行复位的操作。在弹出的原理图编译界面中,如图3-57所示,在Action选项中,现将原理图本身已经存在的位号全部复位,点击Reset Part References to “?”,则全部的位号则变成的问号,可参照图3-57所示。 图3-57 原理图编位号复位设置示意图第三步,把所有

扫码关注

扫码关注