- 全部

- 默认排序

Altium极坐标的应用

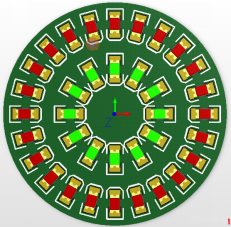

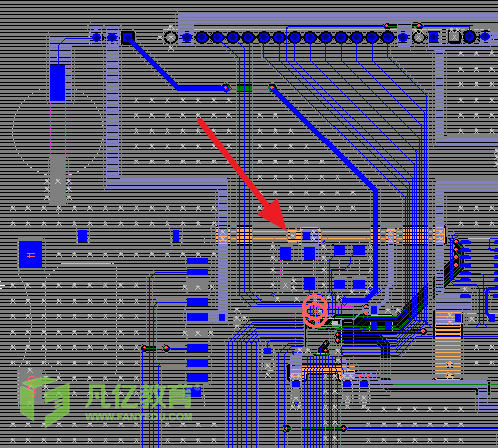

如图13,在PCB设计行业当中,特别是LED灯板行业,我们需要对LED灯珠进行圆弧等间距进行排列,如果我们每个器件都以计算清楚其坐标再进行放置的话会非常繁琐,那么我们有什么好的办法没有呢,Altium提供了一个非常简单的解决方案—极坐标

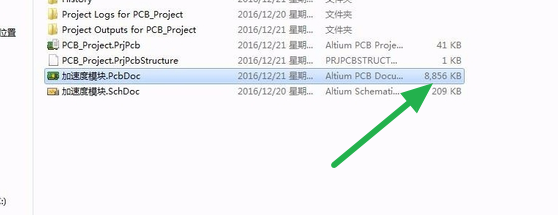

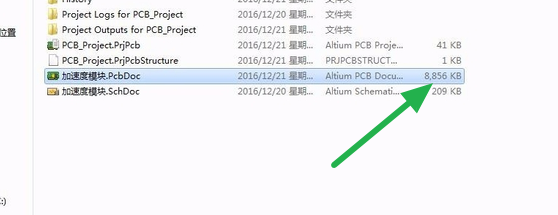

当我们设计完PCB时,去进行保存的时候,在文件夹里面看到此刻的PCB文件非常大,这是为什么呢?是不是里面还有文件什么的?其实出现这个现象最大的原因就是在PCB工程加入了中文字库。那么遇到这种情况我们如何去解决?

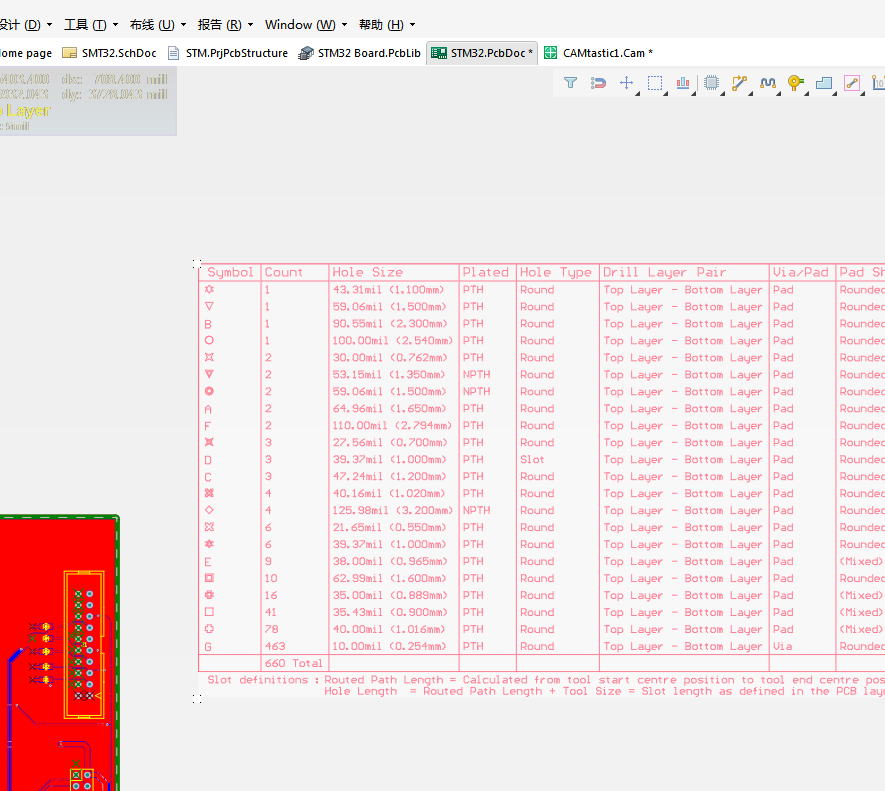

AD20在导出Gerber的时候,Dirll Drawing层的“.legend”出现Legend is not interpreted until output (即使在最终的输出也没有变化)。导致导出Gerber时并没有对应的显示标识。这个问题在高版本中最常见,通常是在放置钻孔表时,对应的选项没有进行设置。

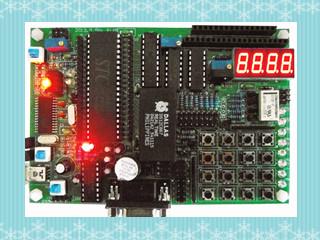

单片机学习是有技巧的

在单片机应用开发中,代码的使用效率问题、单片机抗干扰性和可靠性等问题仍困扰着工程师。为帮助工程师解决单片机设计上的难题,信盈达小编纳出单片机开发中应掌握的几个基本技巧。一、如何提高C语言编程代码的效率用C语言进行单片机程序设计是单片机开发与应用的必然趋势。如果使用C编程时,要达到最高的效率,最好熟悉所使用的C编译器。先试验一下每条C语言编译以后对应的汇编语言的语句行数,这样就可以很明确的知道效率。在今后编程的时候,使用编译效率最高的语句。各家的C编译器都会有一定的差异,故编译效率也会有所不同,优

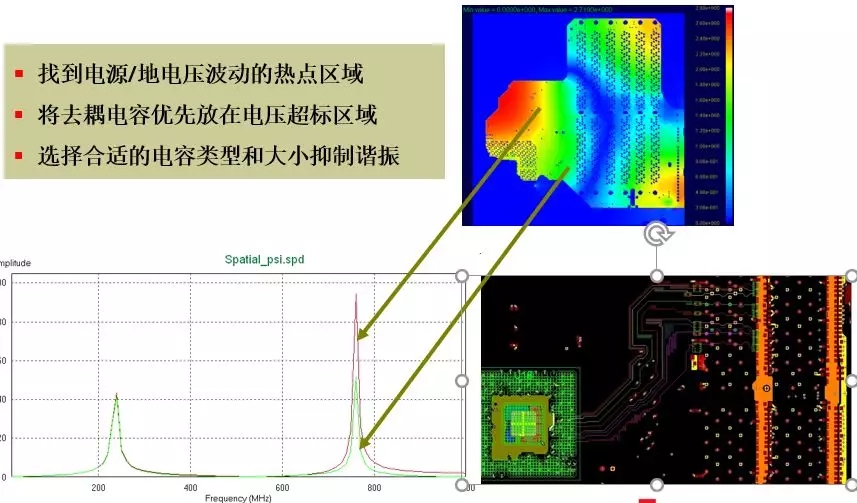

Sigrity PowerSI是IC封装和PCB设计快速准确的全波电磁场分析,作为专业的频域分析工具,为当前高速电路设计中面临的各种信号完整性(SI)、电源完整性(PI)和电磁兼容(EMI/EMC)分析提供快速准确的全波电磁场分析,并提供宽带 S参数提取以及频域仿真。PowerSI可以为IC封装和PCB设计提供快速准确的全波电磁场分析,从而解决高速电路设计中日益突出的各种PI和SI问题:如同步切换噪声(SSN)问题,电磁耦合问题,信号回流路径不连续问题,电源谐振问题,去耦电容放置不当问题以及电压

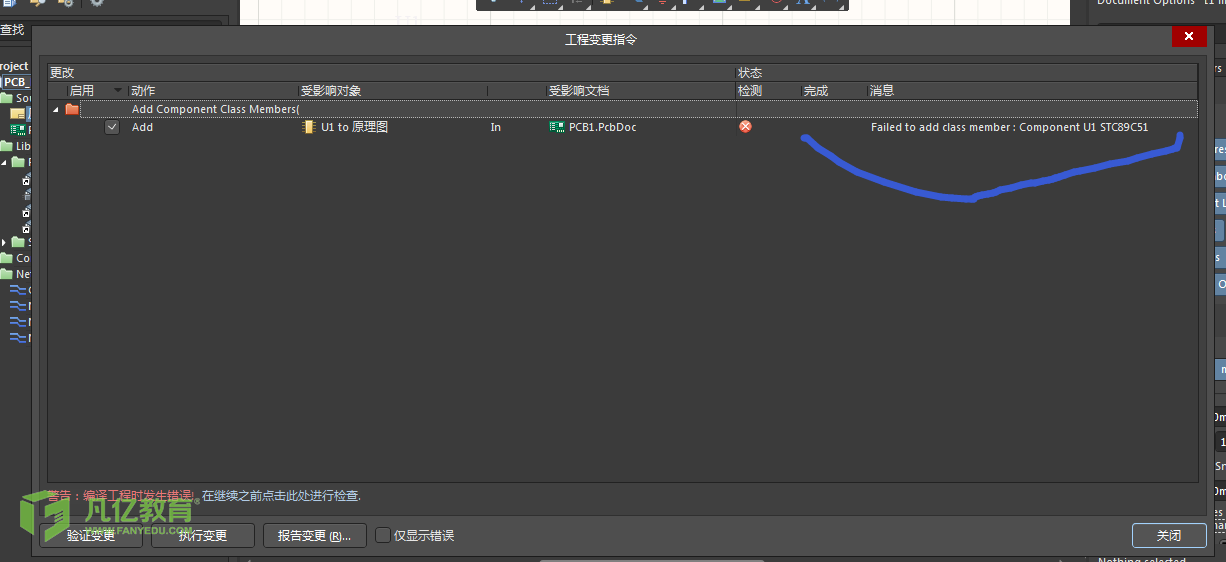

我们在进行到原理图导入到PCB中会出现各种各样的报错,之前的几种常见的报错我们也已经写过其对应的教程了,那么我们今天来看下出现“Failed to add class member”的这一项错误的解决办法。

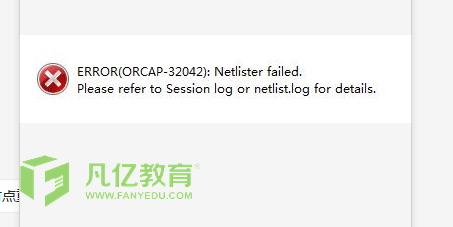

我们在进行原理图设计的时候,完成之后就需要去进行网表的导出,然后在pcb中去进行设计。有很多学员在原理图导出网表的这一操作中会出现各种各样的报错,那么今天我们就来看看最常见的一项导出网表的报错的解决办法,即”Netlister failed”的报错。

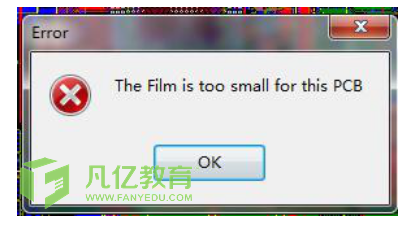

我们在PCB设计完成,并且检查完成之后,就会进行文件的输出。其中最重要的一项文件的输出就是Gerber文件的输出,也就是我们俗称的光绘文件的输出。那么我们在输出Gerber的时候,有时候会出现“The film is small for....”的报错,碰到这种问题,我们应该如何去解决呢?

当我们设计完PCB时,然后再进行保存,在文件夹里面看到PCB文件非常大,这是为什么呢?是不是里面还有文件什么的?其实出现这个现象最大的原因就是在PCB工程加入了中文字库。那么我们的解决办法又是什么呢?

扫码关注

扫码关注