- 全部

- 默认排序

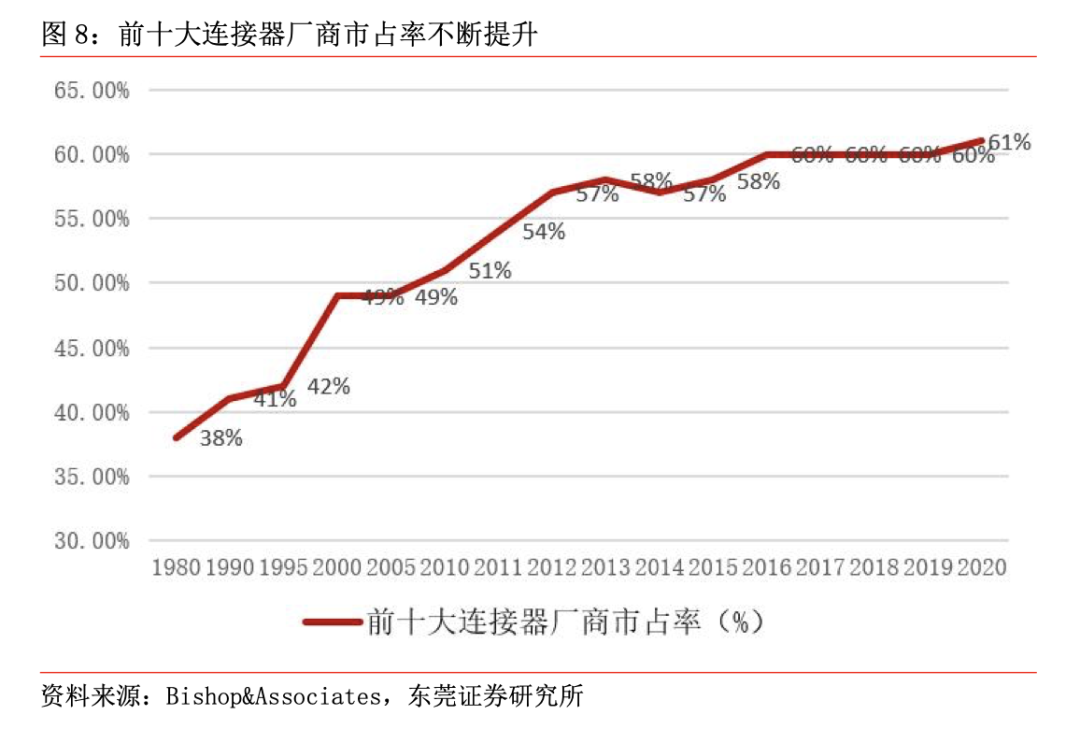

随着应用领域不断扩展,连接器产业逐渐发展成为产品种类齐全、品种规格丰富、专业方向细分、行业特征明显、标准体系规范、系列化及专业化的行业。连接器行业是充分竞争的行业,行业集中度不断提升连接器行业具有市场全球化和分工专业化的特征,行业竞争较为充

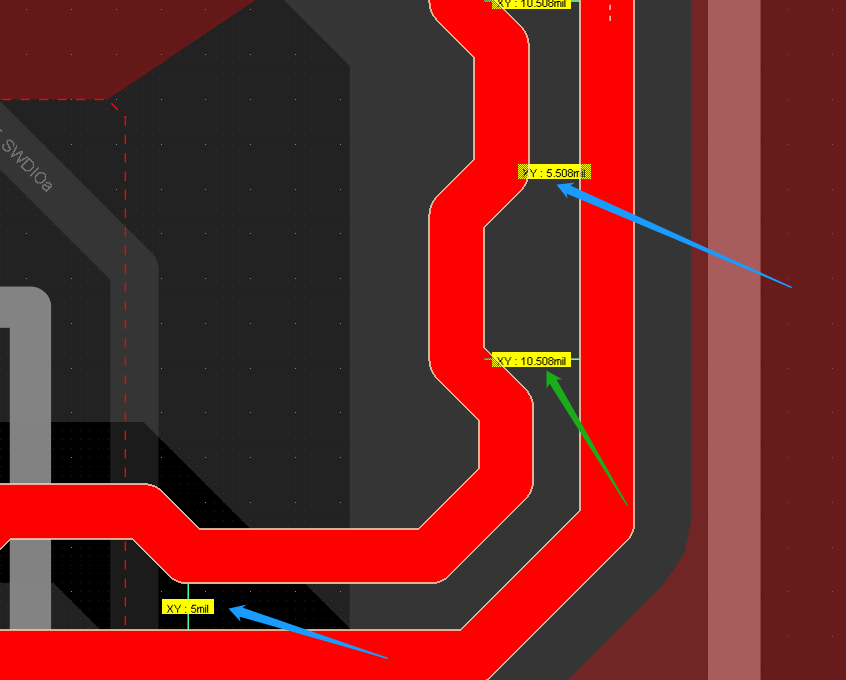

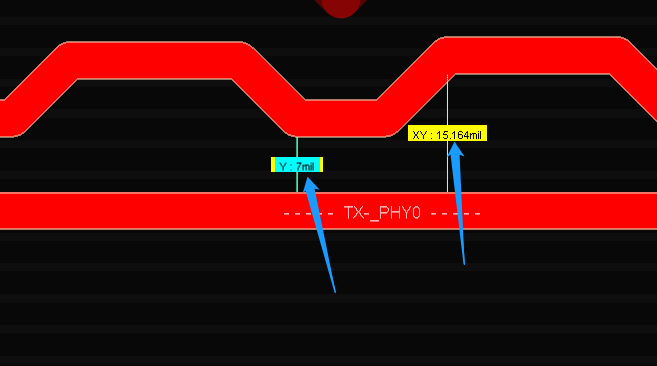

差分走线不满足差分间距要求,锯齿状等长也不能超过线距的两倍2.滤波电容和EAD器件靠近管脚放置3.输出打孔要打在最后一个滤波电容的后面4.焊盘出现不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊5.此处走线不满足载流6.VBAT的滤

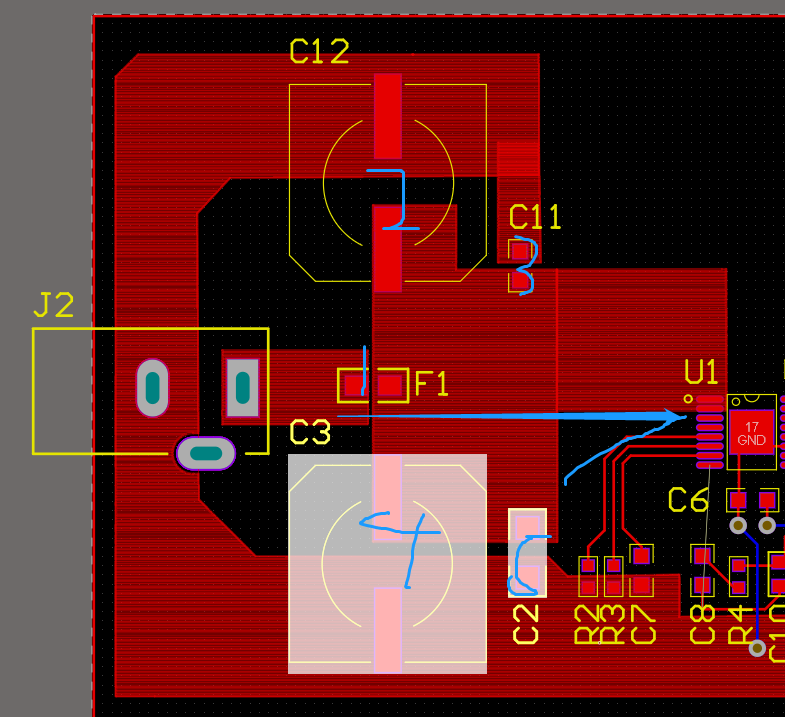

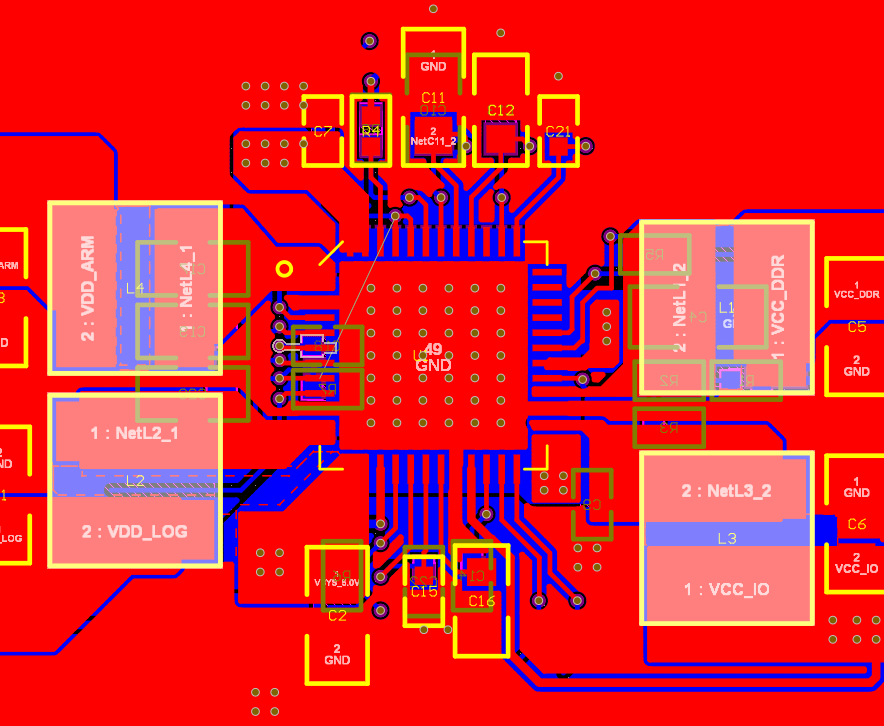

器件摆放尽量呈一字型布局,滤波电容按照先大后小的顺序摆放2.电源输出尽量铺铜处理,满足载流3.电容放在住干道上面4.焊盘出现不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊5.芯片才用单点接地,就是输入和输出的地要连接在芯片中间进行

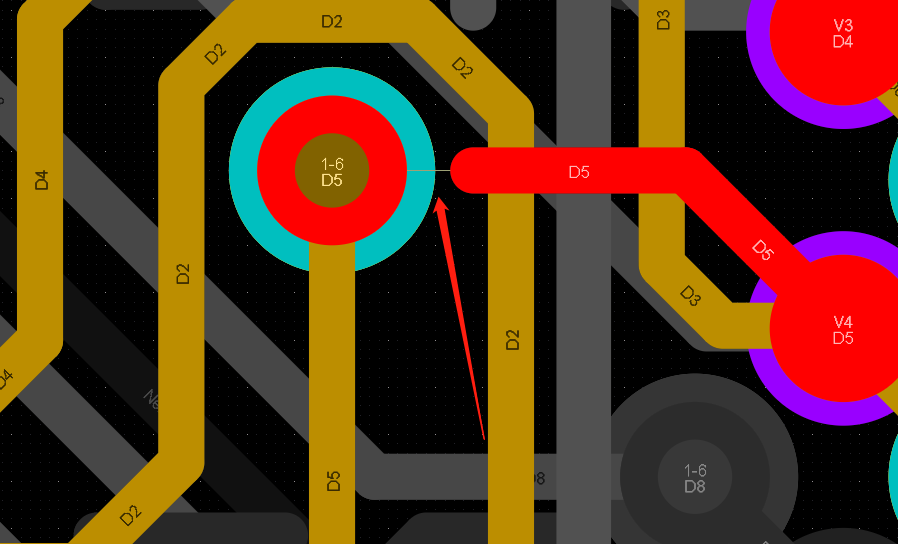

存在开路报错2.过孔尽量不要打在电阻中间3.走线尽量不要有直角,建议钝角4.时钟信号等长不符合规范5.地址线等长存在报错,以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https

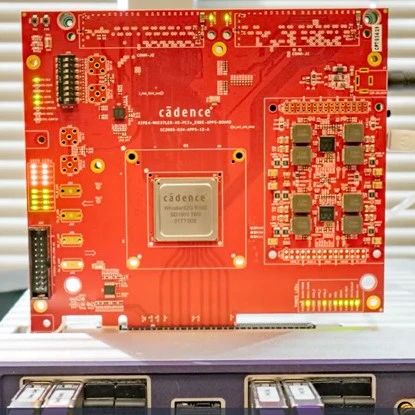

从规范草案到被 PCI-SIG 列入集成商的合规目录需要经历数年。初步 PCIe 5.0 规范于 2017 年 6 月公布,最终规范于 2019 年 5 月发布,第一次正式合规研讨会于 2022 年 4 月举行。如此漫长的过程说明了所开发的产品以及支持这些产品所需的生态系统非常复杂。Cadence

差分线等长不符合规范,锯齿状等长不能超过线距的两倍2.差分走线尽量耦合3.电源线宽尽量保持一致,满足载流4.中间的焊盘可以多打过孔5.存在无网络过孔以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接

电感底部不能放置器件以及走线,重新布局下,可以将电容塞到芯片底部:这种孤铜都去除下:走线注意规范不要出现锐角以及直角:DCDC输出主干道的铜皮尽量加宽一点:放置完铜皮挖空之后需要重新灌铜才能自动避让挖空区域:反馈信号走线又是直角:铺铜也注意

端子压接标准及检验规范要求是电子电路中至关重要的一环,广泛应用于电气、通信、配电、自动化、航空航天等领域。为维护设备的正常运行和人身安全,制定端子压接标准及检验规范要求显得尤为重要。在这篇文章中,我们将介绍端子压接标准及检验规范要求的主要内

一个优秀的工程师设计的产品一定是既满足设计需求又满足生产工艺的,某个方面有瑕疵都不能算是一次完美的产品设计。规范产品的电路设计,工艺设计,PCB设计的相关工艺参数,使得生产出来的实物产品满足可生产性、可测试性、可维修性等的技术规范要求,在产

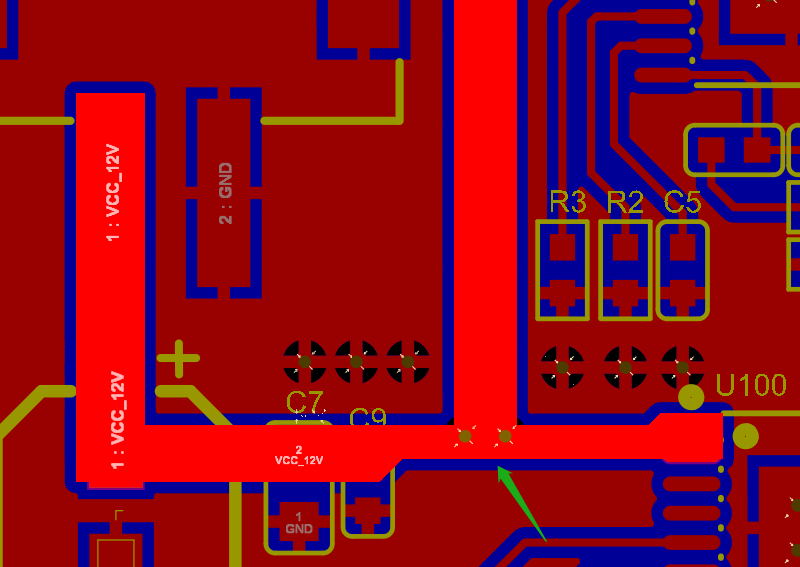

12V电源输出铜皮加粗处理,满足对应的载流大小:电感当前层的内部挖空处理:个别配置电阻电容对齐处理:反馈信号是连接在输出的电容的最后一个管脚上,连接有问题:注意铺铜不要存在直角以及这种尖角,尽量钝角处理:焊盘出线规范,要从两长边拉出再去拐线

扫码关注

扫码关注