- 全部

- 默认排序

★ 掌握PCB设计常用的设计技巧及熟悉PCB设计的整体流程★交互式模块化快速布局★BGA扇孔出线的方式、BGA的快速拉线方法★菊花链拓扑结构的认识及设置★掌握蛇形等长走线,掌握★了解常见EMC的PCB处理方法3W规则的应用

1. 掌握PCB设计常用的设计技巧及熟悉PCB设计的整体流程 2. 掌握DDR3设计的知识要点 3.掌握3W原则的PCB设计 . 了解菊花链拓扑结构及设计规则 . 掌握蛇形等长走线

在规则里面这么多拓扑结构,很多时候我们只需要使用第一个shortest规则就可以,在ad中这几个出线规则其实并不需要我们去太多的纠结,因为对于器件而言不同的器件我们使用的布局方式又是不一样的,比如DDR什么时候用T点,什么时候用菊花链 ,什么时候用fly-By,等等这些,都是需要按照我们的行业规范进行布局和布线。

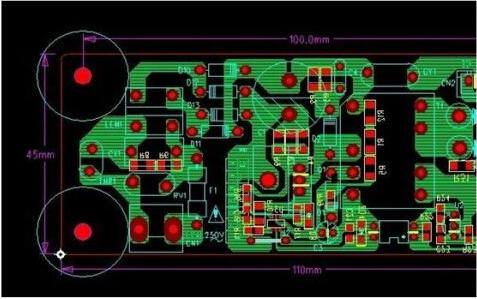

通过这一课程我能学到什么1)Allegro 4层板布局布线技巧2)Allegro 4层板TI主控设计3)Allegro软件基本操作技巧4)菊花链拓扑设计5)凡亿高手实战经验这个是一个非常经典的4层allegro达芬奇核心板设计,基于TI的主控DM642,全程讲解通过Allegro软件来设计一个4层的达芬奇开发板的PCB设计实战过程,从前期的原理图导入,导后期输出生产文件(GERBER )的全过程。

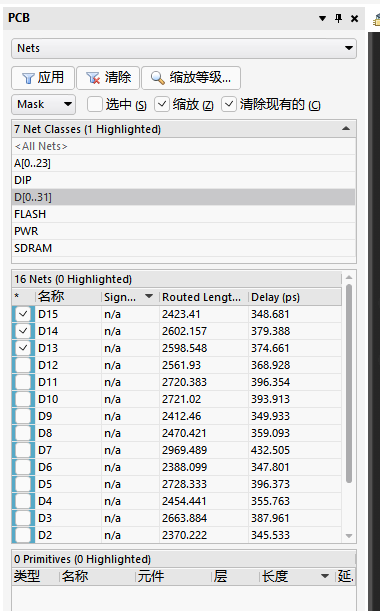

一、PADS8层DDR3 Fly-by拓扑结构视频课程详情本pads视频课程基于飞思卡尔 i.MX6 处理器的 8层PCB设计,重点介绍 DDR3 内存的设计思路,一共四颗 DDR3,采用菊花链(Fly-By)的拓扑结构。讲解了 DDR3 设计的信号 class分组,信号的同组同层布线、信号时序等长及常用规则注意事项、信号完整性、电源完整性的规划等。

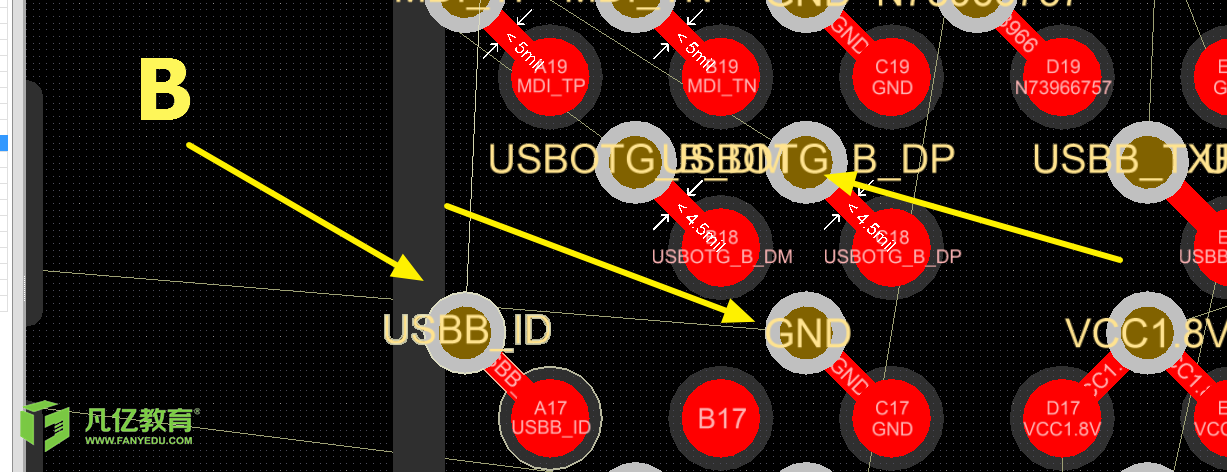

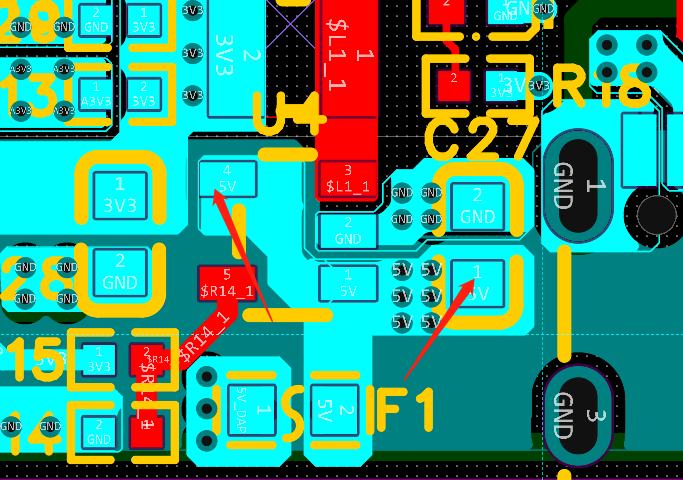

1.电源输入的滤波电容应该靠近输入管脚放置2.【问题分析】:注意等长线之间需要满足3W规则3.【问题分析】:USB需要进行等内等长处理,等长误差为5mil4.此处是用菊花链的方式进行等长,建议使用创建焊盘对组进行分段等长(U1-U2,U2-

USB的差分信号需要进行对内等长,等长误差为5mil2.晶振走线需要走类差分处理3.此处是用菊花链的方式进行等长,建议使用创建焊盘对组进行分段等长(U1-U2,U2-FPC1)4.电源输入的滤波电容应该靠近输入管脚(4脚)放置5.电源输出部

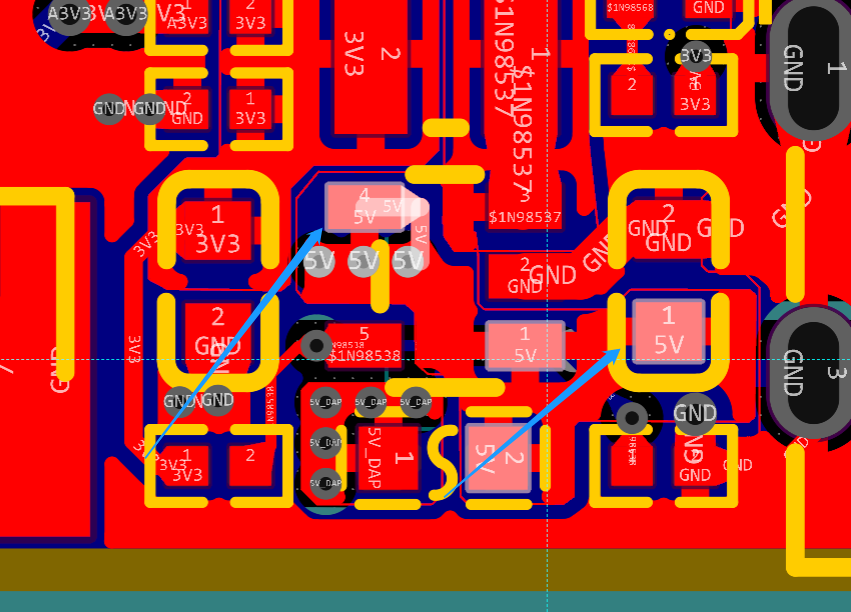

1.电源输入的滤波电容应该靠近输入管脚(4脚)放置2.差分走线要尽量耦合出线,满足差分间距规则3.此处是用菊花链的方式进行等长,建议使用创建焊盘对组进行分段等长(U1-U2,U2-FPC1)4.器件摆放尽量对齐处理5.pcb上存在开路现象6

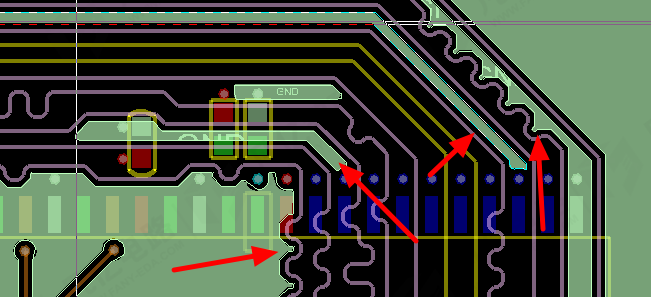

存在多处尖岬铜皮和孤岛铜。2. 多处器件摆放干涉,如生产会造成两个器件重叠无法焊接。3.部分管脚存在开路。4.数据线分组错误,少了LDQM和HDQM5.地址线分组错误,缺少部分信号;以设计规范为准。以上评审报告来源于凡亿教育90天高速PCB

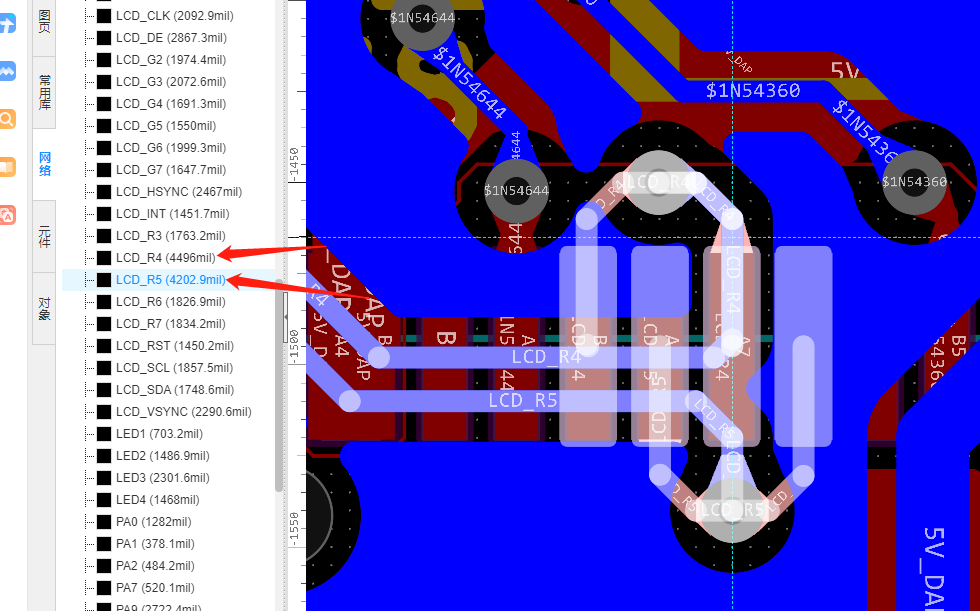

数据线分组错误2.地址线分组错误3.焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊4.走菊花链的结构,等长应该是BGA到SDRAM,然后再从SDRAM到FLASH5.相邻焊盘是同网络的,不能直接相连,需要先连接焊盘之后在进

全站最新内容推荐

- 1加码技术,打破困境,PSPice电路仿真助你解锁职场新高度!

- 2简谈稳压二极管和普通二极管的区别

- 3贴片元件如何拆卸及焊接?

- 4盘点电子工程师必须了解的21个电路

- 5英伟达GB300芯片受阻,存在过热问题

- 6WARELEO李增原创H04课程大纲的安排课程中内容及工具及课程的重点学习办法的讲解

- 7WARELEO李增原创H03根据自己的关注知识点和所需要的知识来选择需要的图书包邮递

- 8WARELEO李增原创H02理工男生李老师的介绍从51单片机驱动到FPGA到仿真设计之路

- 9WARELEO李增原创H01信号电源完整性设计与HFSS射频天线设计仿真验证研修课程主题

- 10WARELEO李增:反射仿真的信号观察办法及时域串扰的仿真设置及观察技巧

扫码关注

扫码关注