- 全部

- 默认排序

Allegro的全称是Cadence Allegro PCB Designer,是Cadence公司推出的一套完整的、高性能印制电路板设计套件。它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段进行定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。Allegro印制电路板设计提高了PCB设计效率和缩短设计周期,让您的产品尽快进入量产。Allegro是我们目前高速PCB设计中使用最多的工具。

Allegro的全称是Cadence Allegro PCB Designer,是Cadence公司推出的一个完整的、高性能印制电路板设计套件。通过顶尖的技术,它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。Allegro印制电路板设计提高了PCB设计效率和缩短设计周期,让您的产品尽快进入量产(目前高速PCB设计用的最多工具,就是Allegro)。

Allegro的全称是Cadence Allegro PCB Designer,是Cadence公司推出的一个完整的、高性能印制电路板设计套件。通过顶尖的技术,它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。Allegro印制电路板设计提高了PCB设计效率和缩短设计周期,让您的产品尽快进入量产(目前高速PCB设计用的最多工具,就是Allegro)。

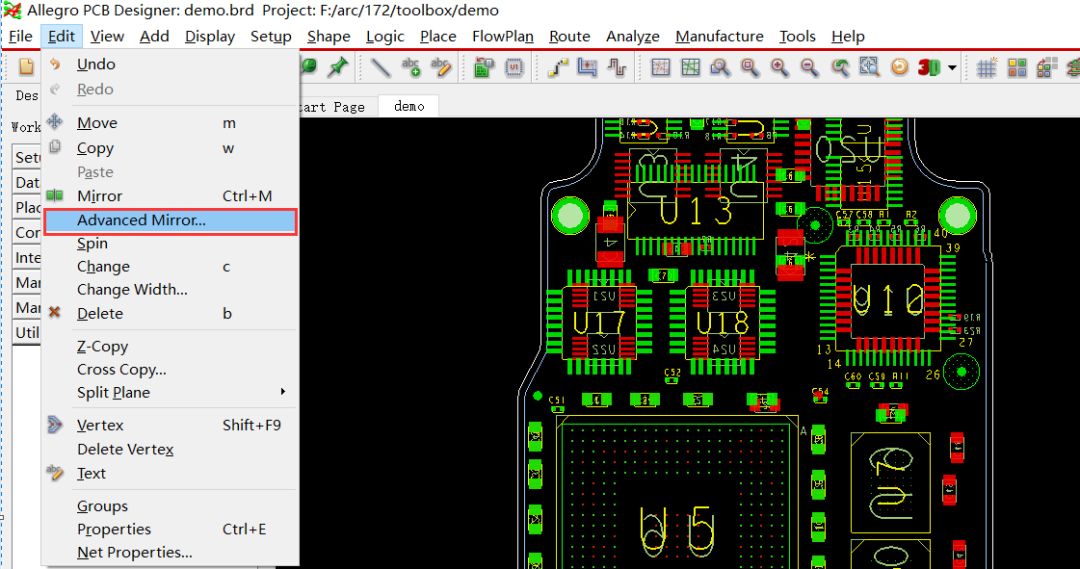

Allegro PCB Designer是一个完整的、高性能印制电路板设计套件。通过顶尖的技术,它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。 在这个专题中,我们将介绍在该套件下的一个Toolbox选项组件下的Advanced Mirror高级镜像功能。

在设计PCB的时候,为了满足各项设计要求的原因,我们需要设置很多的约束规则,然后设计完成之后,去进行DRC检查。DRC检查就是检查我们的PCB设计是否满足所设置的规则,常见的DRC检查有开路,短路,间距等等规则约束。

物理约束规则介绍

物理规则包括设置线宽和指定过孔库等的属性规则,在设置规则之前,需要把层叠等参数设置好。默认的为default规则。Default规则是指铺铜的单线50Ω阻抗的信号线规则

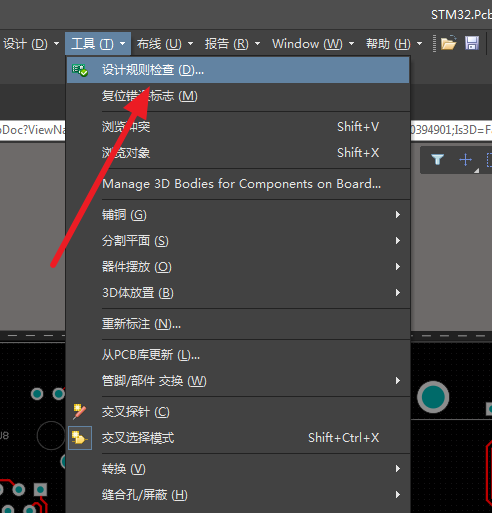

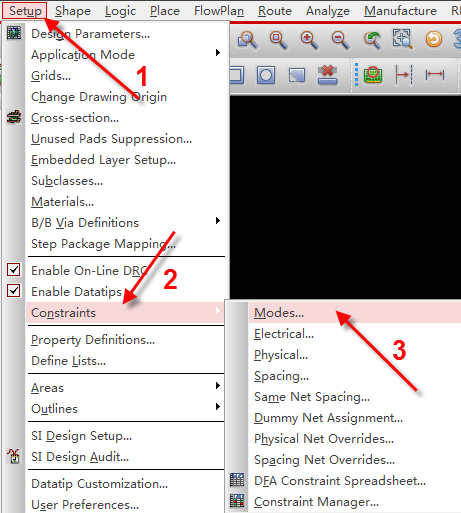

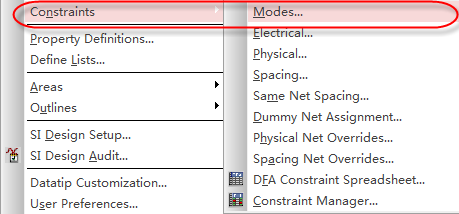

答:我们在前面的问答中讲述了走线的阻抗线宽以及不同的元素之间的间距规则之间的限定,但是,在Allegro软件中各个的约束规则需要在约束规则管理模式开启的情况下,才能起作用的。执行菜单命令Setup-Constrains,在下拉菜单中选择Modes,进行各个约束规则管理模式的选取,如图5-79所示:

答:我们在PCB设计时,都会进行规则的设置,然后使用规则来约束设计,进行DRC的监测。我们这里讲解一下,soldemask也就是阻焊到其它元素的间距应该如何设置呢,具体操作的方法如下所示:

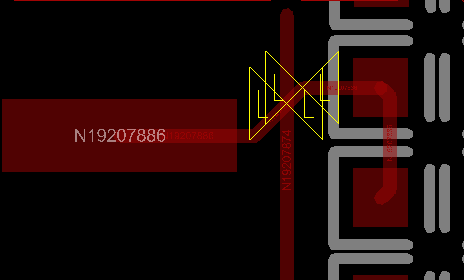

答:使用Allegro软件进行PCB设计,一般会使用约束规则辅助设计,当设计时有对象违反了设置的约束规则,软件会以DRC标记的形式提醒设计者。

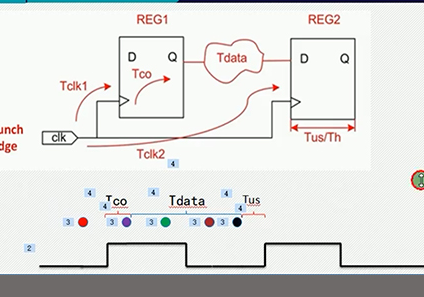

众所周知,芯片行业存在一个定理,那就是摩尔定律,主要内容是集成电路上可容纳的晶体管数目在大约每18个月便会增加一倍。掌握FPGA/IC工程师需要的核心技能,来凡亿教育!>>《基于VIVADO平台的FPGA时序约束教程》随着技术的提升和原材料

扫码关注

扫码关注