- 全部

- 默认排序

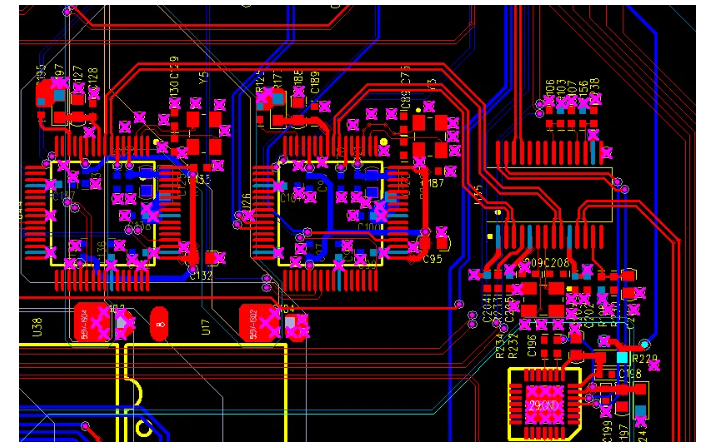

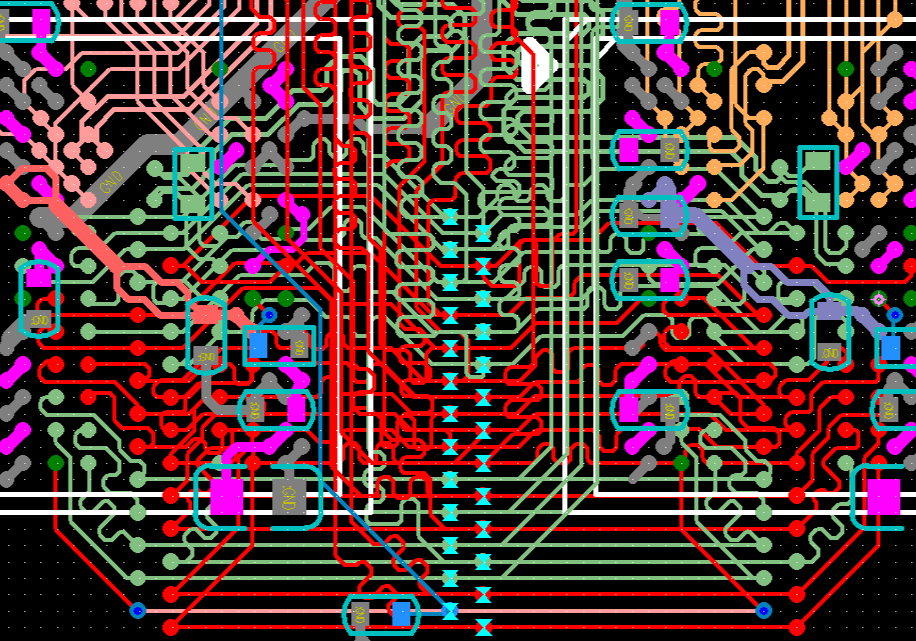

PCB设计,遇到差分线,需要做等长设计时,该怎么操作呢?在做走线等长设计的时候,我一般都是采用让走线进入蛇形走线模式,然后走出蛇形线来快速完成等长设计。

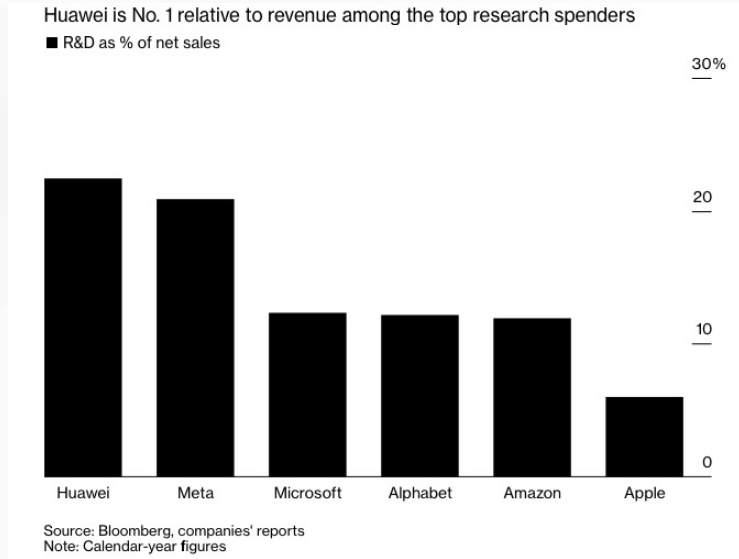

据彭博社报道称,很少有公司像华为一样,在面对美国制裁仍然要将更多的收入投入到研发当中,对于华为来说,开发新技术试管挫败美国对其造成影响的贸易和投资制裁。新手入门,学习HDMI+DDR+差分等长来>>《华为海思HI3716电视主板PCB设计实

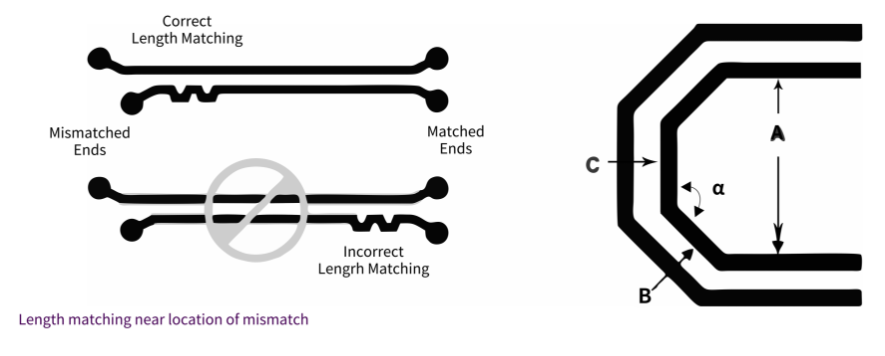

Altium Designer 21在之前版本的基础上对蛇形等长功能进行了优化,大大提高了设计的效率和规范性,具体改进可以参考以下说明。1.1新增两种等长样式 在之前的版本设计当中,等长设计时只有单一的U形等长。Altium Designe

一个学习信号完整性仿真的layout工程师做layout工程师都知道差分等长规则的设置,但可能有的不了解Xnet的设置,因为在我们平常的layout中发现,其实在电阻或者电容的另一端的走线是特别短的,如果要求没那么严格,也就不需要设置Xne

PADS虚拟过孔

虚拟过孔一般在有拓扑结构的设计时被使用,比如T形拓扑,虚拟过孔可以当作一个虚拟的管脚,满足了拓扑结构设计时等长的需要。鼠标右键选择“选择网络”,鼠标左键选择需要添加虚拟过孔的对应的网络(可选择焊盘或者布线上),单击鼠标右键选择“添加虚拟过孔

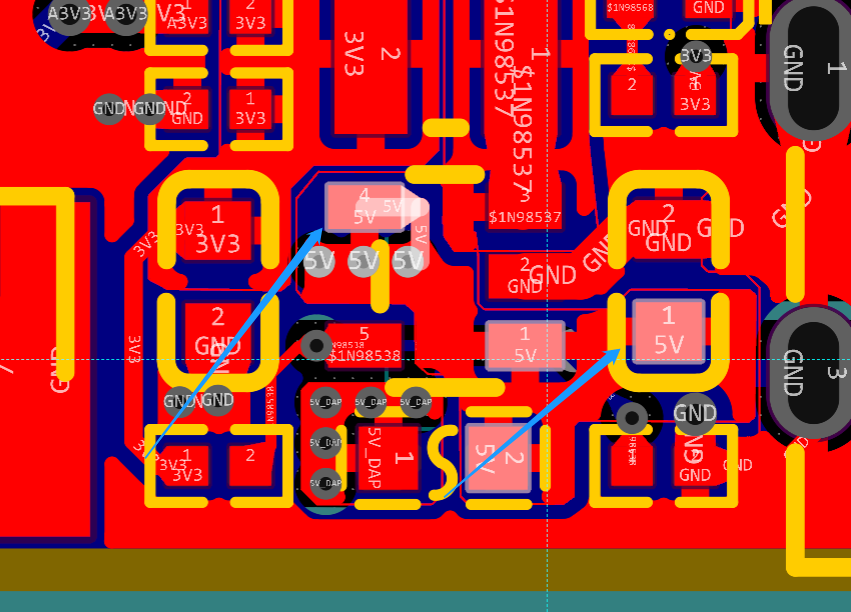

Xnet关联网络

部分网络在原理图设计时需要添加串阻等器件进行信号阻抗匹配,此时,需要将串联器件2端网络进行关联,以方便等长规则设置。1)执行菜单命令命令“设置-电气网络”,打开对应的电气网络对话框,如图5-144所示。图5-144“电气网络”菜单命令2)在

PADS蛇形等长处理

在做PCB设计时,为了满足某一组所有信号线的总长度满足在一个公差范围内,通常要使用蛇形走线将总长度较短的信号线绕到与组内最长的信号线长度公差范围内,这个用蛇形走线绕长信号线的处理过程,就是俗称的PCB信号等长处理。如图6-59示。图6-59

在DDR的设计中,需要对数据线及地址线进行分组及等长来满足时序匹配,通常DDR的数据线之间的长度误差需要保证在50mil以内,地址线的长度误差需要保证在100mil以内。执行菜单命令【设计】-【规则】或者使用快捷键DR打开规则约束器,在“H

1.电源输入的滤波电容应该靠近输入管脚放置2.【问题分析】:注意等长线之间需要满足3W规则3.【问题分析】:USB需要进行等内等长处理,等长误差为5mil4.此处是用菊花链的方式进行等长,建议使用创建焊盘对组进行分段等长(U1-U2,U2-

扫码关注

扫码关注