- 全部

- 默认排序

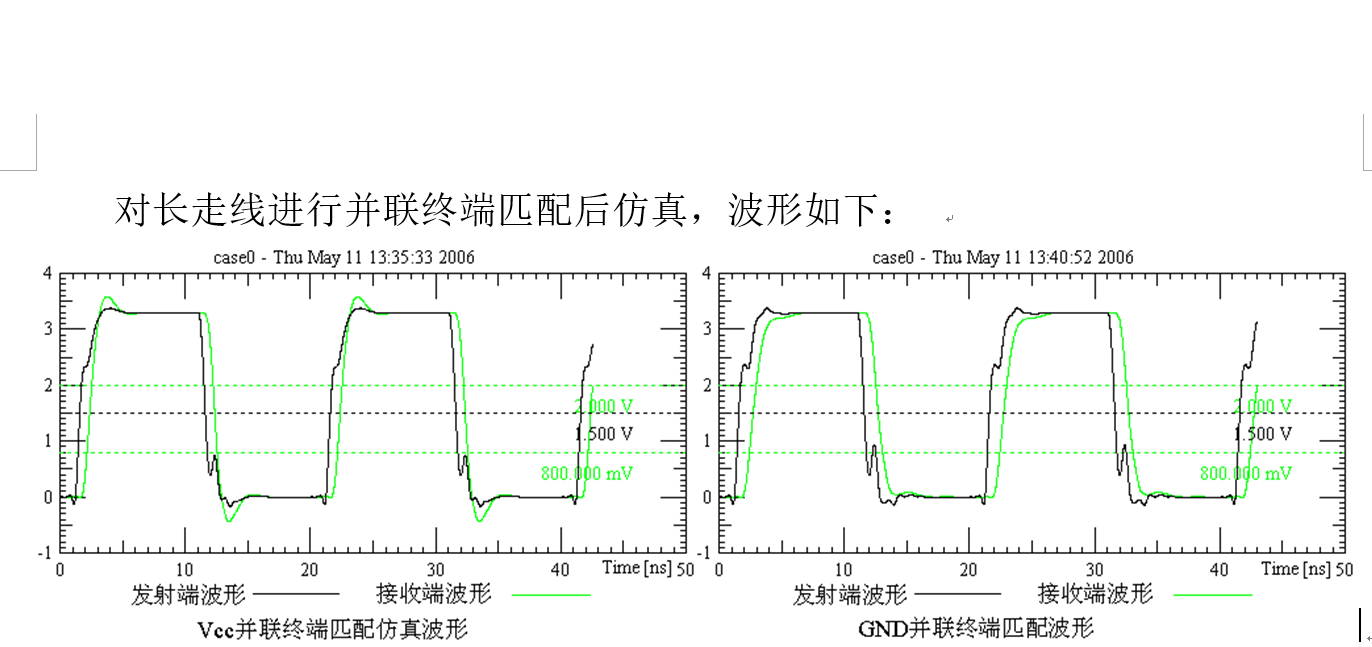

并联终端匹配是最简单的终端匹配技术:通过一个电阻R将传输线的末端接到地或者接到VCC上。电阻R的值必须同传输线的特征阻抗Z0匹配,以消除信号的反射。如果R同传输线的特征阻抗Z0匹配,不论匹配电压的值如何,终端匹配电阻将吸收形成信号反射的能量。终端匹配到VCC可以提高驱动器的源的驱动能力,而终端匹配到地则可以提高电流的吸收能力。

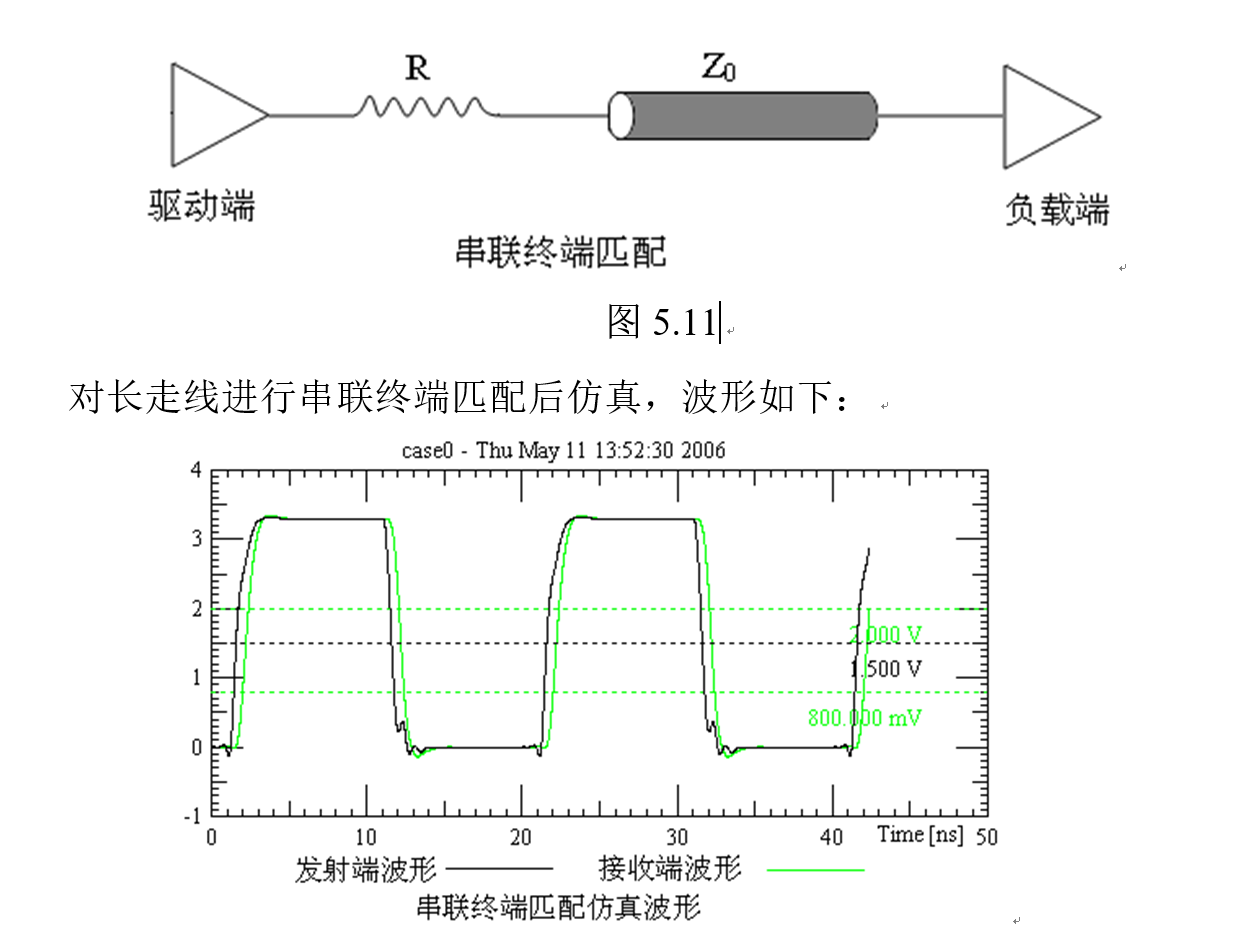

串联终端匹配技术,也称之为后端终端匹配技术,不同于其它类型的终端匹配技术,是源端的终端匹配技术。串联终端匹配技术是在驱动器输出端和信号线之间串联一个电阻。驱动器输出阻抗R0以及电阻R值的和必须同信号线的特征阻抗Z0匹配。对于这种类型的终端匹配技术,由于信号会在传输线、串联匹配电阻以及驱动器的阻抗之间实现信号电压的分配,因而加在信号线上的电压实际只有一半的信号电压。

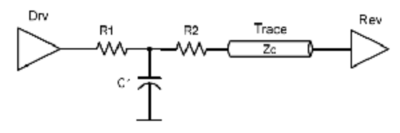

戴维南终端匹配技术或者也叫做双电阻终端匹配技术,采用两个电阻来实现终端匹配,R1和R2的并联组合要求同信号线的特征阻抗Z0匹配。R1的作用是帮助驱动器更加容易地到达逻辑高状态,这通过从VCC向负载注入电流来实现。与此相类似,R2的作用是帮助驱动器更加容易地到达逻辑低状态,这通过R2向地释放电流来实现。

端接电阻的认识和放置

端接电阻是用来实现阻抗匹配的。 什么是阻抗匹配,对于波形信号,在传输和使用的过程中会产生非线性阻抗,例如线路中存在电容或电感等非线性原件, 对于高频的信号不知道什么时候就会产生阻抗,此时就会影响信号的特性,频率或者能量都会改变,可以通过在电路中加入一种电阻控制电路的阻抗使之达到不影响信号,这种电阻就是端接电阻。端接电阻分为并行端接和串行端接两种

答:端接,Butt Joint,是指消除信号反射的一种方式。在高速PCB设计中,信号的反射将给PCB的设计质量带来很大的负面影响,采用端接电阻来达到线路的阻抗匹配,是减轻反射信号影响的一种有效可行的方式。端接,分为一下两类:Ø 源端端接,接在信号源端或信号发送端的端接,一般与信号走线串接;Ø 终端端接,接在信号终端或信号接收端的端接,一般与信号走线并接。源端端接的优点是接供较慢的上升时间,减少反射量,产生更小的EMI,从而降低过冲,增加信号的传输质量。我们在PCB设计中处理源

答:端接,Butt Joint,是指消除信号反射的一种方式。在高速PCB设计中,信号的反射将给PCB的设计质量带来很大的负面影响,采用端接电阻来达到线路的阻抗匹配,是减轻反射信号影响的一种有效可行的方式。端接,分为一下两类:

在进行阻抗匹配的时候我们可以在电阻源端放置一个串联端接电阻,但是有时候受到空间的限制可能会把电阻摆的稍微远一点,那么这个时候大家可能会有疑问,电阻离发送端远一点或者电阻放置在接收端,那么电阻还能消除传输线的反射吗?下面我们一起来验证一下!1

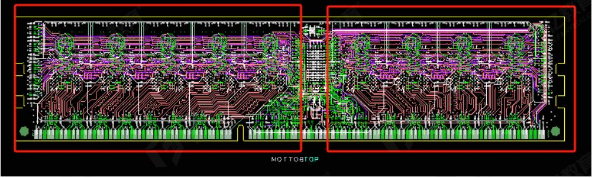

上次我们对不加端接电阻和加端接电阻之后的仿真结果做了分析之后我们得出在DDR采用菊花链拓扑结构的时候是需要加端接电阻的,这次我们看看DDR末端的端接电阻距离最后一片DDR远一点效果好一些还是近一点效果好一些。本次采用的案例依旧是我们上期的D

扫码关注

扫码关注