- 全部

- 默认排序

信号完整性是指信号在信号线上的质量。信号具有良好的信号完整性是指当在需要的时候,具有所必需达到的电压电平数值。差的信号完整性不是由某一因素导致的,而是由板级设计中多种因素共同引起的。特别是在高速电路中,所使用的芯片的切换速度过快、端接元件布设不合理、电路的互联不合理等都会引起信号的完整性问题。具体主要包括串扰、反射、过冲与下冲、振荡、信号延迟等。

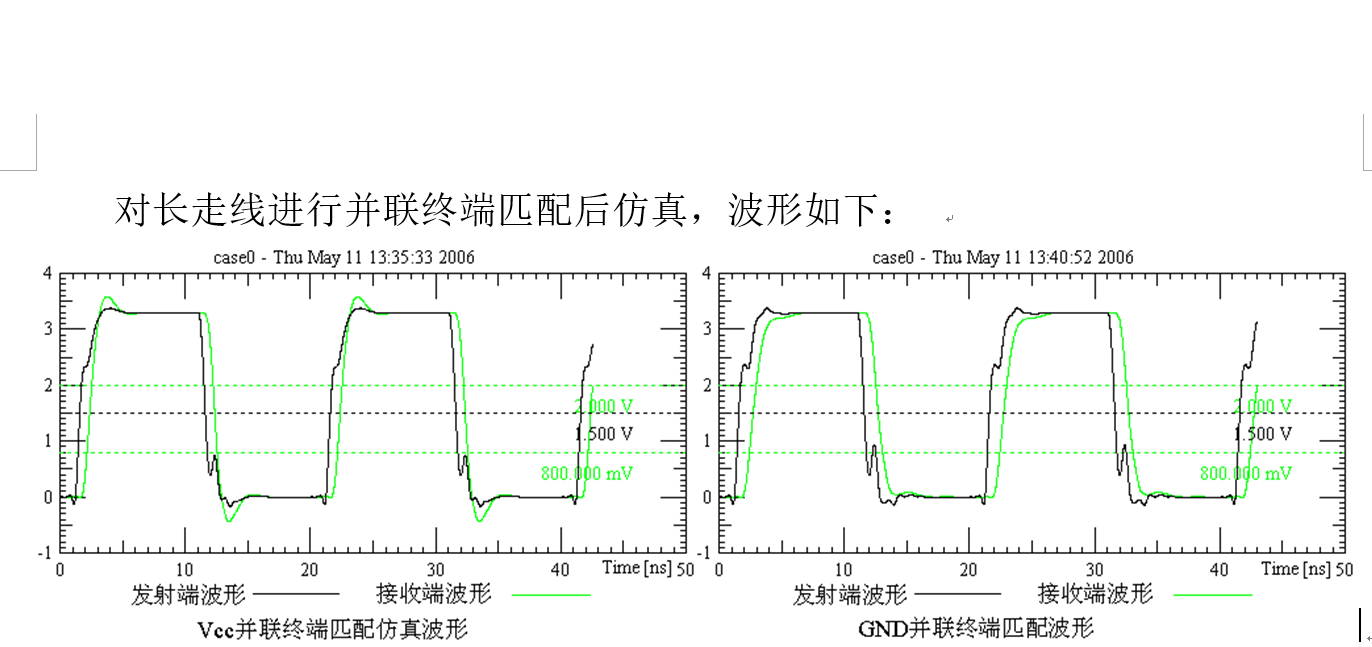

并联终端匹配是最简单的终端匹配技术:通过一个电阻R将传输线的末端接到地或者接到VCC上。电阻R的值必须同传输线的特征阻抗Z0匹配,以消除信号的反射。如果R同传输线的特征阻抗Z0匹配,不论匹配电压的值如何,终端匹配电阻将吸收形成信号反射的能量。终端匹配到VCC可以提高驱动器的源的驱动能力,而终端匹配到地则可以提高电流的吸收能力。

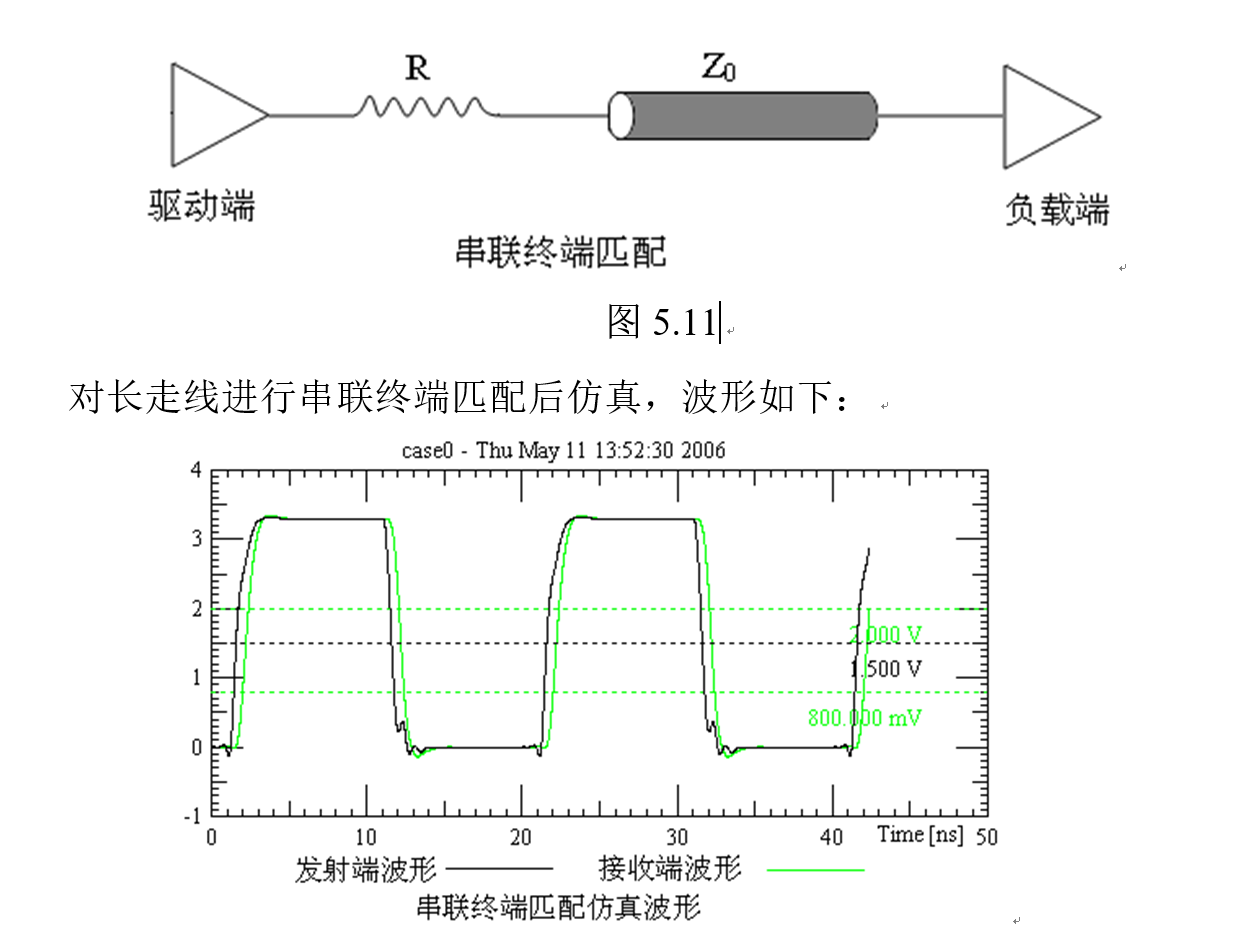

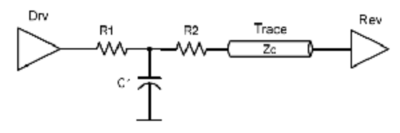

串联终端匹配技术,也称之为后端终端匹配技术,不同于其它类型的终端匹配技术,是源端的终端匹配技术。串联终端匹配技术是在驱动器输出端和信号线之间串联一个电阻。驱动器输出阻抗R0以及电阻R值的和必须同信号线的特征阻抗Z0匹配。对于这种类型的终端匹配技术,由于信号会在传输线、串联匹配电阻以及驱动器的阻抗之间实现信号电压的分配,因而加在信号线上的电压实际只有一半的信号电压。

戴维南终端匹配技术或者也叫做双电阻终端匹配技术,采用两个电阻来实现终端匹配,R1和R2的并联组合要求同信号线的特征阻抗Z0匹配。R1的作用是帮助驱动器更加容易地到达逻辑高状态,这通过从VCC向负载注入电流来实现。与此相类似,R2的作用是帮助驱动器更加容易地到达逻辑低状态,这通过R2向地释放电流来实现。

端接电阻的认识和放置

端接电阻是用来实现阻抗匹配的。 什么是阻抗匹配,对于波形信号,在传输和使用的过程中会产生非线性阻抗,例如线路中存在电容或电感等非线性原件, 对于高频的信号不知道什么时候就会产生阻抗,此时就会影响信号的特性,频率或者能量都会改变,可以通过在电路中加入一种电阻控制电路的阻抗使之达到不影响信号,这种电阻就是端接电阻。端接电阻分为并行端接和串行端接两种

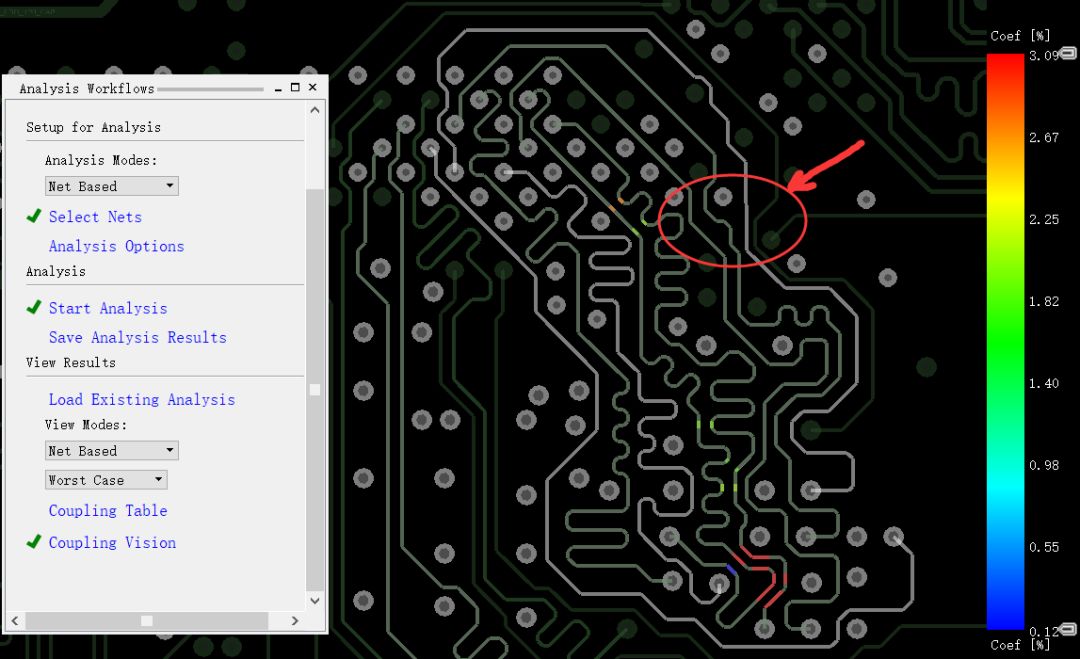

串扰是两条信号线之间的耦合、信号线之间的互感和互容引起线上的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。 PCB板层的参数、信号线间距、驱动端和接收端的电气特性及线端接方式对串扰都有一定的影响。下面是在SigXplorer里面搭建了一个串扰的仿真链路,黄色部分就是得到的信号之间的串扰分析结果。

答:端接,Butt Joint,是指消除信号反射的一种方式。在高速PCB设计中,信号的反射将给PCB的设计质量带来很大的负面影响,采用端接电阻来达到线路的阻抗匹配,是减轻反射信号影响的一种有效可行的方式。端接,分为一下两类:Ø 源端端接,接在信号源端或信号发送端的端接,一般与信号走线串接;Ø 终端端接,接在信号终端或信号接收端的端接,一般与信号走线并接。源端端接的优点是接供较慢的上升时间,减少反射量,产生更小的EMI,从而降低过冲,增加信号的传输质量。我们在PCB设计中处理源

答:上拉、下拉电阻的作用有如下几种:提高电压准位:当TTL电路驱动COMS电路时,如果TTL电路输出的高电平低于COMS电路的最低高电平(一般为3.5V), 这时就需要在TTL的输出端接上拉电阻,以提高输出高电平的值;OC门电路必须加上拉电阻,以提高输出的搞电平值;加大输出引脚的驱动能力,有的单片机管脚上也常使用上拉电阻;N/A pin防静电、防干扰:在COMS芯片上,为了防止静电造成损坏,不用的管脚不能悬空,一般接上拉电阻产生降低输入阻抗, 提供泄荷通路。同时管脚悬空就比较容易接受外界的电磁干

答:端接,Butt Joint,是指消除信号反射的一种方式。在高速PCB设计中,信号的反射将给PCB的设计质量带来很大的负面影响,采用端接电阻来达到线路的阻抗匹配,是减轻反射信号影响的一种有效可行的方式。端接,分为一下两类:

全站最新内容推荐

- 1加码技术,打破困境,PSPice电路仿真助你解锁职场新高度!

- 2简谈稳压二极管和普通二极管的区别

- 3贴片元件如何拆卸及焊接?

- 4盘点电子工程师必须了解的21个电路

- 5英伟达GB300芯片受阻,存在过热问题

- 6WARELEO李增原创H04课程大纲的安排课程中内容及工具及课程的重点学习办法的讲解

- 7WARELEO李增原创H03根据自己的关注知识点和所需要的知识来选择需要的图书包邮递

- 8WARELEO李增原创H02理工男生李老师的介绍从51单片机驱动到FPGA到仿真设计之路

- 9WARELEO李增原创H01信号电源完整性设计与HFSS射频天线设计仿真验证研修课程主题

- 10WARELEO李增:反射仿真的信号观察办法及时域串扰的仿真设置及观察技巧

扫码关注

扫码关注