- 全部

- 默认排序

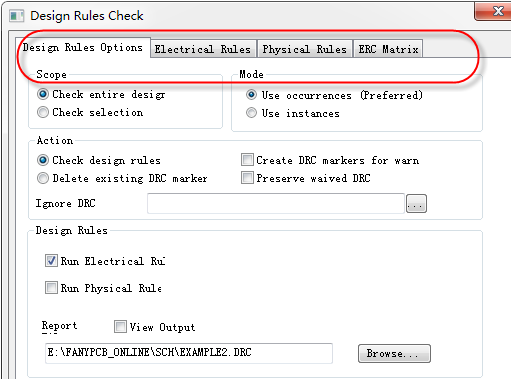

答:第一步,选择原理图的根目录,然后执行菜单Tools-Design Rules Check,进行设计规则的检查,如图3-61所示; 图3-61 进行DRC检查示意图第二步,弹出的DRC检测界面中,有4项的参数可以设置,可以依次进行选择,如图3-62所示,Design Rules Options为检查的参数设置,Electrical Rules为电气规则检查参数设置,Physical Rules为物理规则检查参数设置,ERC Matrix为DRC矩阵设置是否报DRC。 图3-

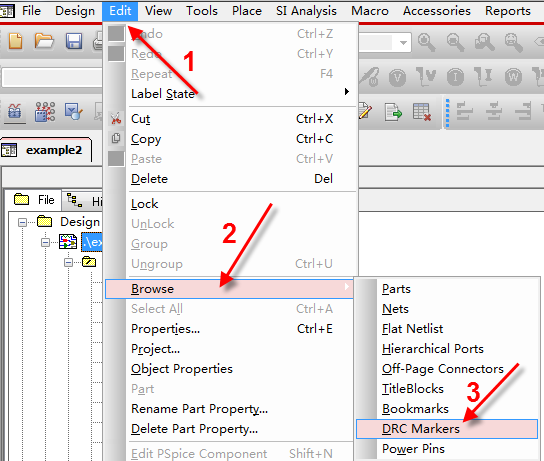

答:对原理图文件进行DRC检测以后,按照设置的DRC检测的选项,会在原理图中留下DRC的标记,对于分页的原理图来说,每一页每一页的去查看DRC的标记,比较繁琐,这里可以运用Browse功能,查看所有的DRC,操作方法如下:第一步,选中原理图的根目录,执行菜单Edit→Browse功能,然后选择DRC Marks,进行DRC标记的查看,如图3-66所示: 图3-66 浏览DRC Marks设置示意图第二步,执行命令以后,如图3-67所示,DRC ERROE显示的是错误的类型说明,DRC

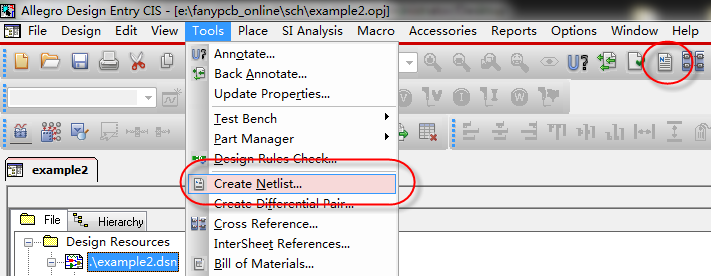

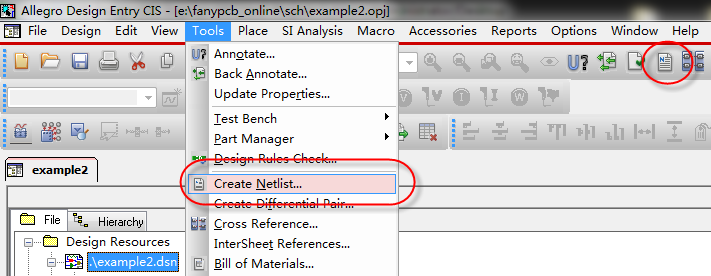

答:orcad产生Cadence Allegro的网表的操作步骤如下;第一步,选择原理图根目录,执行菜单Tools→Creat Netlist,或者是点击菜单栏上的图标,调出产生网表的界面,如图3-68所示; 图3-68 产生网表示意图第二步,弹出的Creat Netlist界面中,选择的是PCB Editor,产生Allegro的第一方网表,如图3-69所示; 图3-69 Allegro第一方网表参数设置示意图第三步,输入Allegro第一方网表需要注意下面几个

答:orcad产生Cadence Allegro的网表的操作步骤如下;第一步,选择原理图根目录,执行菜单Tools→Creat Netlist,或者是点击菜单栏上的图标,调出产生网表的界面,如图3-74所示; 图3-74 输出网表示意图第二步,弹出的输出网表界面中选择Other选项,来输出第三方网表,如图3-75所示,在Formatters栏中选择orTelesis.dll选项,上面的Part Value栏需要用PCB Footprint来代替,不然会产生错误;

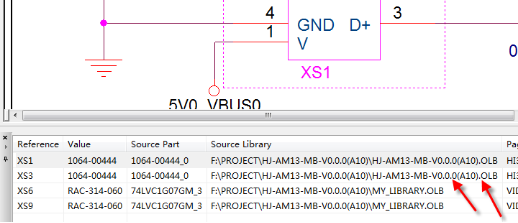

答:在使用Orcad软件输出Allegro第一方网表,出现如下错误:#1 ERROR(ORCAP-36055): Illegal character in \hj-am13-mb-v0.0.0(a10)\.解决的办法如下所示:第一步,错误的提示标明的含义的表示有非法字符, 跟这个的就是一串的非法字符,我们要做的就是把非法字符改掉;第二步,首先定位非法字符的位置,选中原理图根目录,在搜索栏输入* 非法字符*进行搜索,这个就是* hj-am13-mb-v0.0.0(a10)*,如

答:我们在运用Orcad软件进行原理图的设计完成以后,需要通过Orcad软件进行物料清单的输出、然后对BOM清单进行整理。下面我们列一下,运用Orcad软件进行BOM清单输出的步骤如下:第一步,打开原理图主目录的界面,关闭掉其它的分界面,然后选中原理图的根目录,进行下一步的操作,如图3-90所示: 图3-90 原理图根目录选中示意图第二步,选中根目录以后,执行菜单命令Tools-Bill of Materials…命令,来进行BOM清单的输出,如图3-91所示: 图3-91

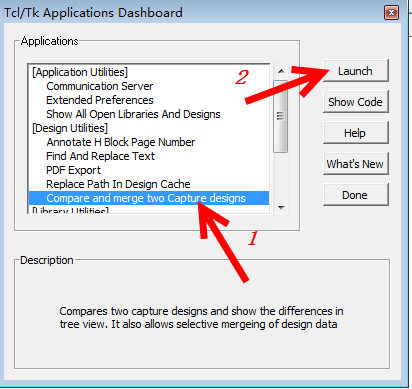

答:在电子设计中, 电路图的修改是非常频繁的,改动的多了,有时候会出现要改回去的情况,所以有时就会需要对两份原理图进行差分化的对比,操作步骤如下:第一步,首先,我们对一份原理图进行修改,修改一点点内容,做为测试之用,如图3-123与图3-124所示,方便后期查找; 图3-123 修改后的原理图示意 图3-124 修改前的原理图示意第二步,我们打开其中的任意一份原理图,选中原理图的根目录,然后执行菜单命令Accessories-Cadence TcL/Tk Utilities命

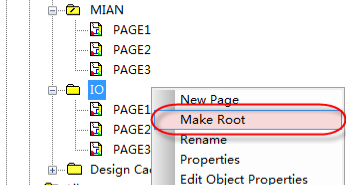

答:在使用Orcad软件绘制原理图时,通常会把一个工程下面对应的不同部分的原理图绘制在一起,如图3-184所示,这样方便后期的检查与查看,这样做有一个问题,你会发现输出网表的时候,不能全部输出,一下子只能输出一个文件的网表。这里我们给大家讲述一下怎么输出所有文件的网表: 图3-184 原理图不同的工程示意图第一步,我们选中原理图的根目录时,点击输出网表的命令,输出的网表都是最上面的那个MIAN的三页图纸的网表;第二步,我们需要输出下面的IO的三页图纸的网表,需要将IO原理图

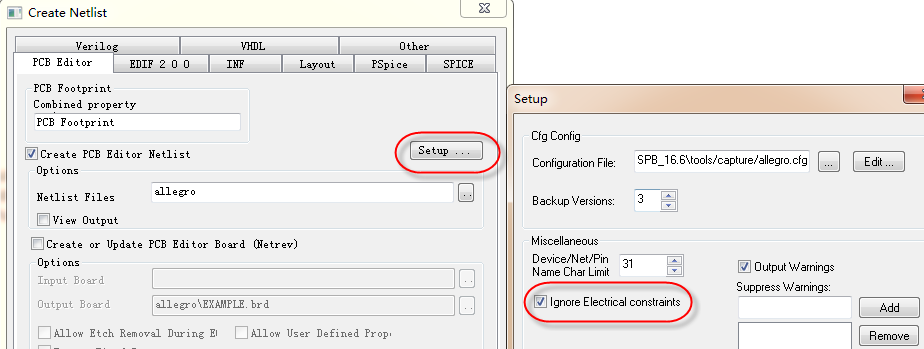

答:我们在进行PCB设计的时候呢,尽量不要把原理图的规则导入到PCB中,我们需要在输出网表的时候进行设置,具体的操作步骤如下所示:第一步,选中原理图的根目录文件即DSN文件,进行网表的输出,执行菜单Tools-Create Netlist,创建网表;第二步,在弹出的输出PCB网络表的对话框中,其它地方都是不用勾选的,在右侧有一个Setup选项,是输出网络的参数设置按钮,我们需要在这里进行不输出原理图规则的设置;第三步,点击输出网表的Setup选项,进行参数的设置,如图3-211所示,在左侧箭头所

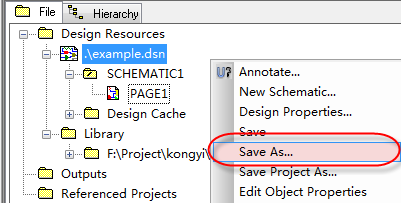

答:我们在进行原理图设计或者是进行PCB设计,都会遇到这样的问题,需要降低设计文件的版本,我们这里讲解下,Orcad软件设计的原理图如何去降低原理图的版本,操作的步骤很简单,我们这里列举一下操作的步骤:第一步,需要选中降低原理图的根目录就是DSN文件,如图3-212所示,选中之后,点击鼠标右键,Save As,就可以存为低的版本; 图3-212 原理图另存低版本示意图第二步,在弹出的界面中,如图3-213所示,在保存类型那一栏可以选择低的版本,一般是存为16.2的版本,这样就存为了低的

扫码关注

扫码关注