- 全部

- 默认排序

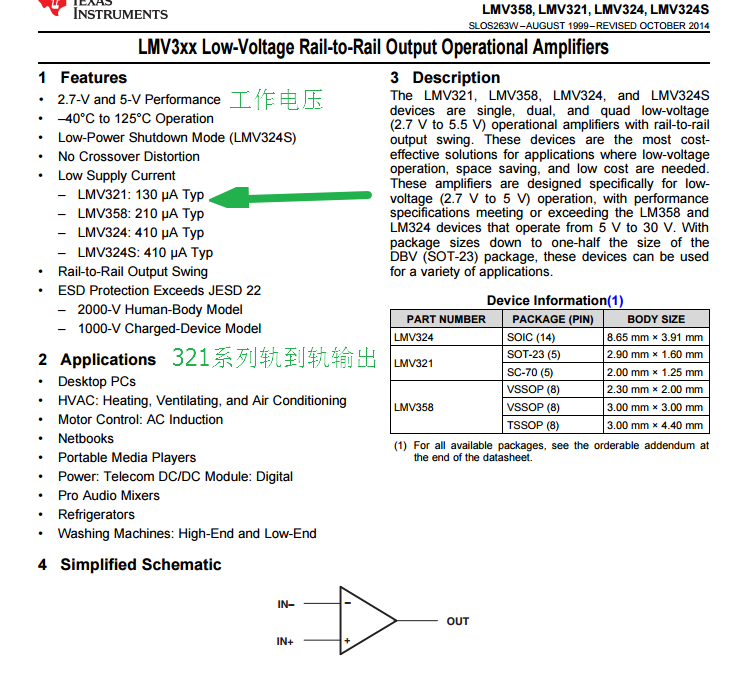

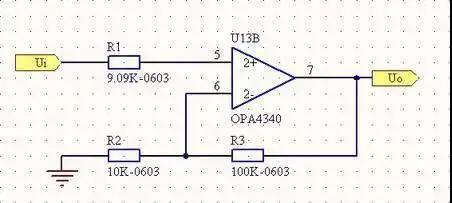

运放电流检测电路

使用运放电流检测,检测方式有高端检测和低端检测两种运放电路。高端运放电流检测优点:-可以检测区分负载是否短路-无地电平干扰缺点:-共模电压高,使用非专用分立器件设计较复杂、成本高、面积大低端运放电流检测优点:-共模电压低,可以使用低成本的普通运算放大器缺点:-检流电阻引入地电平干扰,电流越大地电位干扰越明显

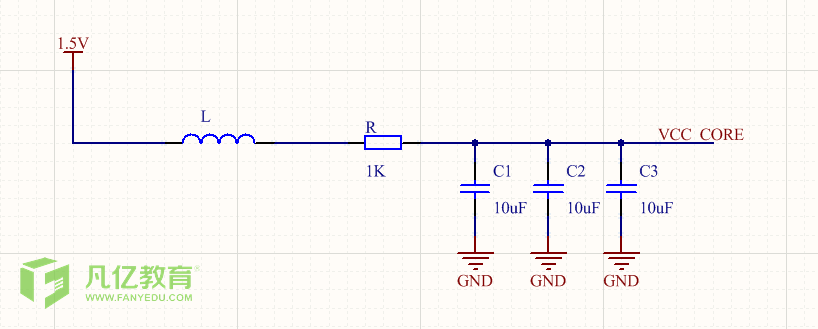

假设下图是一个单板上的PHY芯片的核心电源滤波电路设计。 * 根据这个PHY芯片的资料,这个电源对噪声等方面的干扰特别明显,所以这个设计中不仅采用了,LC滤波电路。还在电感L的后面串联了一个1欧的电阻R。LC滤波电容能滤除高频段噪声。而在这个电路中的这个电阻R不但能衰减高频段噪声,而且能衰减低频段噪声。可以作为一个全频段的衰减器,这种电路设计方法一般用于对噪声特别敏感的电源,如时钟的电源等等。但是单板的长时间运行发现,电阻R经常爆裂。 * 电路设计中选用的电阻R,尺寸是040

电路磁珠的滤波机理

磁珠的外形与电感相似,其主要功能是吸收电源、信号上的噪声等干扰。请注意到“吸收”俩个字。电容本身就可以起到滤波作用,电感和电容配合也能起到滤波作用,但这种滤波,并没有真正的将噪声消除。例如,电容的滤波其原理是在高频时建立一条通往地平面的低阻抗通道,以便将噪声泄放到地平面。而电感和电容配合的滤波,其原理是构建成一个低通滤波器,是让频段比较低的信号顺利而衰减的通过,而阻断频段比较高的噪声,低通滤波器对高频噪声而言,近似一个极大的电阻。高频段噪声遇到这个极大的电阻,只能是被反射回去,基于该原理,应用低

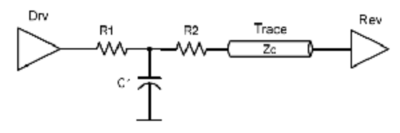

端接电阻的认识和放置

端接电阻是用来实现阻抗匹配的。 什么是阻抗匹配,对于波形信号,在传输和使用的过程中会产生非线性阻抗,例如线路中存在电容或电感等非线性原件, 对于高频的信号不知道什么时候就会产生阻抗,此时就会影响信号的特性,频率或者能量都会改变,可以通过在电路中加入一种电阻控制电路的阻抗使之达到不影响信号,这种电阻就是端接电阻。端接电阻分为并行端接和串行端接两种

上下拉电阻那些事

上拉就是将不确定的信号通过一个电阻嵌位在高电平!电阻同时起限流作用!下拉同上拉是对器件注入电流,下拉是输出电流:弱强只是上拉电阻的阻值不同,没有什么严格区分:对于非集电极(或漏极)开路输出型电路(如普通门电路)提升电流和电压的能力是有限的,上拉电阻的功能主要是为集电极开路输出型电路输出电流通道。

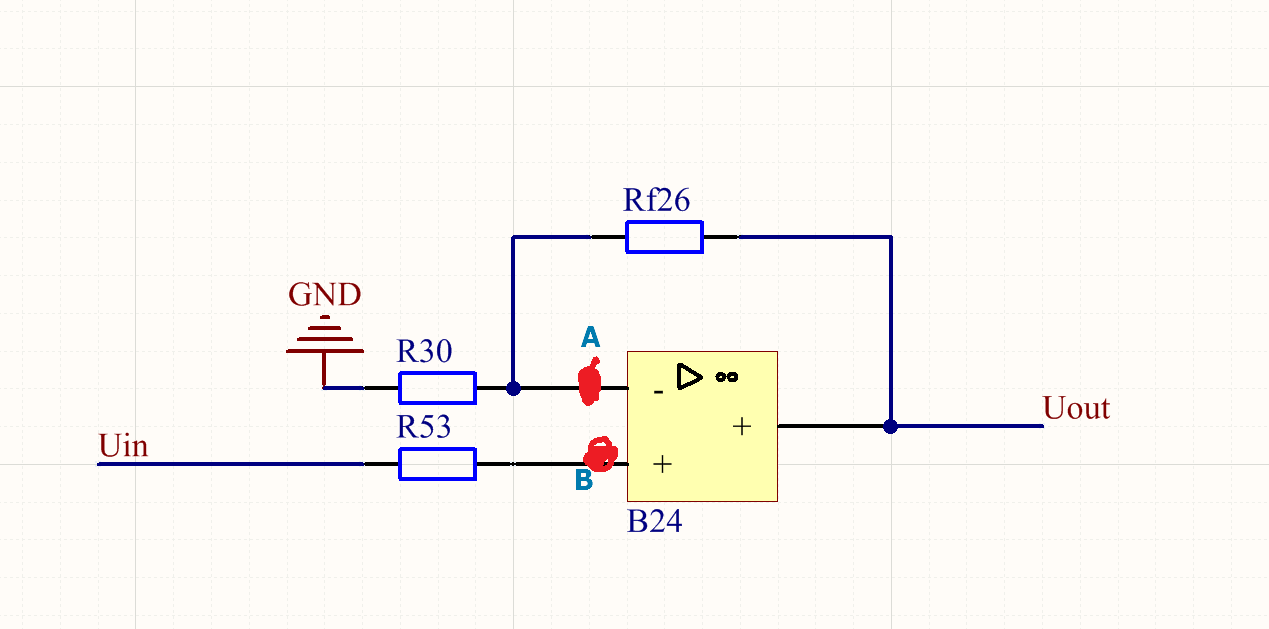

串并联反馈如何判断

串联反馈:是指我们的反馈元件从反馈网络中取出反馈信号用串联的形式把反馈电压和我们的输入回路相减 串联反馈:降低放大器的电压放大倍数,稳定放大器的电压增益。由于是串联所以提高了输入电阻。

运放组成的反馈电路分析

运放电路反馈分为:电流反馈,增大输出电阻,稳定输出电流 电压反馈,减少输出电阻,稳定输出电压。串联反馈,增大输入电阻,稳定输入电压,降低电压放大倍数。并联反馈,减少输入电阻,稳定输出电流,降低电流放大倍数

扫码关注

扫码关注