- 全部

- 默认排序

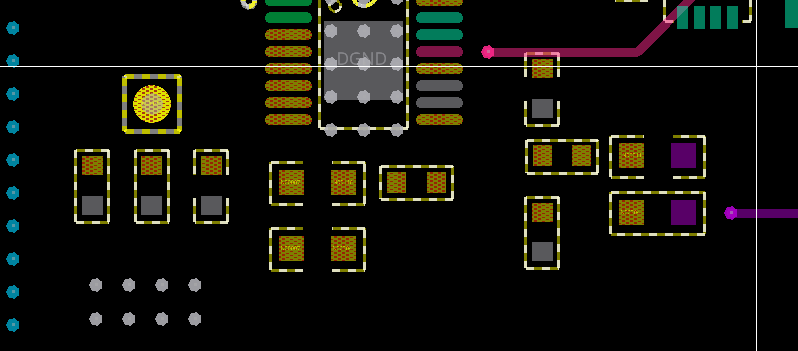

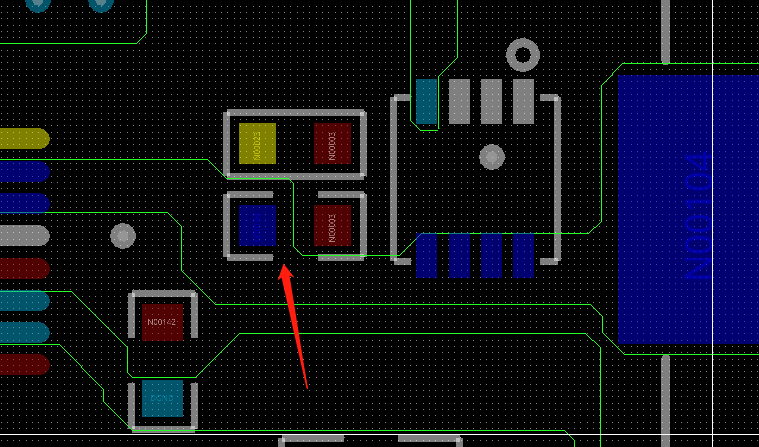

USB2.0注意铜皮不要有任意角度USB3.0差分对内等长锯齿状不能超过线距的两倍2.此处采用兼容设计,两个电阻可以放置在共模电感上面3.打孔要打在电容之前,注意 线宽要保持一致4.差分走要耦合5.差分对,间距最少保持20mil6.存在多余

过流短路其实是一个原理,通过在输出端串接一个检测电阻,将需要保护的电流值转化为电压值,将此电压值送入运放,与基准电压比较,即可得出一个信号,用来控制保护是否启动。过流都可以保护了,那短路其实就是过流的极限状态,只是此时由于短路,输出电压没有了,这时颗配合初级的MOSFET的限流电阻控制最大输出功

在电子工程领域,数字万用表是一种常见的测量工具,常用于测量电压、电流、电阻等各种参数,一般来说,数字万用表的精度是评估其测量准确度的重要指标之一,常见的数字万用表精度为5位半和6位半,这两者有什么区别?1、5位半精度的数字万用表5位半精度的

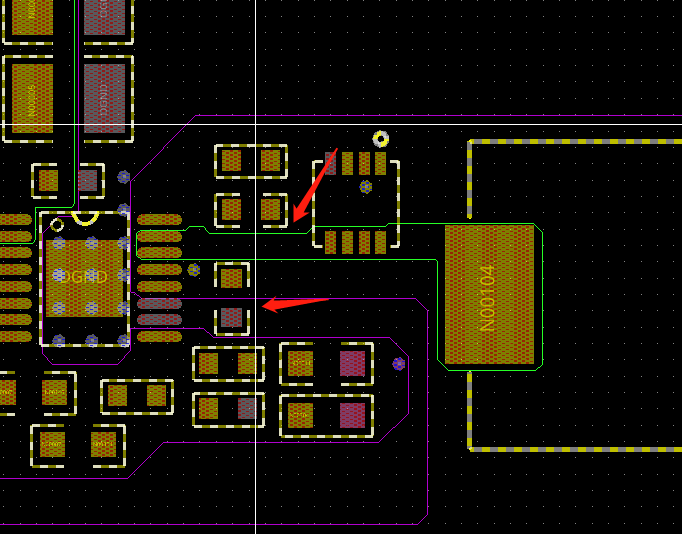

此处的电阻电容塞到芯片底部,跟对应网络进行连接:机壳地跟电路地之间至少间距2MM,除了 跨接器件部分:变压器每层都需要挖空:变压器上除了差分其他信号加粗到20MIL:晶振注意从滤波电容那里包地处理:一把RX 或者TX的信号线尽量是一把紧凑整

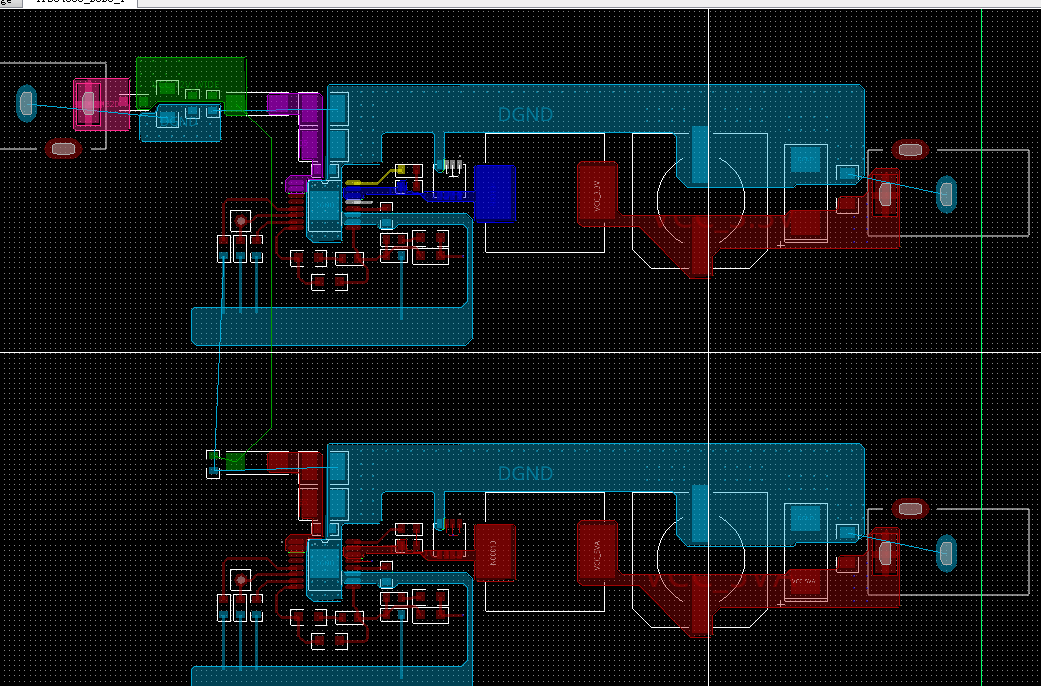

电源跟地都没有处理,还存在飞线,一定需要处理:配置电阻电容可以向上或者向下移动,中间布局优先于电源主干道,重新优化下布局:并且配置电阻电容尽量整体对齐以及紧凑,不要太松散了:一路跟二路的输入电源都没有铺铜连接:输出主干道的铜皮太窄,完全满足

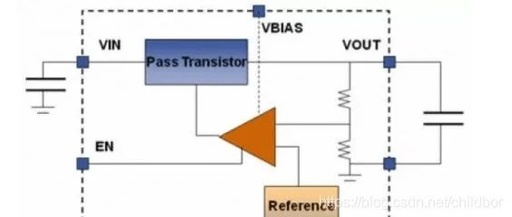

LDO概念LDO,low dropout regulator,中文是低压差线性稳压器,它内部的一般结构如下图: 用到的元器件也比较简单,一个串联调整管VT,两个分压电阻R1,R2,放大器A,基准电压REF部分,然后就可以把输入和输出连接起来,由R1和R2分压得到的放大器的同相输入端电压为取样电压,放

电线过细会不会更加耗电?

当电子工程师在设计PCB布局布线时都会犹豫电线的粗细,电线的尺寸直接影响电路的性能和能耗,在选择电线尺寸时,需要综合考虑电流负载、电线长度、功率损耗及电源的供应能力等,那么电线过细是否会更加耗电?一般来说,电线过细会带来以下问题:1、高电阻

配置电阻电容可以稍微移动下,留出空间给主干道铺铜:注意电感当前层内部挖空处理:反馈信号没有连接:第二路DCDC的电源跟地都没有处理,都是需要处理的 :以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链

配置电阻电容可以稍微紧凑点:铜皮注意尽量不要直角锐角 ,可以优化下:其他的没什么问题了。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.co

优先主干道的器件摆放,其他的配置电阻电容可以靠上放置,中间留出主干道空间:此处的电源跟地的走线完全满足不了载流:自己铺铜处理或者加粗走线。走线不要从器件内部穿过:主干道的铜皮不要太细了,尽量都均匀点:电感内部当前层挖空处理:以上评审报告来源

扫码关注

扫码关注