- 全部

- 默认排序

一块好的电路板,除了实现电路原理功能之外,还要考虑EMI、EMC、ESD(静电释放)、信号完整性等电气特性,也要考虑机械结构、大功耗芯片的散热问题,在此基础上再考虑电路板的美观问题,就像进行艺术雕刻一样,对其每一个细节进行斟酌。

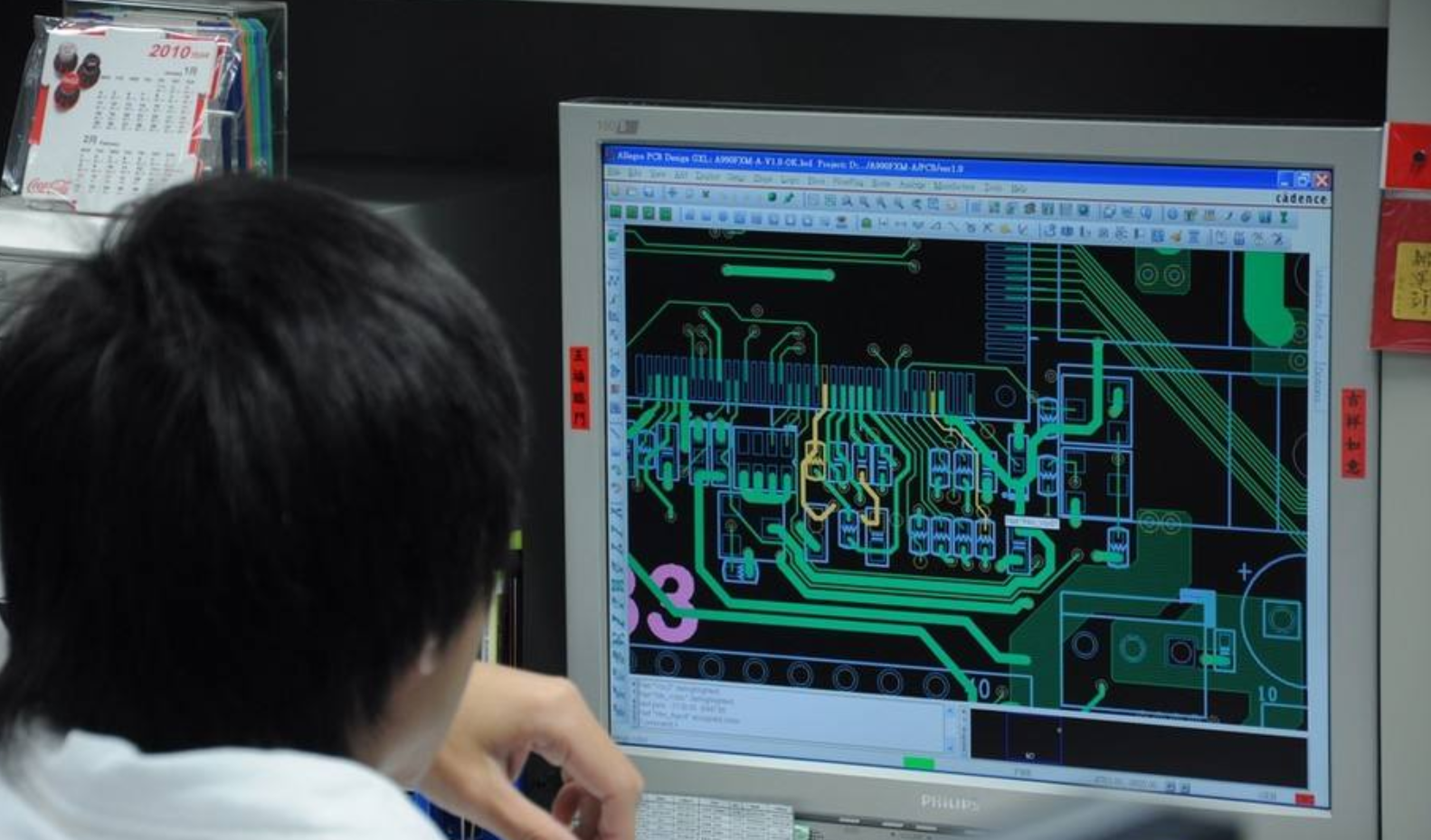

现在越来越多的高速设计是采用一种有利于加快开发周期的更有效的方法。先是建立一套满足设计性能指标的物理设计规择,通过这些规则来限制PCB布局布线。在器件安装之前,先进行仿真设计。在这种虚拟测试中,设计者可以对比设计指标来评估性能。而这些关键的前提因素是要建立一套针对性能指标的物理设计规则,而规则的基础又是建立在基于模型的仿真分析和准确预测电气特性之上的,所以不同阶段的仿真分析显得非常重要。

在研究由反射引起的振铃效应前,先讨论由电路谐振引起的振铃效应。在时钟速度高达10MHz的数字系统中,振铃(Ringing)现象是设计中的显著问题。传导系统对输入信号的响应,在很大程度上取决于系统的尺寸是否小于信号中最快的电气特性的有效长度,反之亦然。电气特性的有效长度由它的持续时间和传播延迟决定,即l=Tr/D(Tr =上升时间,ps;D=延迟,ps/in)。如果走线长度小于有效长度的1/6,该电路表现为集总系统,如果系统对输入脉冲的响应是沿走线分布的,称之为分布系统。

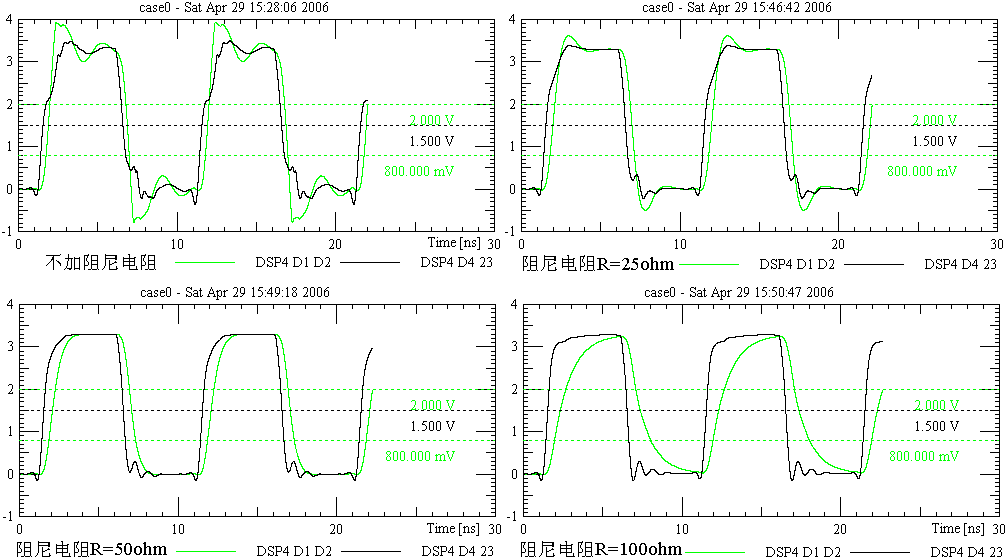

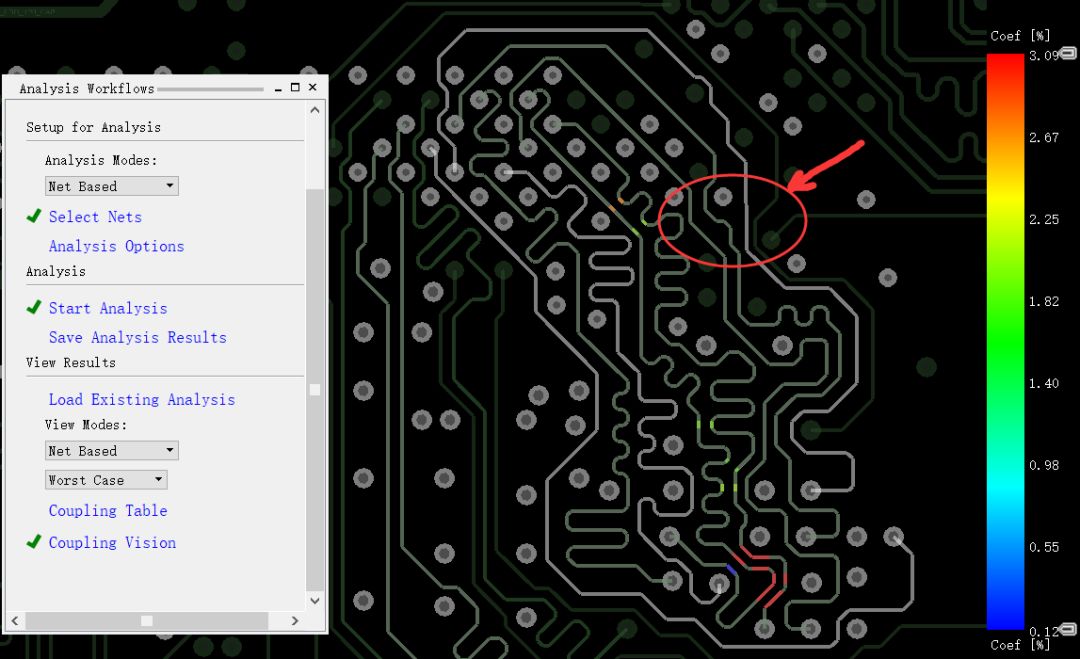

串扰是两条信号线之间的耦合、信号线之间的互感和互容引起线上的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。 PCB板层的参数、信号线间距、驱动端和接收端的电气特性及线端接方式对串扰都有一定的影响。下面是在SigXplorer里面搭建了一个串扰的仿真链路,黄色部分就是得到的信号之间的串扰分析结果。

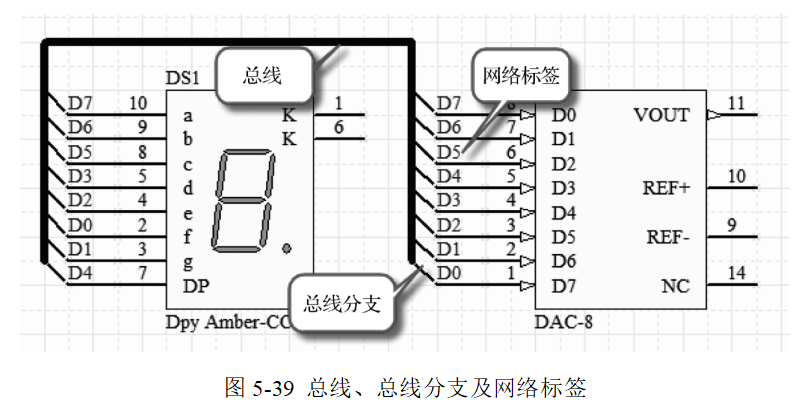

总线由总线,总线分支及网络标号组成,代表具有相同电气特性的一组导线,在具有相同电气特性的导线数目较多的情况下,可采用总线的方式,以方便识图,这里就讲解下如何放置总线及总线分支。

No ERC检查点即忽略ERC检查点,是指该点所附加的元件管脚在进行ERC检查时,如果出现错误或者警告,错误或者警告将被忽略过去,不影响网络表的生成。忽略ERC检查点本身不具有任何的电气特性,主要用于检查原理图

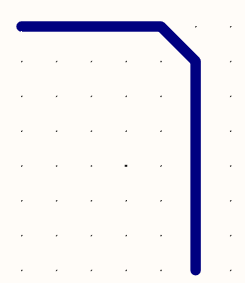

Altium Designer原理图电气连接的放置— 绘制导线及导线属性设置导线是用来连接电气元件、具有电气特性的连线。1.绘制导线(1)执行菜单命令“放置-线”,如图5-30中左图所示,或者也可以按快捷键“B,激活放置导线命令,使鼠标光标

在硬件开发项目中,工程师不仅要注重开发工具的使用及详细流程,也要与软件开发、CAD等相关人员进行沟通,同时也要具备接口标准相关知识。所以本文将分享硬件开发项目中常用的接口及接口标准。常用的接口类型,按物理电气特性划分,大致可分为以下几类:1

单纯的网络标签虽然可以表示图纸中相连的导线,但是由于连接位置的随意性,给工程人员分析图纸、查找相同的网络标签带来一定的困难。总线代表的是具有相同电气特性的一组导线,在具有相同电气特性的导线数目较多的情况下,可采用总线的方式,以方便识图。总线

No ERC检查点即忽略ERC检查点,是指该点所附加的元件管脚在进行ERC时,如果出现错误或者警告,错误或者警告将被忽略过去,不影响网络报表的生成。忽略ERC检查点本身并不具有任何的电气特性,主要用于检查原理图。 图5-50 放置No E

扫码关注

扫码关注