- 全部

- 默认排序

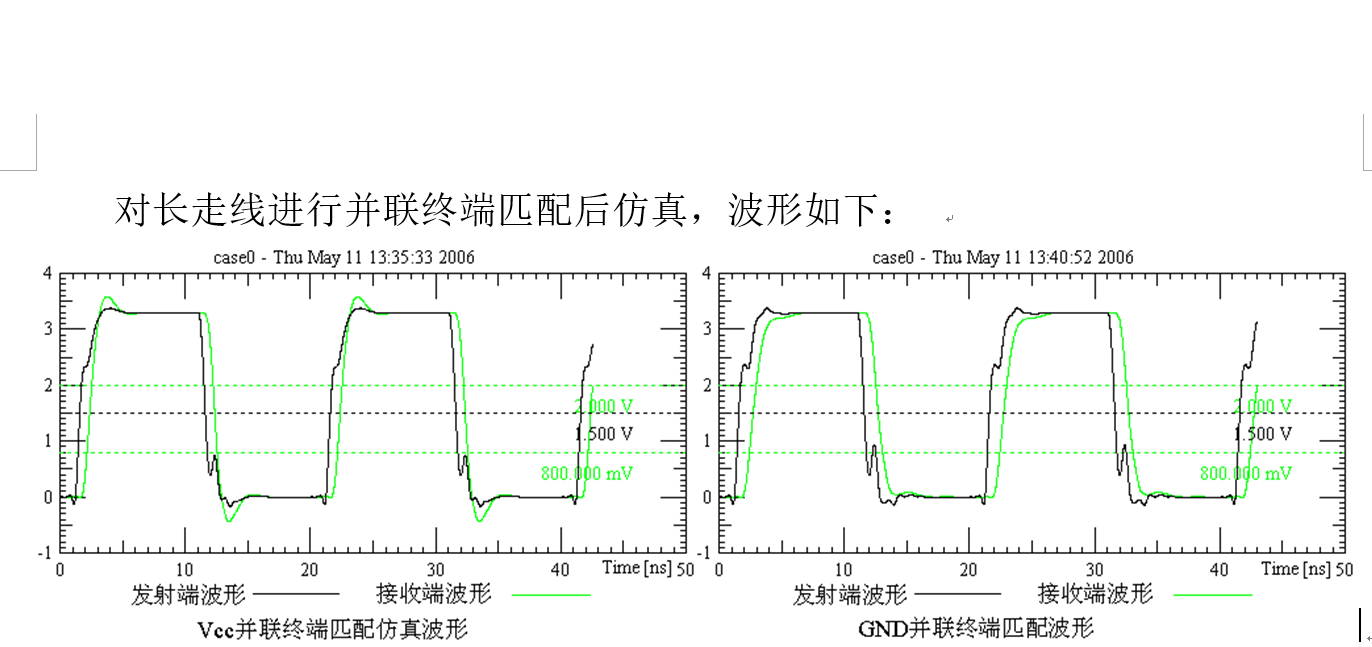

并联终端匹配是最简单的终端匹配技术:通过一个电阻R将传输线的末端接到地或者接到VCC上。电阻R的值必须同传输线的特征阻抗Z0匹配,以消除信号的反射。如果R同传输线的特征阻抗Z0匹配,不论匹配电压的值如何,终端匹配电阻将吸收形成信号反射的能量。终端匹配到VCC可以提高驱动器的源的驱动能力,而终端匹配到地则可以提高电流的吸收能力。

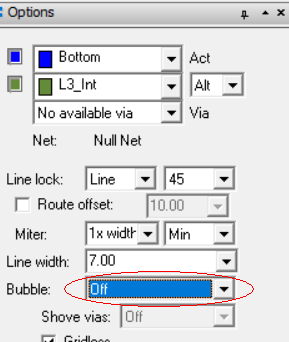

allegro在布线过程中,根据个人习惯有多种避让方式可以选择,不管采用那种方式,都需要经过优化才能使pcb布线更符合设计要求,推荐交叉使用以下方式进行布线。(1)使用off方式进行布线,可能导致很多DRC的产生,把网络连接好后,需要把DRC都消除掉。优化时需要把格点设小,使用微调推挤或重新布线方式,优点是布线可根据个人的意愿进行,布线速度快;缺点是优化时需要花费

电路磁珠的滤波机理

磁珠的外形与电感相似,其主要功能是吸收电源、信号上的噪声等干扰。请注意到“吸收”俩个字。电容本身就可以起到滤波作用,电感和电容配合也能起到滤波作用,但这种滤波,并没有真正的将噪声消除。例如,电容的滤波其原理是在高频时建立一条通往地平面的低阻抗通道,以便将噪声泄放到地平面。而电感和电容配合的滤波,其原理是构建成一个低通滤波器,是让频段比较低的信号顺利而衰减的通过,而阻断频段比较高的噪声,低通滤波器对高频噪声而言,近似一个极大的电阻。高频段噪声遇到这个极大的电阻,只能是被反射回去,基于该原理,应用低

我们在进行AD原理图绘制之后,都会对原理图进行编译检查。那么,当我们编译检查出现了“off grid at.....”的警告时,总是会摸不清头脑,为什么出现了这个警告?我应该怎么去消除这个警告?

茹贝尔震荡自激消除网络

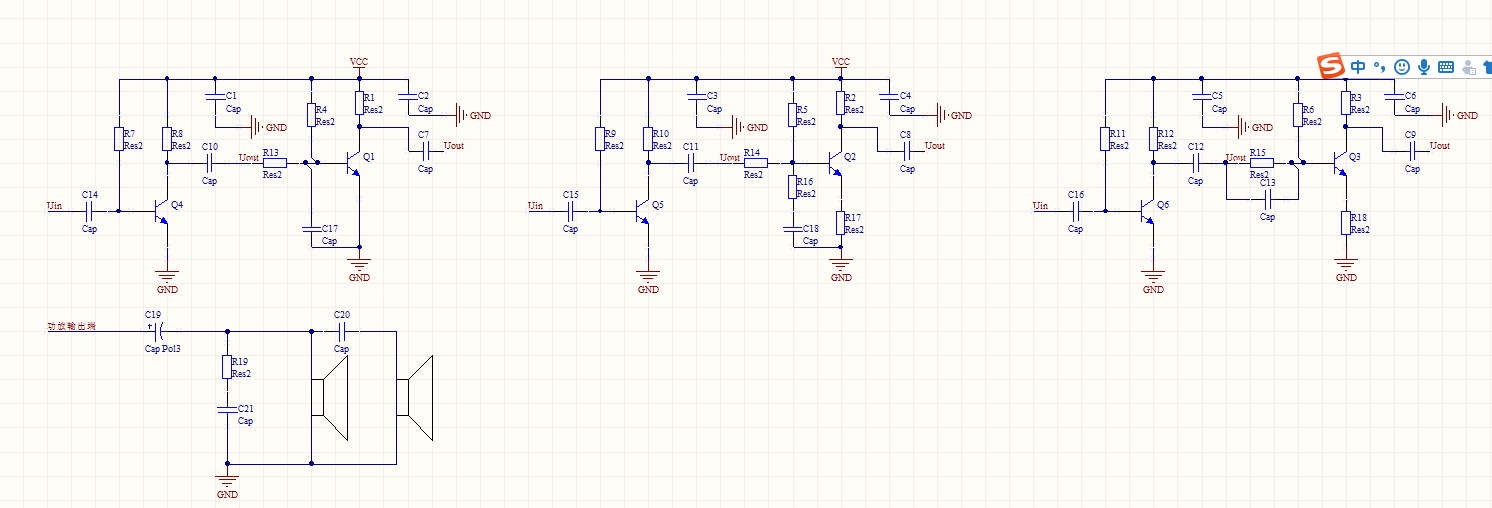

我们知道放大器电路中,无可避免的就是震荡自激的产生,而自激的来源首先是相位的颠覆所导致,什么意思呢?这是因为我们的运放电路所产生的电信号属于交变信号(模拟信号,比如正弦波)。有时候我们人为的随意加放Pf级别的电容和电阻所导致,最终产生相位偏移,而满足自我激励的另外一个条件就是幅度。

如何使用旁路电容器消除电源噪声-什么是电源噪声?你知道如何处理吗?想象一下,您已经设计了一个不错的运算放大器电路,并开始对其进行原型设计,但失望地发现该电路无法按预期工作或根本无法工作。造成这种情况的主要原因可能是来自电源或内部IC电路的噪声,甚至来自相邻IC的噪声可能已耦合到电路中。

答:浸银工艺介于有机涂覆和化学镀镍/浸金之间,工艺比较简单、快速;不像化学镀镍/浸金那样复杂,也不是给PCB穿上一层厚厚的盔甲,但是它仍然能够提供好的电性能。银是金的小兄弟,即使暴露在热、湿和污染的环境中,银仍然能够保持良好的可焊性,但会失去光泽。浸银不具备化学镀镍/浸金所具有的好的物理强度因为银层下面没有镍。 浸银是置换反应,它几乎是亚微米级的纯银涂覆。有时浸银过程中还包含一些有机物,主要是防止银腐蚀和消除银迁移问题;一般很难测量出来这一薄层有机物,分析表明有机体的重量少于1%。

答:过孔的两个寄生参数是寄生电容和寄生电感。过孔本身存在着对地的寄生电容,如果已知过孔在铺地层上的隔离孔直径为D2,过孔焊盘的直径为D1,PCB板的厚度为T,板基材介电常数为ε,则过孔的寄生电容大小近似可以用以下公式来计算:C=1.41εTD1/(D2-D1)。过孔的寄生电容会给电路造成的主要影响是延长了信号的上升时间,降低了电路的速度。比如说,对于一块厚度为50Mil的PCB板,如果使用内径为10Mil,焊盘直径为20Mil的过孔,焊盘与地铺铜区的距离为32Mil,则我们可以通过上面的公式近似

答:端接,Butt Joint,是指消除信号反射的一种方式。在高速PCB设计中,信号的反射将给PCB的设计质量带来很大的负面影响,采用端接电阻来达到线路的阻抗匹配,是减轻反射信号影响的一种有效可行的方式。端接,分为一下两类:Ø 源端端接,接在信号源端或信号发送端的端接,一般与信号走线串接;Ø 终端端接,接在信号终端或信号接收端的端接,一般与信号走线并接。源端端接的优点是接供较慢的上升时间,减少反射量,产生更小的EMI,从而降低过冲,增加信号的传输质量。我们在PCB设计中处理源

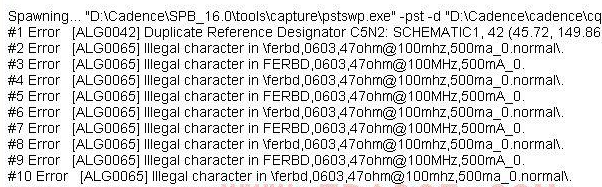

答:orcad当前设计中,所用到库在原理图页面下方的Design Cathe里,在绘制原理图时,可能很多部分是从别的原理图拷贝而来,所以Design Cathe中就会存在一些非法字符,从而影响网表的输出,我们就需要将Design Cathe中的非法字符消除,消除的步骤如下:第一步,点击菜单File→New Library,新建一个库在当前设计的路径下,注意保存的时候不要在路径上出现非法字符,如含有括号、百分号等;第二步,在Design Cathe中找到库路径中含有非法字符的那个库文件,选中库文件

扫码关注

扫码关注