- 全部

- 默认排序

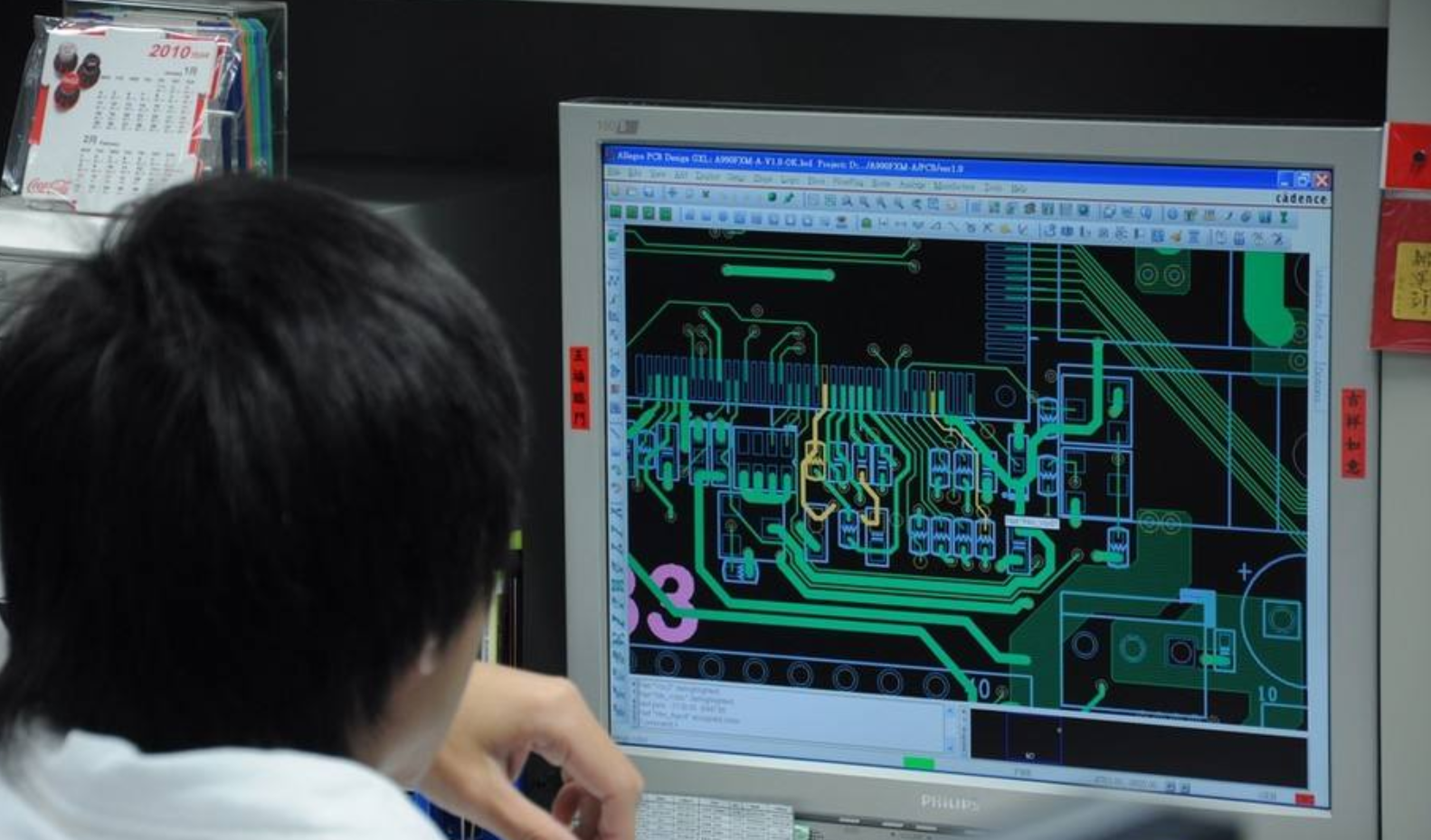

电子产品设计的基本流程包括项目启动,市场调研,项目规划,项目详细设计,原理图设计,PCB布局、布线,PCB制板、焊接,功能、性能测试等环节,我们在教学过程中,一般按下面的步骤进行电子产品设计:第一步:获取产品需要实现的功能;

现在越来越多的高速设计是采用一种有利于加快开发周期的更有效的方法。先是建立一套满足设计性能指标的物理设计规择,通过这些规则来限制PCB布局布线。在器件安装之前,先进行仿真设计。在这种虚拟测试中,设计者可以对比设计指标来评估性能。而这些关键的前提因素是要建立一套针对性能指标的物理设计规则,而规则的基础又是建立在基于模型的仿真分析和准确预测电气特性之上的,所以不同阶段的仿真分析显得非常重要。

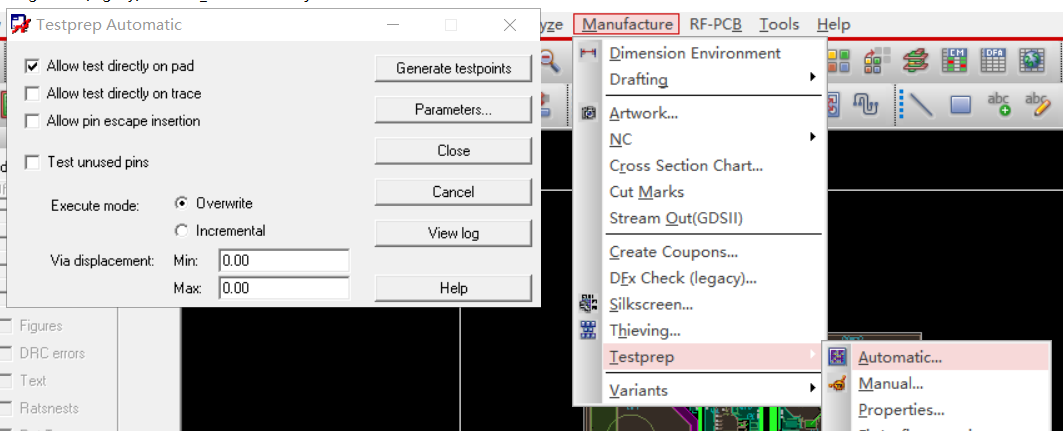

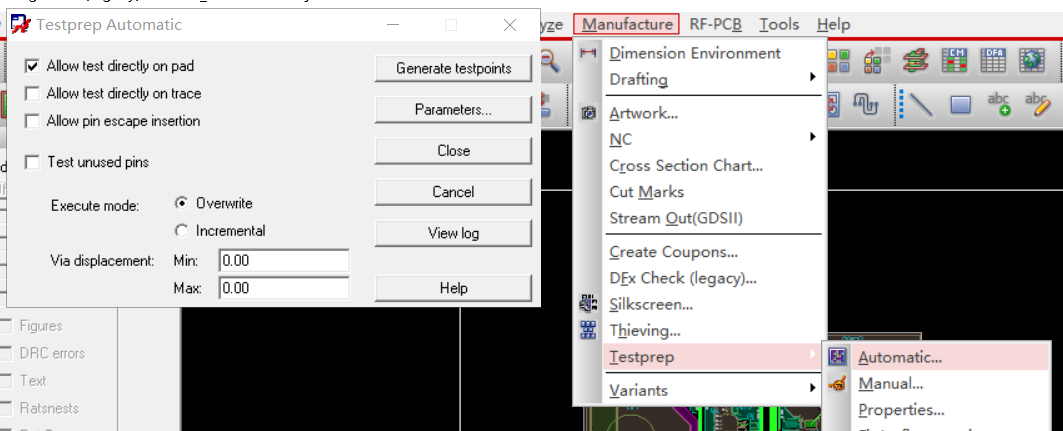

cadence allegro Allow test directly on pad:允许测试点在焊盘上,允许时将自动替换已有的过孔。Allow test directly on trace:允许测试点在信号线上,允许时测试点可以直接在信号线上。Allow pin escape insertion:允许从引脚上自动引出测试点。Test unused pins:无网络引脚添加测试点。

某行车记录仪,测试的时候要加一个外接适配器,在机器上电运行测试时发现超标,具体频点是84MHz、144MHz、168MHz,需要分析其辐射超标产生的原因,并给出相应的对策。辐射测试数据如下:

[导读] EMC( Electromagnetic Compatibility) 电磁兼容性对于一个产品而言是一个非常重要的性能指标,一个产品遇到EMC的坑,很多测试很难通过,很多软件同学可能会觉得EMC更多的是硬件攻城师要去应对的难题,与软件没毛关系。

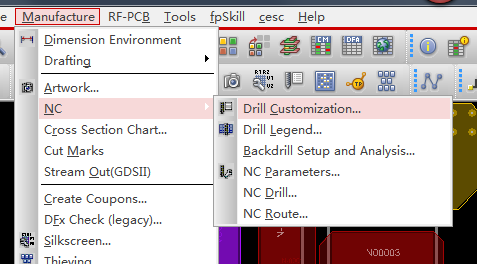

钻孔表格的设置与生成

任何pcb设计文件设计完成后,都需要通过相关功能输出生成所需要的文件资料,allegro软件的功能确保了pcb的设计数据与成产文件完全一致,从而可以直接在设计界面中输出所有pcb生产、测试、装配所需的文件,以下要将的是pcb钻孔表格的设置与生成

电磁兼容故障诊断与整改

电磁兼容故障诊断与整改是一项复杂的系统工程,主要表现在其故障现象多样,产品的电气、结构、材料、设计等诸多影响因素相互关联,整改手段差异性很大,对技术人员能力要求较高,所以需要丰富的设计经验和良好的测试能力作为保证。往往结果就是很小的一个因素,但需要经历曲折的过程。

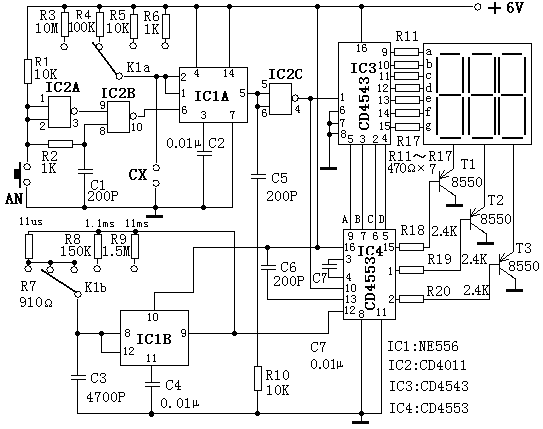

三位数字显示电容测试表

广大电子爱好者都有这样的体会,中、高档数字万用表虽有电容测试挡位,但测量范围一般仅为1pF~20mF,往往不能满足使用者的需要,给电容测量带来不便。本电路介绍的三位数显示电容测试表采用四块集成电路,电路简洁、容易制作、数字显示直观、精度较高,测量范围可达1nF~104mF。特别适合爱好者和电气维修人员自制和使用。

扫码关注

扫码关注