- 全部

- 默认排序

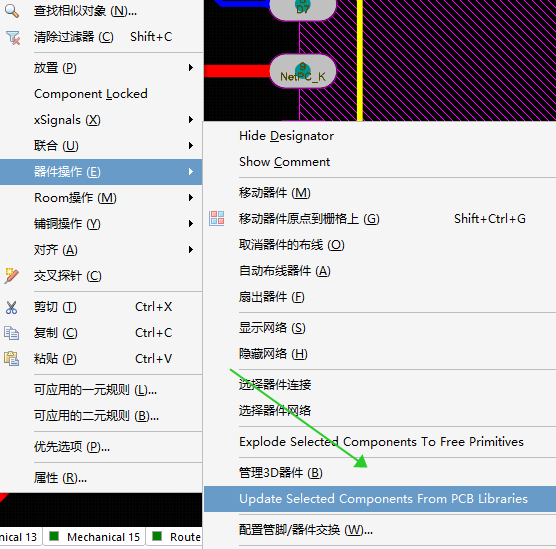

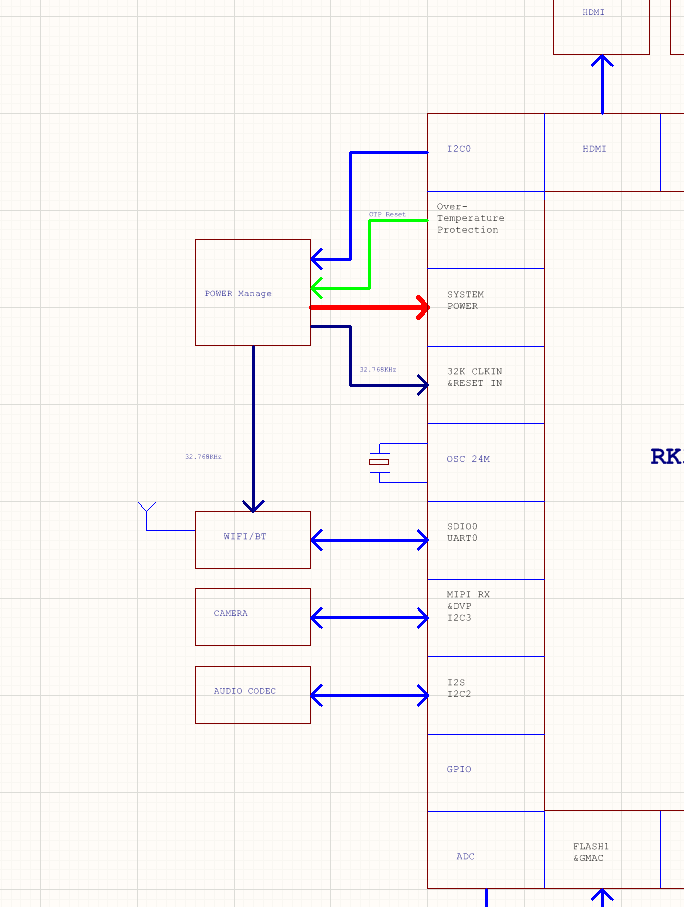

在项目实际的设计中我和小伙伴一样都遇到过很多麻烦的问题,有些时候原理图和PCB设计可能是由不同的工程师负责,由于种种原因可能需要在没有原理图的情况下直接对PCB进行操作。如更新元件封装和增加与删除元件等操作。接下来我们一起学习

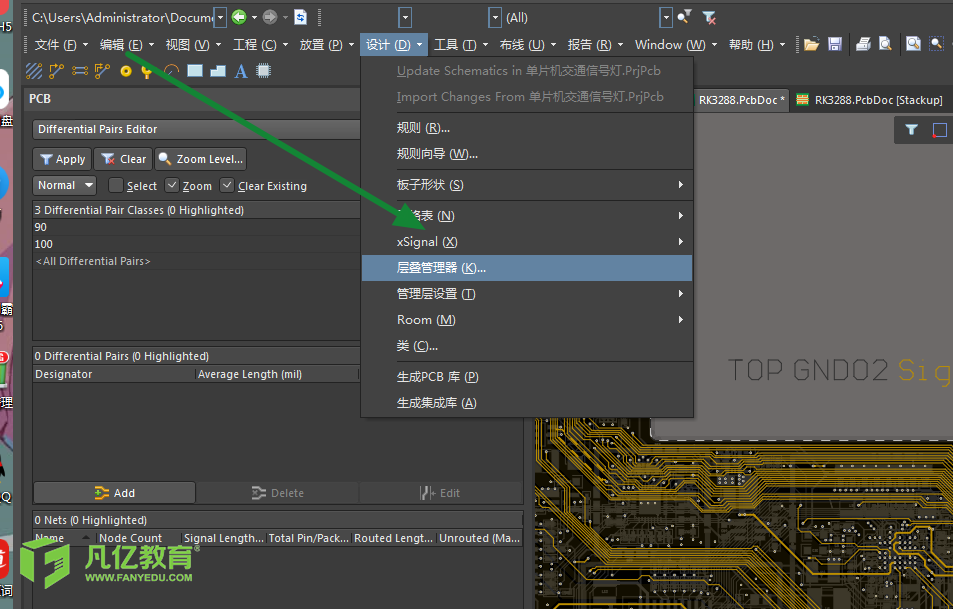

对于AD爱好者来说,每一次的版本更新都是新功能的添加和旧功能的优化或者是移除,在新版AD19在内电层内缩pullback进行了位置变化,同时内电层改变内缩还相邻的内缩会一起变动。

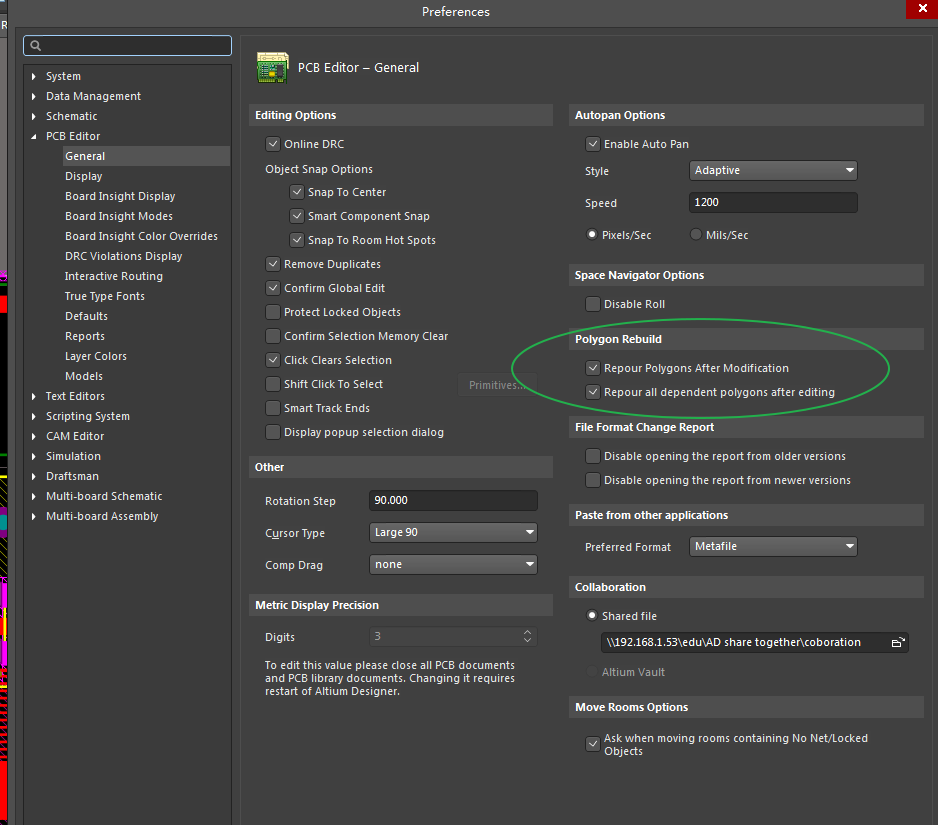

高版本中,我们进行动态铜皮的自动更新,那么如何进行设计,如果想实现自动在铜皮里面进行铜皮避让,首先你的电脑必须是高配置,不然有可能就会出现铜皮自动避让,从而出现卡机的现象。

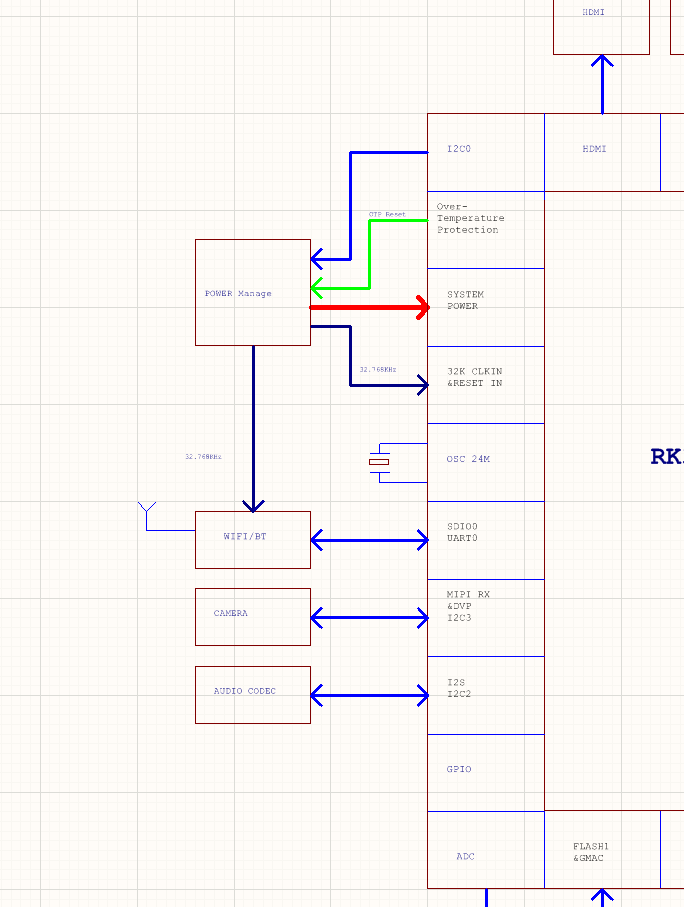

Ad19由于做了更新的改动,所以我们对应的RB就不能进行管脚的查看,首先我们点击我的PCB界面,然后我们点击我们的PCB的空白处,我们点击一下,然后我们对应在我们的panel 面板下面调用出我们的proprieties这个界面,这个和低版本不一样之处在于,高版本将prorieties这个界面替代了我们的PCB Inspertor.

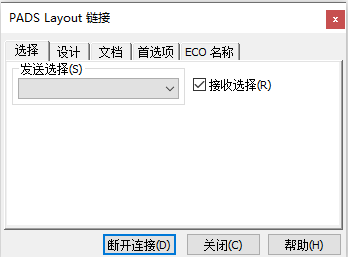

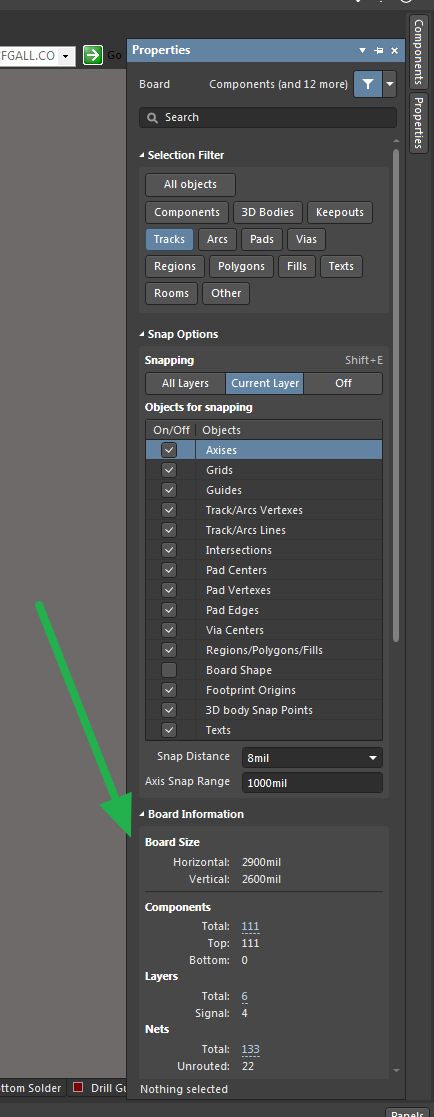

在PCB设计时,会根据PCB设计的一些情况,设置相对应的规则和区域,但是因为原理图这种没有设置,在原理图和PCB对比更新时不能把这些规则和区域去掉

扫码关注

扫码关注