- 全部

- 默认排序

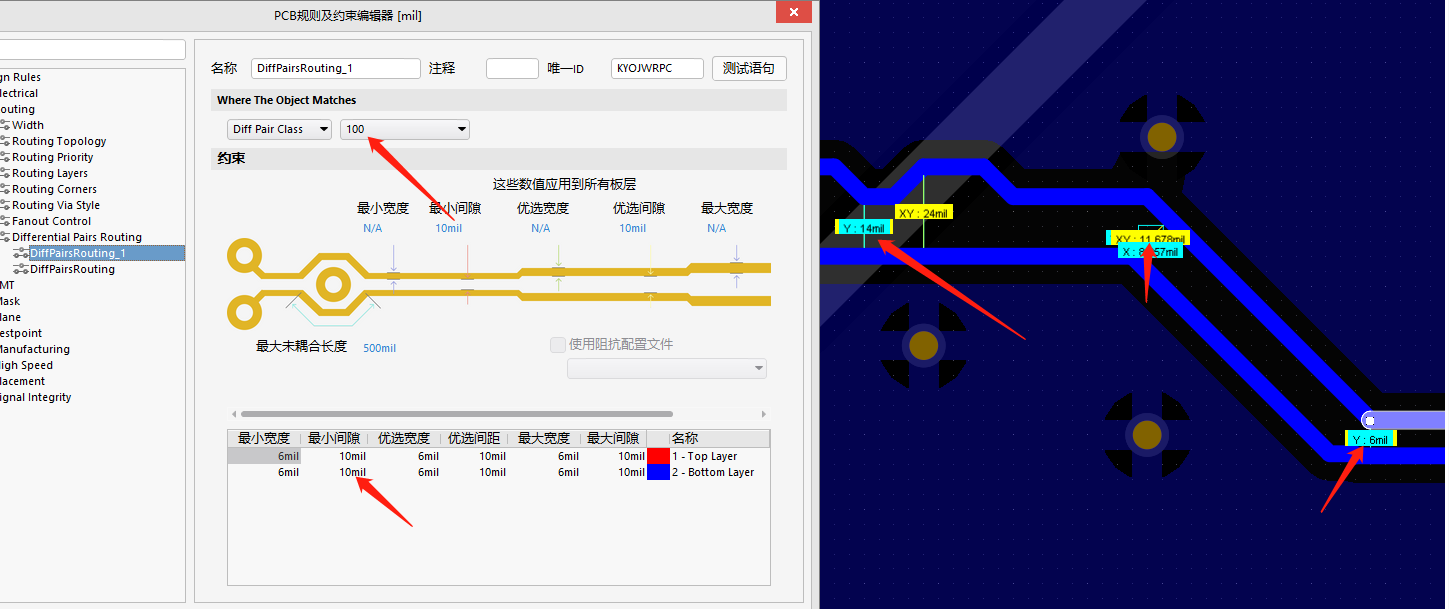

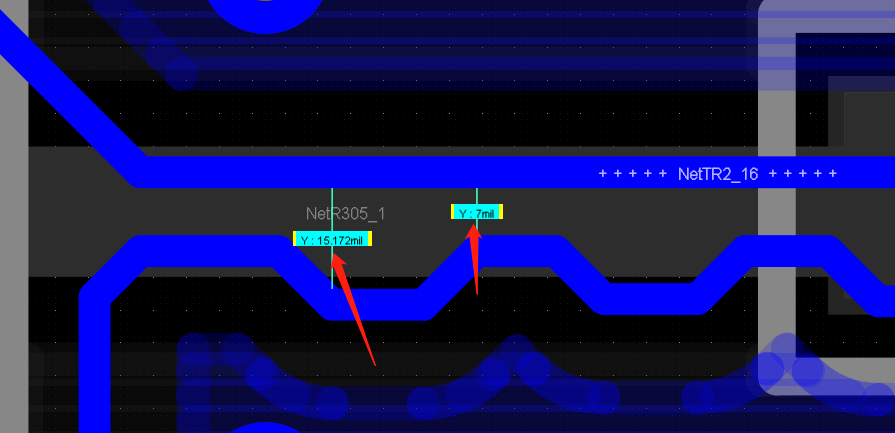

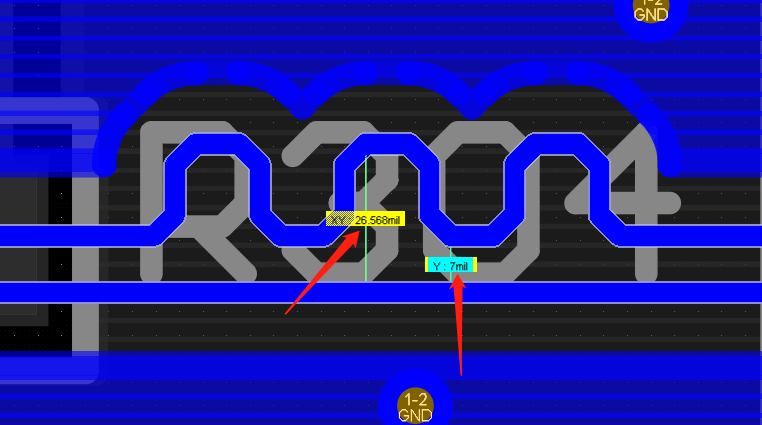

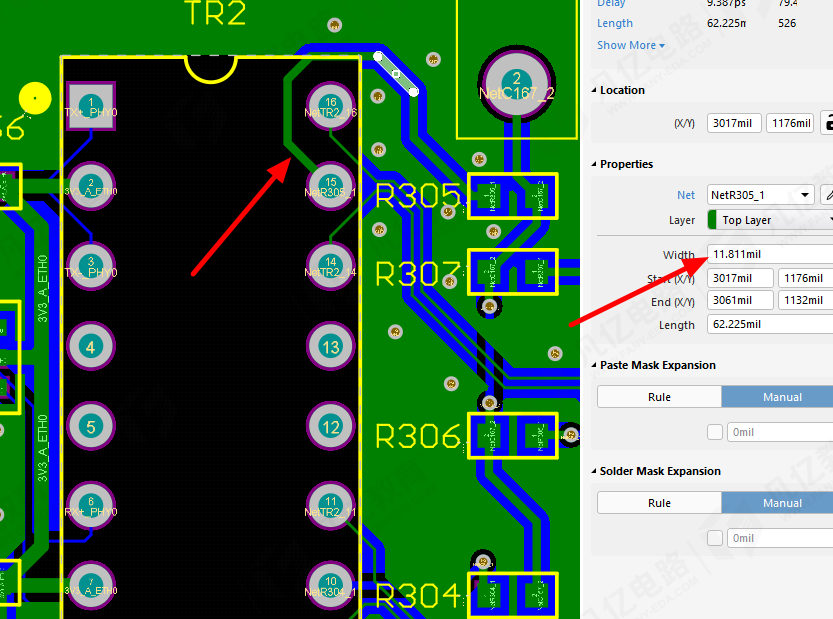

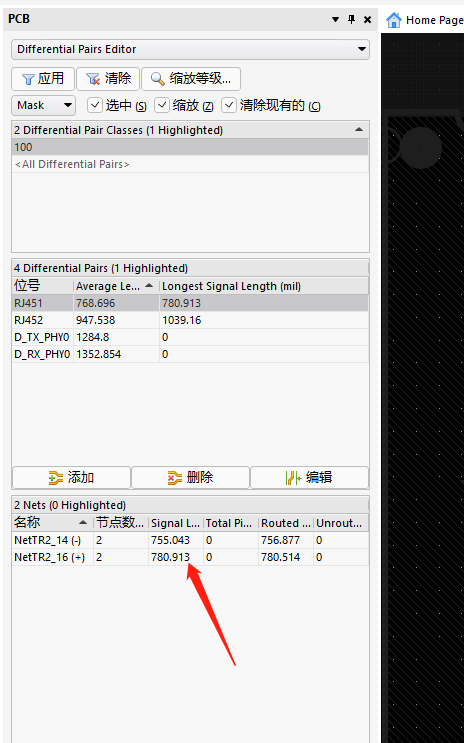

差分走线不符合规范,要按照差分阻抗线宽线距进行走线2.对内等长凸起高度不能超过线距的两倍3.差分走线需要在优化一下4.此处存在短路5.存在多处开路6.一层连通不用打孔,差分要按照阻抗线距走线7.时钟信号尽量单根包地处理8.差分对内等长误差5

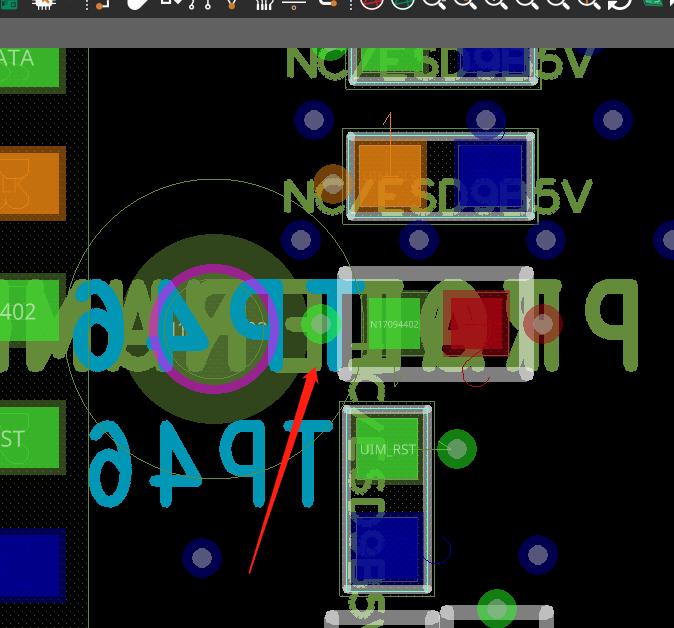

SIM:注意测试点跟器件以及过孔的间距,此处右侧器件可以整体往右边挪动一点:注意铜皮尽量设置动态铜皮,将静态转换下:电感内部挖空掉,在当前层:TF:注意器件之间可以空出点间距留出来扇孔,扇孔不要离焊盘太远:时钟信号包地保全一点,还有 空间可

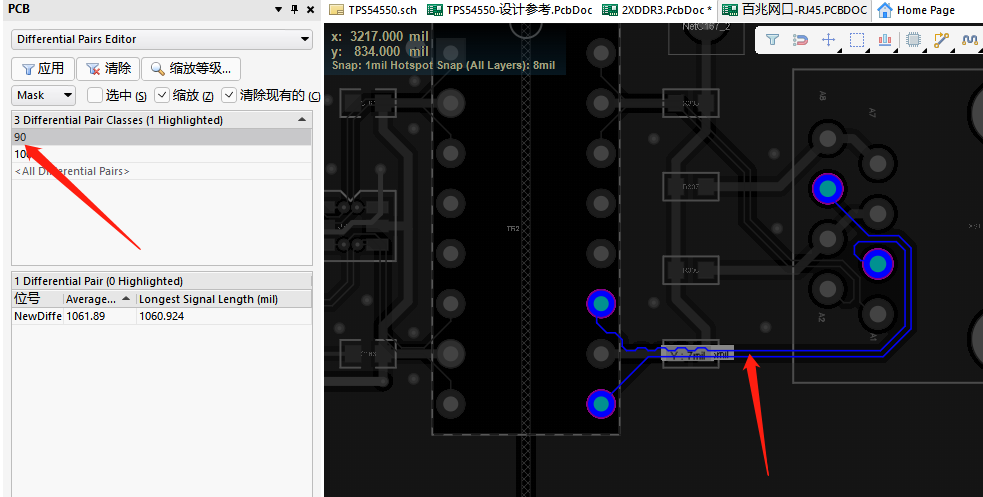

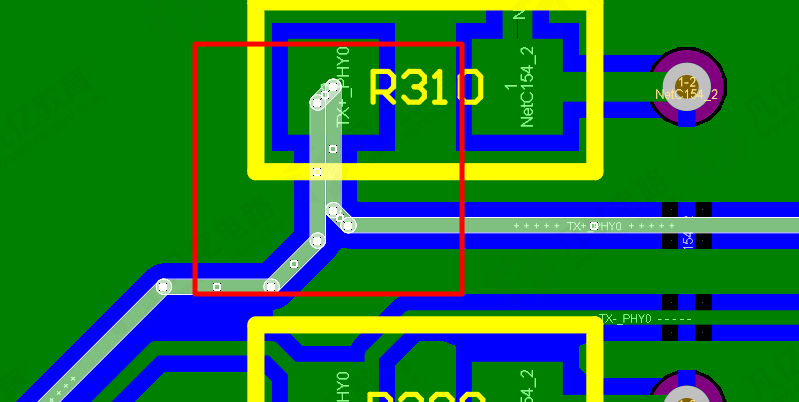

网口差分控100欧姆,不是90,加后期自己注意一下2.差分对内等长误差5mil3.差分出线要尽量耦合走线不要超过焊盘宽度,建议与焊盘同宽,自己调整一下5.时钟信号需要包地处理,在地线上均匀的打上过孔蛇形等长建议用钝角以上评审报告来源于凡亿教

差分对内等长凸起捣鼓不能超过线距的两倍2.差分出线可以在优化一下3.此处走线可以从焊盘拉出后子啊进行加粗处理4.差分对内等长误差5mil时钟信号需要单根包地处理,或者离其他信号20mil以上评审报告来源于凡亿教育90天高速PCB特训班作业评

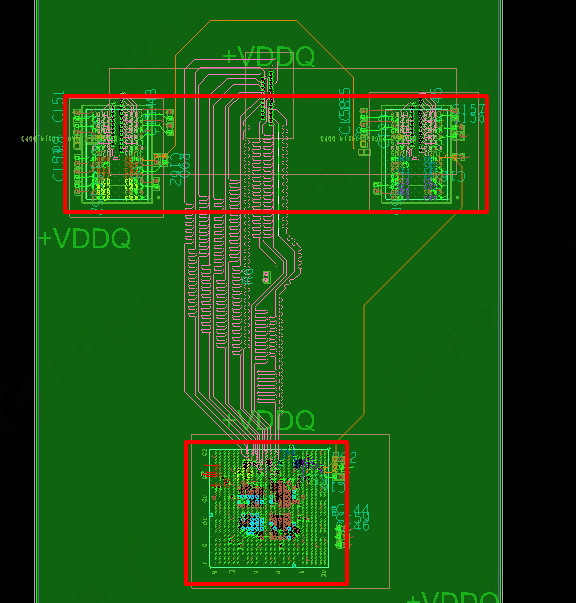

ddr之间ddr和芯片距离太远,ddr到芯片推荐600-800mil器件摆放太近丝印干涉,滤波电容推荐摆放到ddr背面靠近焊盘放置 过孔上焊盘,小器件焊盘尽量不要打孔到焊盘上差分线是主要时钟信号,尽量缩短走线电容靠近ddr中间放置差分线等长

在现场可编程门阵列(FPGA)设计中,复位机制是非常重要,正确选择和应用复位策略可确保系统的稳定性和可靠性,本文将深入探讨这些复位机制,希望对小伙伴们有所帮助。1、如何区分同步复位和异步复位?同步复位和异步复位的区别是:它们与主时钟信号的关

注意差分对内等长凸起高度不能超过线距的两倍差分尽量哪里不耦合就在哪里绕,尽量不要在中间绕蛇形2.差分出线需要耦合,后期自己调整一下3.走线尽量不要有锐角,后期自己优化一下4.时钟信号需要包地处理,并在地线上打孔,建议50-100mil一个以

差分连接焊盘走线不要重叠、锐角,两边保持一致变压器除差分走线以外其他所有走线加粗到20mil以上差分走线尽量耦合差分走线出焊盘尽快耦合保持长度一致时钟信号包地打孔处理rx、tx分别建立等长组控制100mil误差分别等长走线应连接到焊盘中心,

变压器除差分以外所有走线加粗到20mil多处走线锐角,尽量避免走线、铺铜锐角多处尖岬铜皮、孤岛铜皮,器件中间多余尖细铜皮挖空处理时钟信号包地打孔处理差分对内控制5mil误差等长以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解

网口差分需要进行对内等长,误差5mil2.走线需要优化一下,尽量不要出现直角3.差分出线要尽量耦合4.差分焊盘出线尽量从四角出线,后期自己优化一下5.差分需要按照阻抗线宽线距走线,避免后期造成阻抗突变6.存在多处drc7.时钟信号包地,尽量

扫码关注

扫码关注