- 全部

- 默认排序

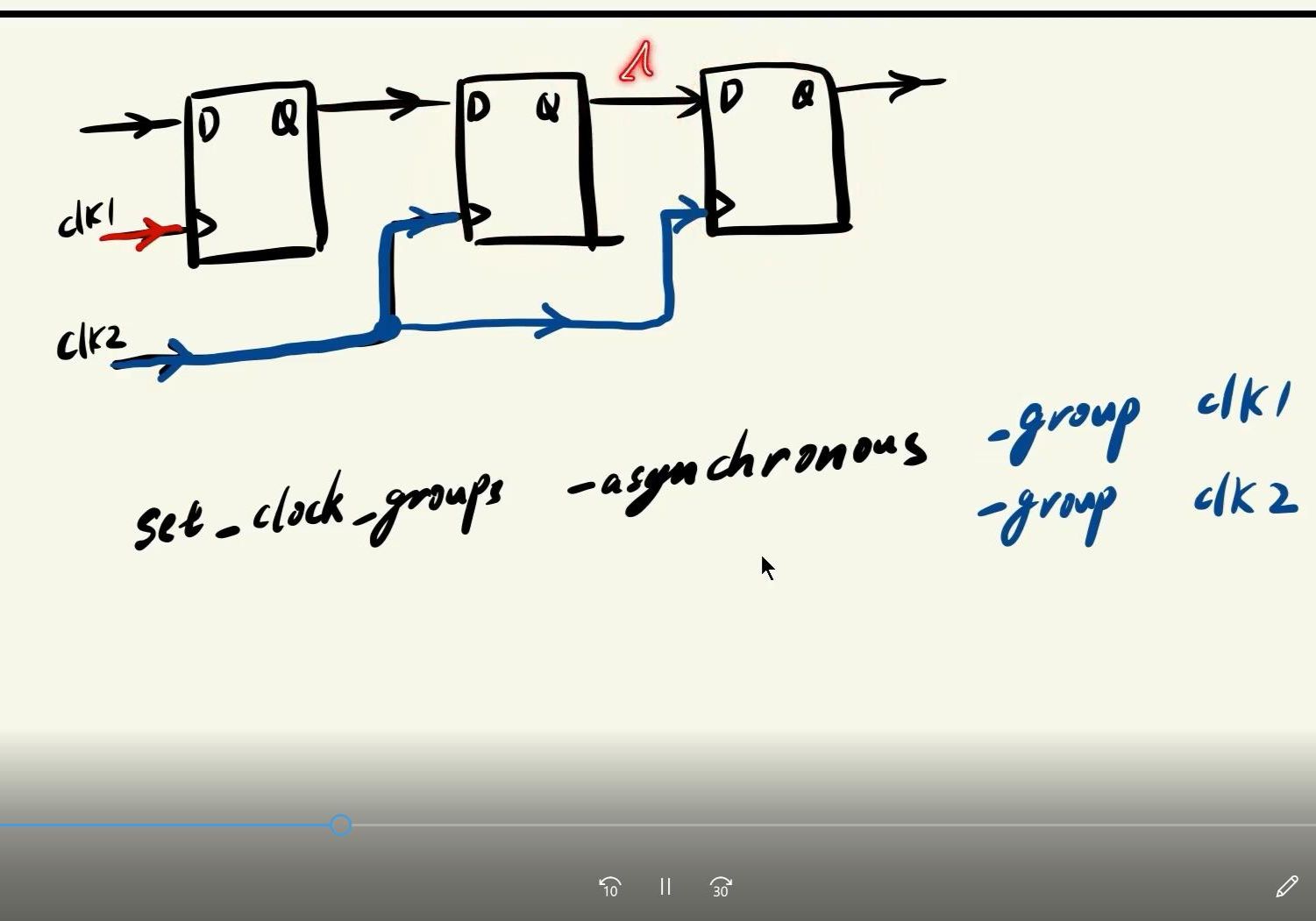

电平信号的跨时钟处理

跨时钟域信号的验证要点

深圳晶振电路的PCB设计

我们常把晶振比喻为数字电路的心脏,这是因为,数字电路的所有工作都离不开时钟信号,晶振直接控制着整个系统,若晶振不运作那么整个系统也就瘫痪了,所以晶振是决定了数字电路开始工作的先决条件。 我们常说的晶振,是石英晶体振荡器和石英晶体谐振器两种,他们都是利用石英晶体的压电效应制作而成。在石英晶体的两个电极上施加电场会使晶体产生机械变形,反之,如果在晶体两侧施加机械压力就会在晶体上产生电场。并且,这两种现象是可逆的。利用这种特性,在晶体的两侧施加交变电压,晶片就会产生机械振动,同时产生交变电场。这种震

往往说晶振是数字电路设计的关键,便是由于全部的数字电路设计都需要一个好的工作时钟信号,最普遍的便是用晶振来处理,可以说要是有数字电路设计的地方就可以看到晶振。 大家常说的晶振,包括两种,一种需要加驱动电路才可以产生频率信号,这类晶振叫晶振谐振器,例如普遍的49S封装、两脚封装的SMD32255032、小量四脚SMD封装。一种无需加驱动电路,只需要再加工作电压信号,就可以产生频率信号,这类称为晶振振荡器,大部分全是4脚封装,带有开关电源脚位、地脚位、频率輸出脚位等。

至于USB,SATA,PCIE等串行信号,并没有上述并行总线的时钟概念,其时钟是隐含在串行数据中的。数据发送方时钟包含在数据中发出,数据接收方通过接受到的数据恢复出时钟信号。这类串行总线没有上述并行总线等长布线的概念。但因为这些串行信号都采用差分信号,为了保证差分信号的信号质量,对差分信号对的布线一般会要求等长且按总线规范的要求进行阻抗匹配的控制

SDRAM芯片引脚介绍

以 Micron公司容量为512Mb(512兆位),规格为8M×16×4的某款 SDRAM为例,介绍 SDRAM的引脚定义。(1) CLK:时钟信号,为输入信号。 SDRAM所有输入信号的逻辑状态都需通过CLK的上升沿采样确定。(2) (2)CKE:时钟使能信号,为输入信号,高电平有效。CKE信号的用途有两个,其是关闭时钟以进入省电模式,其二是进入自刷新( SELF REFRESH)状态。CKE无效时,SDRAM内部所有与输入相关的功能模块停止工作。在电路设计中需注意,应为C

答:orcad创建封装库时,放置管脚的Shape的含义是管脚的长度以及一些特殊含义,其表示的含义解释如下:Clock:时钟信号,管脚的长度是标准长度;Dot:低电平有效信号,管脚的长度是标准长度;Dot-Clock:低电平有效的时钟信号,管脚的长度是标准长度;Line:普通信号,管脚的长度是标准长度;Short:普通信号,管脚的长度比标准的长度要短一些;Short Clock:时钟信号,管脚的长度比标准的长度要短一些;Short Dot:低电平有效信号,管脚的长度比标准的长度要短一些;Short

扫码关注

扫码关注