- 全部

- 默认排序

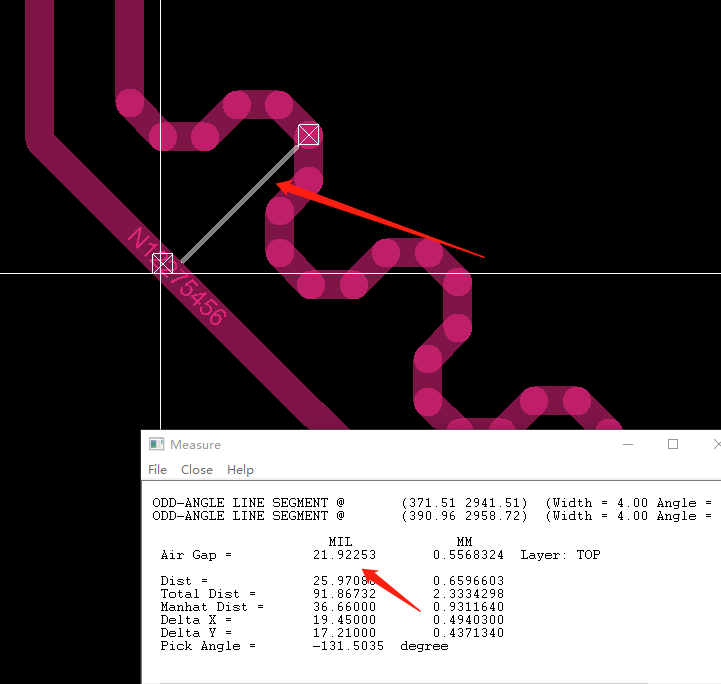

一、产品问题描述某车载产品进行EMC测试,发现1.6GHZ处超标,不能满足标准要求。① 远场测试图 图 1 远场测试图② 测试结果注:由上图测试结果可见,受测样机辐射发射骚扰测试在1600MHz频点存在超标情况,超标数值为5.34DB。二、定位与初步分析经与客户沟通得知样机内DDR通讯的时钟信

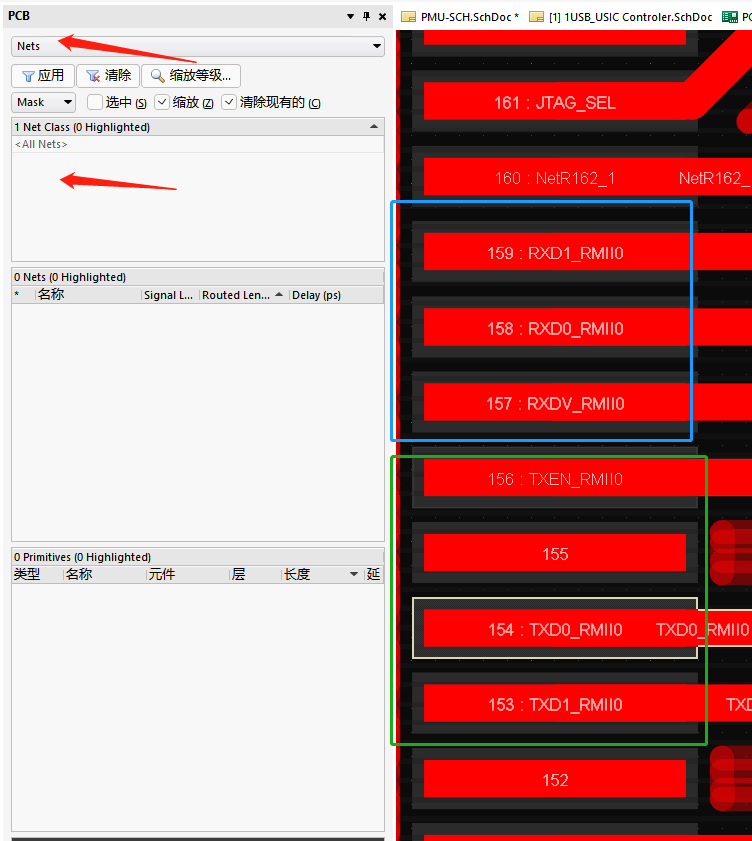

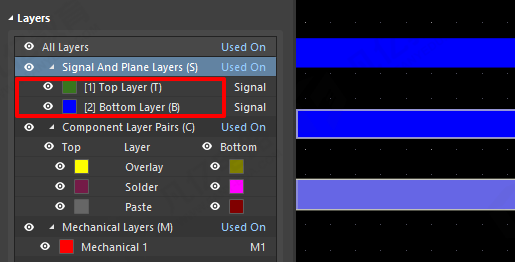

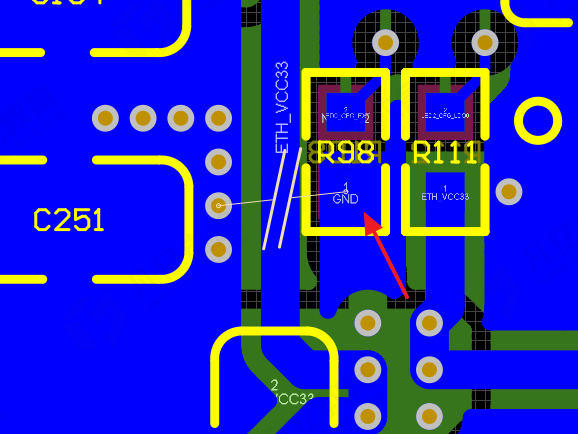

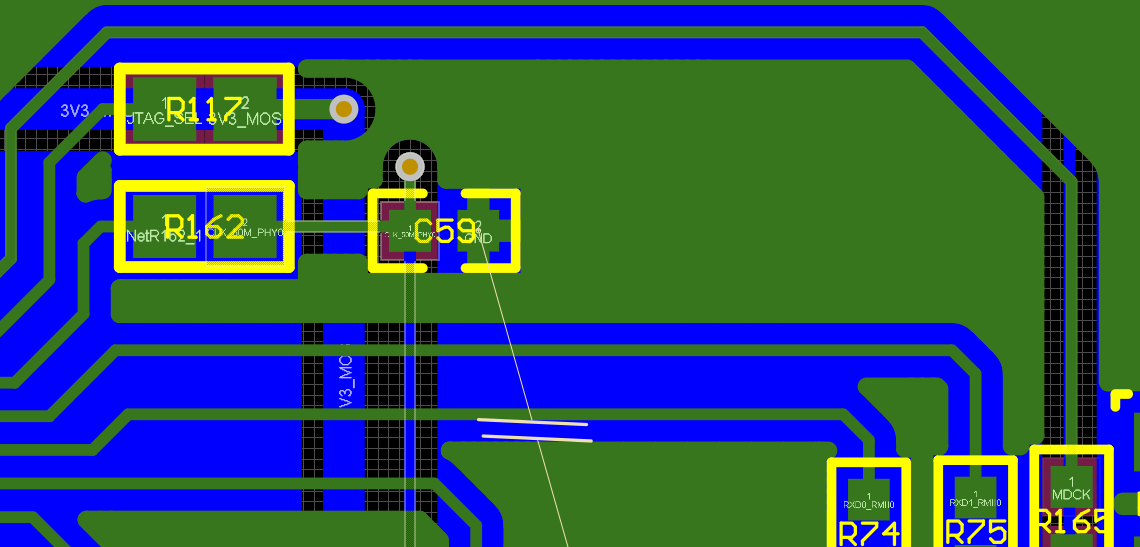

未创建TX和RX的class,分别等长误差100mil2.时钟信号要进行连通并包地处理3.焊盘出现需要优化一下4.变压器所有层需要挖空处理5.差分对内等长误差5mil6.差分出线要尽量耦合7.没有添加差分对的class8.pcb上存在多处开

1.线宽要保持一致,线宽不一致会导致阻抗不连续。2.TF卡的时钟信号,与其他信号线的间距保证20mil左右,有空 间的情况下,包地处理。3.数据线等长错误,避免绕90度角等长。4.铺铜存在多处孤岛铜和尖岬铜皮以上评审报告来源于凡亿教育90天

1,焊盘有开路。2.pcb存在drc4.多处孤岛铜皮和尖岬铜皮4.走线保持3w间距4.走线避免锐角5.差分换层旁边要打地过孔6.晶振布线错误,晶振的一对线要走成类差分的形式,并整体包地处理, 线尽量短如下图8.同层连接不需要打孔9.时钟线要

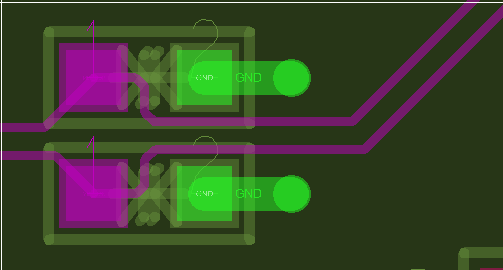

1.存在开路,孤岛铜皮没有连接出去。2.芯片中间过孔没有连接出去导致天线报错。3.多处孤岛铜皮和尖岬铜皮。4.电容地网络要和电源一样加宽载流。5.差分焊盘出线尽量耦合6.差分走线不耦合7.时钟信号走线要包地处理8.走线尽量短9.TX、RX没

高速PCB设计在现代电子产品中越来越重要,而高速信号的传输问题也日益成为PCB工程师面临的问题之一,那么在高速PCB设计中如何解决高速信号传输中的问题?也许本文能给你一些参考。一般来说,高速信号传输中会出现多种问题,如时钟抖动、时序失真、瞬

锯齿状等长不能超过线距的两倍2.线宽尽量保持一致3.时钟要靠近管脚放置,并且包地处理4.走线也不规范,需要优化一下5.此处电源不满足载流6.TX和RX需要添加class,并进行等长处理,误差100mil7.TX,RX之间需要走一根20mil

这个差分需要优化一下。这里过孔打到焊盘上了晶振需要包地处理走线也要走类差分变压器这里的走线除了差分都要大于20mil时钟要包地处理这里等长不要有直角长度也要大于3w以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班

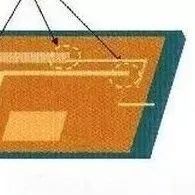

随着信号上升沿时间的减小,信号频率的提高,电子产品的EMI问题,也来越受到电子工程师的重视。高速pcb设计的成功,对EMI的贡献越来越受到重视,几乎60%的EMI问题可以通过高速PCB来控制解决。1高速信号走线屏蔽规则如上图所示:在高速的PCB设计中,时钟等关键的高速信号线,走需要进行屏蔽处理,如果

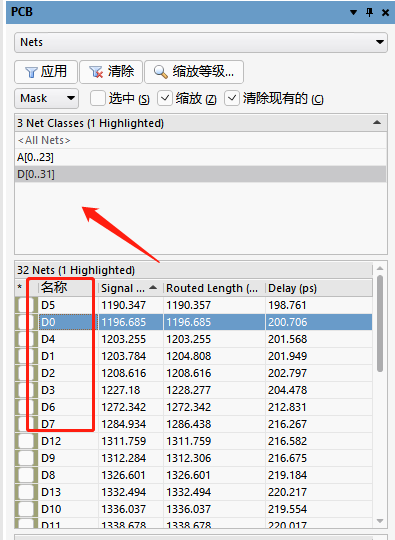

数据线高八位和低八位要分别进行分组等长,一组9根2.地址线等长不符合原理图要求3.等长注意一下不要有直角4.地址线分组需要把时钟信号,读写,控制都添加进来以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访

扫码关注

扫码关注