- 全部

- 默认排序

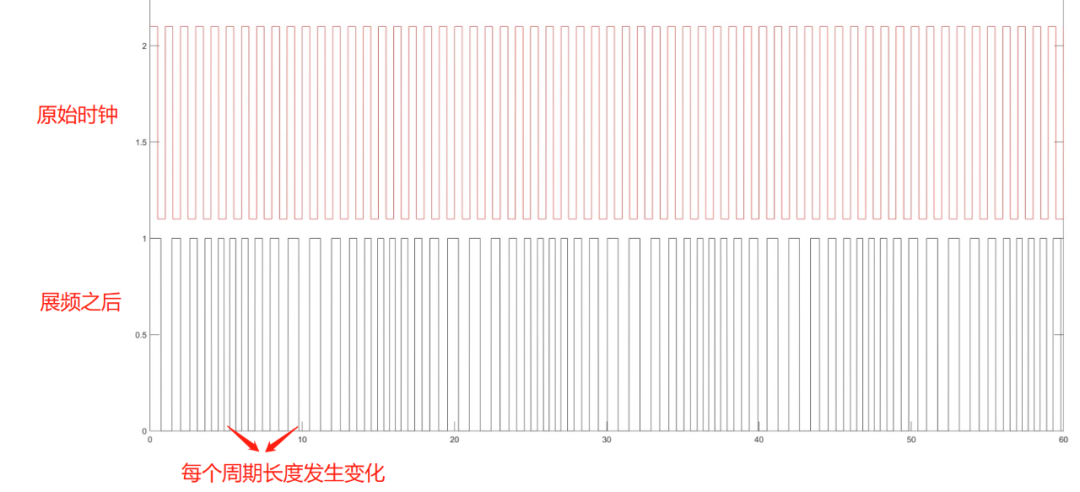

先前我们说了说:为什么时钟信号比数据信号更容易引起辐射超标?为什么时钟信号比数据信号更容易引起辐射超标?并且做了试验,如果认真看过的话,就会明白,周期性的信号是窄带频谱,特定的频率的幅值会很高,这对认证测试来说非常的不利。而一般时钟信号都是周期信号,这在电路中是少不了的。有没有什么办法,改造下时钟的

如何计算CAN通信波特率

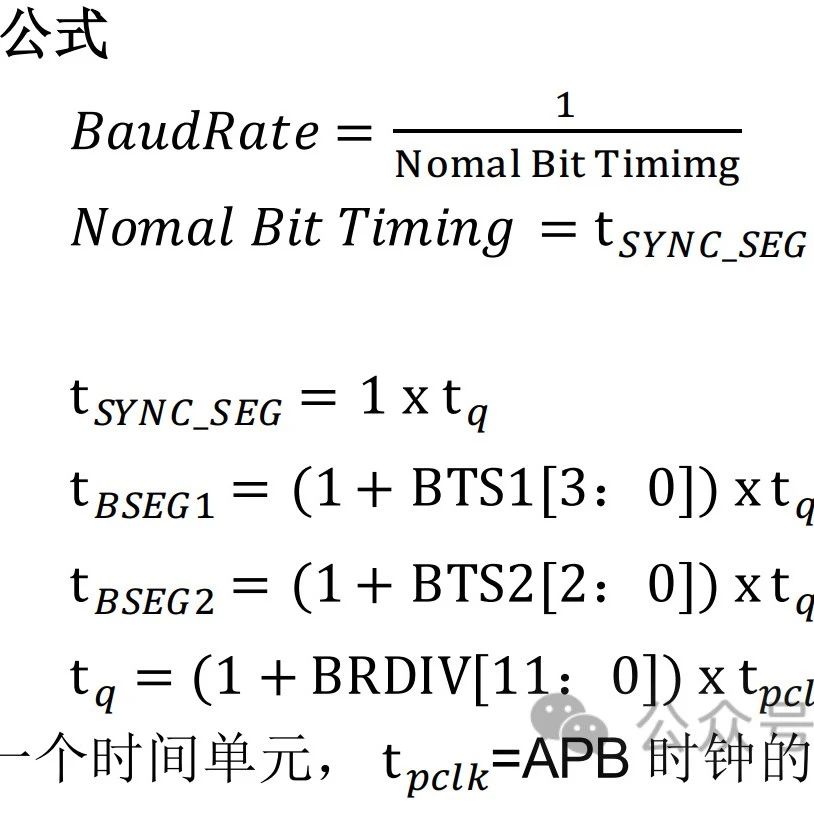

在CAN总线系统中,波特率的计算是一个关键步骤,它确保网络上的所有设备能够以相同的速率进行通信。1、理论波特率的计算涉及到几个关键参数,包括CAN控制器的时钟频率、分频因子、以及位时间的不同部分。时钟频率(Fclk)CAN控制器的时钟频率。这是CAN模块的输入时钟,通常来自于微控制器的主时钟。分频因

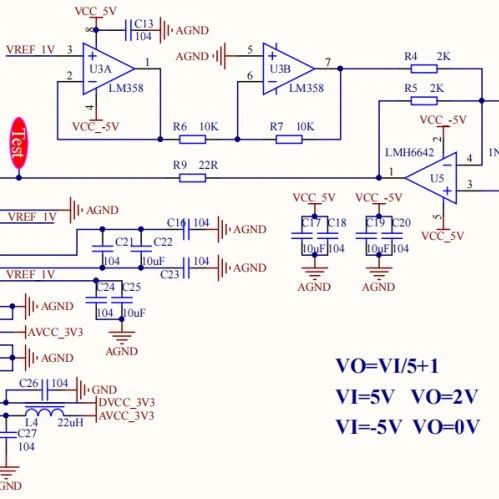

AD9280 在时钟(CLK)的驱动下工作,用于控制所有内部转换的周期;AD9280 内置片内采样保持放大器(SHA),同时采用多级差分流水线架构,保证了 32MSPS 的数据转换速率下全温度范围内无失码;AD9280 内部集成了可编程的基准源,根据系统需要也可以选择外部高精度基准满足系统的要求。A

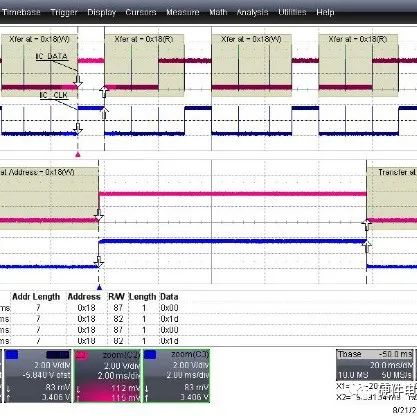

IIC接口—规范硬件信号测试1.测试指标说明 IIC总线根据时钟速率的不同分标准模式、快速模式和高速模式三种,测试中需根据实测的结果选择相应的测试指标作为判断的依据。测试内容主要包括以下两个方面: 信号完整性:SCL、SDA; 信号时序:tHD;STA、tSU;STO、tSU;D

【摘要】本文结合某单板(下文中统一称M单板)FPGA调试过程中发现地弹噪声造成某重要时钟信号劣化从而导致单板业务丢包的故障,来谈下如何最大程度地降低地弹噪声对单板信号完整性影响。一、故障现象M单板在进行业务调试时发现:如果只有上行方向有业务,上行业务正常无丢包;如果只有下行方向有业务,下行业务也正常

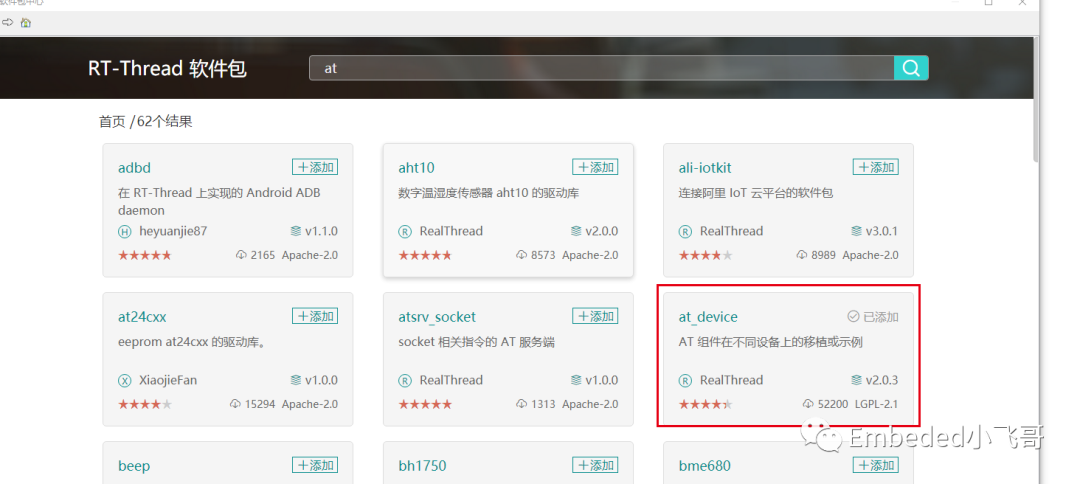

继上次的OLED显示开发之后,觉得RTT的平台挺好玩的,图形化配置,容易上手,这次在上次OLED显示的基础之上,增加ESP8266获取网络时间,同步网络时间并利用模拟RTC模块,做一个精巧的小时钟,ART-PI核心板板载有WIFI模组的,AP6212A ,wifi,蓝牙一体的模块,后面会开发板载模块

在微控制器中,STM32F103功能强大,应用广泛,要想确保STM32F103的系统稳定运行及性能优化,其时钟系统的配置更是不可缺少,所以如何配置?1、时钟源的选择HSI:内部RC振荡器,频率为8MHz,适用于对时钟频率精度要求不高或产品体

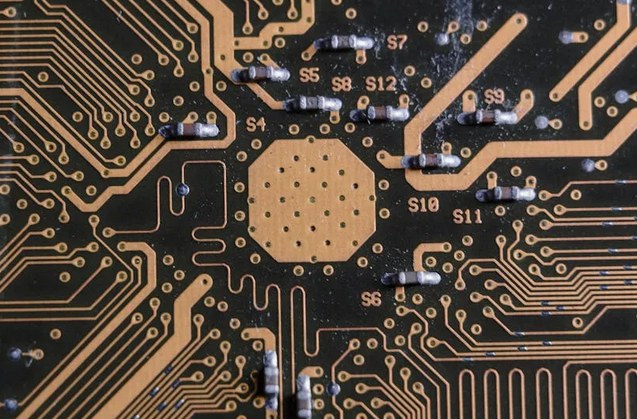

数字IC芯片的外围电路设计是确保芯片正常、高效运行的关键环节。它涉及到芯片与外部环境的接口设计,以及芯片功能实现的辅助电路。一、明确设计需求功能需求:根据芯片的功能特性,确定外围电路需要实现的功能,如数据传输、电源管理、时钟同步等。性能需求

DDR是当前最常用的存储器设计技术之一,其高速、低功耗的特性满足了众多消费者的需求。但随着传输速度的加快,DDR的设计验证难度呈指数上升。对仿真工程师来说,DDR的高速率很容易引起一系列信号完整性问题,引发包括时序冲突、协议背离、时钟抖动及

时钟电路模块在电子系统中起着非常重要的作用,其主要功能包括:芯片同步:时钟电路模块提供稳定的时钟信号,用于同步数字芯片(如处理器、存储器、接口芯片等)的工作,确保它们在正确的时间点进行数据传输和处理。数据同步:时钟信号可以作为数据传输中的同

扫码关注

扫码关注