- 全部

- 默认排序

我们常把晶振比喻为数字电路的心脏,这是因为,数字电路的所有工作都离不开时钟信号,晶振直接控制着整个系统,若晶振不运作那么整个系统也就瘫痪了,所以晶振是决定了数字电路开始工作的先决条件。 我们常说的晶振,是石英晶体振荡器和石英晶体谐振器两种,他们都是利用石英晶体的压电效应制作而成。在石英晶体的两个电

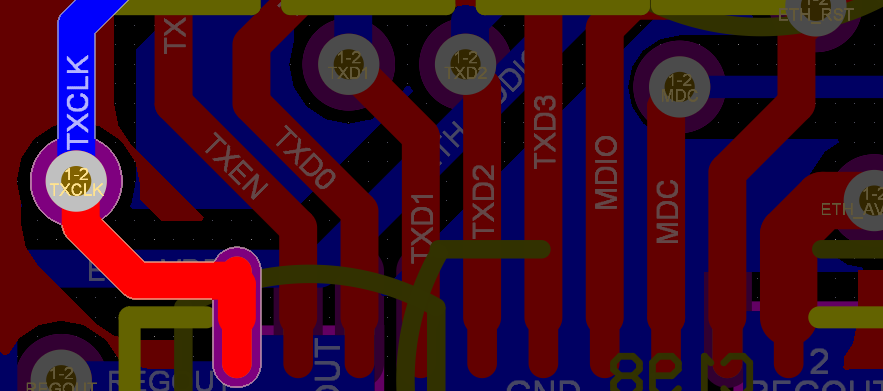

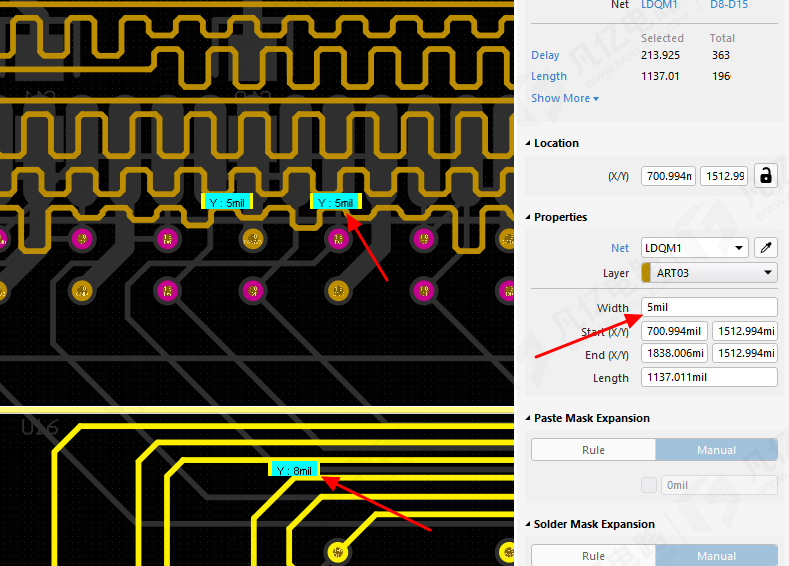

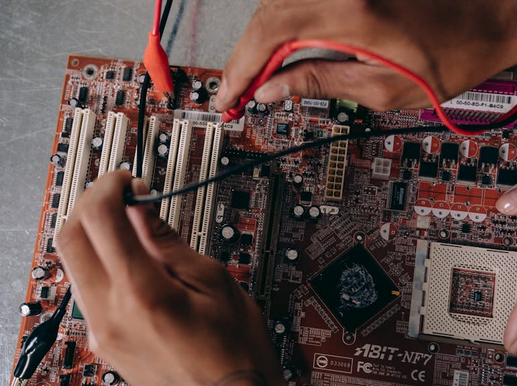

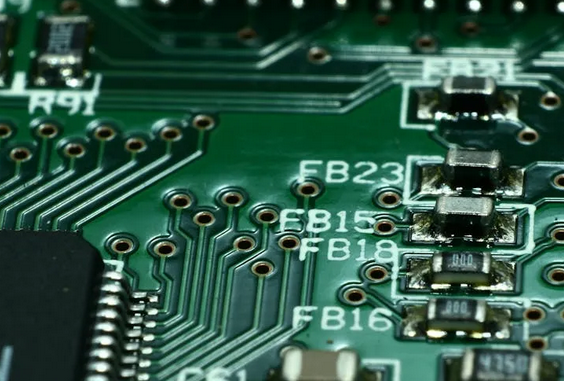

焊盘出线不规范,不能从侧面出线,出线的时候线宽不要大于焊盘宽度这个变压器下面的挖空可以在宽一点rx和tx没有做等长,信号线中间不要变化线宽时钟没有包地处理两个不同的地除跨接器件外其他的地方连接要不小于1.5mm差分对内等长误差大于5mil以

1、9FGL0641DKILF :PCI Express(PCIe) 时钟发生器 IC 100MHz9FGL0641器件是6路输出3.3V PCIe gen 1–6时钟发生器。每个输出都有一个支持PCIe CLKREQ#功能的专用OE#引脚

一、88W9064 —— 2.4/5 GHz双频4x4 Wi-Fi® 6 (802.11ax)接入解决方案88W9064-A1-BWPC/AK 是先进的Wi-Fi 6接入解决方案下一代演进的一部分,已助力打造了许多屡获殊荣的平台。该器件系列

走线保持3w间距等长绕线尽量咬合电容尽量靠近焊盘,电源走线加粗时钟线等长错误以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.com/item

晶振,作为电子设备的核心时钟源,其频率稳定性是很多电子工程师设计时需要考虑的重要原因之一,若是处理不当,晶振频率发生漂移,导致设备无法正常运行,还带来一系列问题,所以今天来讲讲晶振频率漂移,希望对小伙伴们有所帮助。1、系统稳定性下降晶振的频

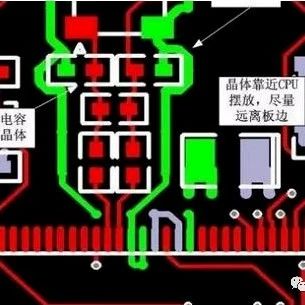

在电子产品设计中,很容易碰见大佬说不要在PCB板边缘放晶振,晶振,也就是晶体振荡器,作为提供稳定时钟信号的关键元件,那么为什么不能放在PCB板边缘?1、机械应力与振动风险PCB板边缘是设备与外界连接和固定的关键区域,如插槽、连接器等都位于此

1、LMK04368MPAPTEP 是一款适用于航天应用、支持 JEDEC JESD204B/C 的高性能时钟调节器。PLL2 可以配置 14 个时钟输出以驱动 7 个 JESD204B/C 转换器或其他逻辑器件(使用器件和 SYSREF

在电子系统中,晶振作为关键的时钟源,备受电子工程师的关注,然而在设计过程中,很容易听见这样的说法,如:晶振精度不准,容易导致电路稳定差,这种说法是否属实?下面一起来看看吧!1、晶振精度对系统稳定性的影响晶振的精度将直接影响到系统时钟信号的准

STM32单片机按功耗由高到低排列,其工作模式可分为运行、睡眠、停止和待机。上电复位后,STM32处于运行状态,但其内核若不再继续运行,可选择进入三种低功耗模式降低功耗,那么如何选?1、睡眠模式该模式此时关闭了内核时钟,而片上外设和其他CM

扫码关注

扫码关注