- 全部

- 默认排序

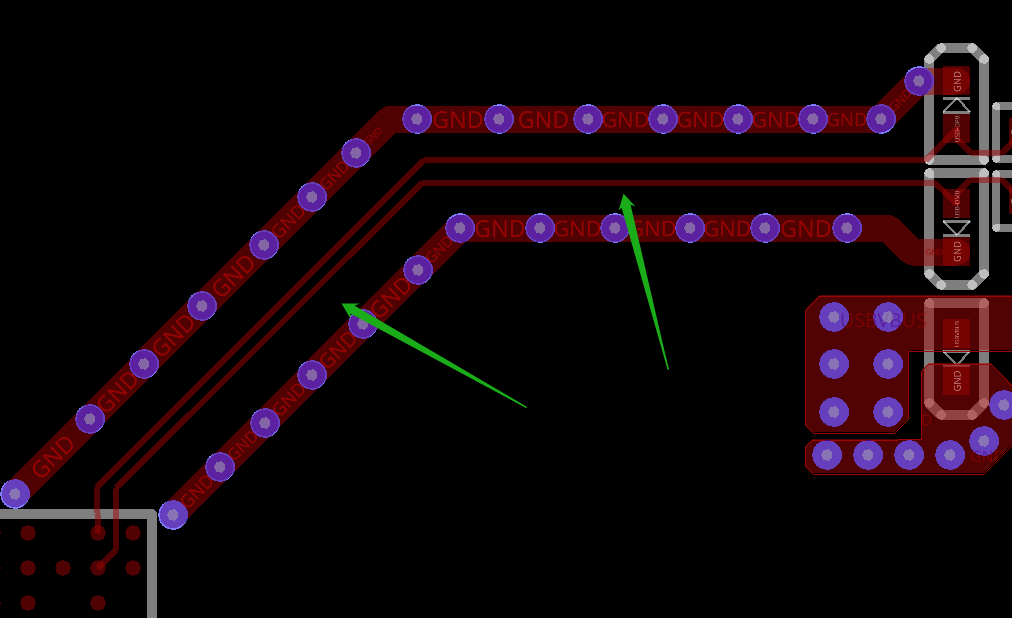

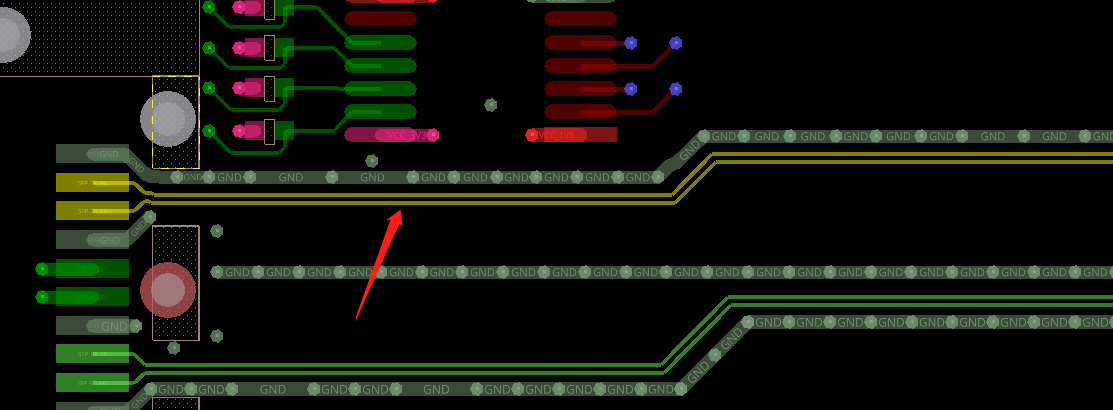

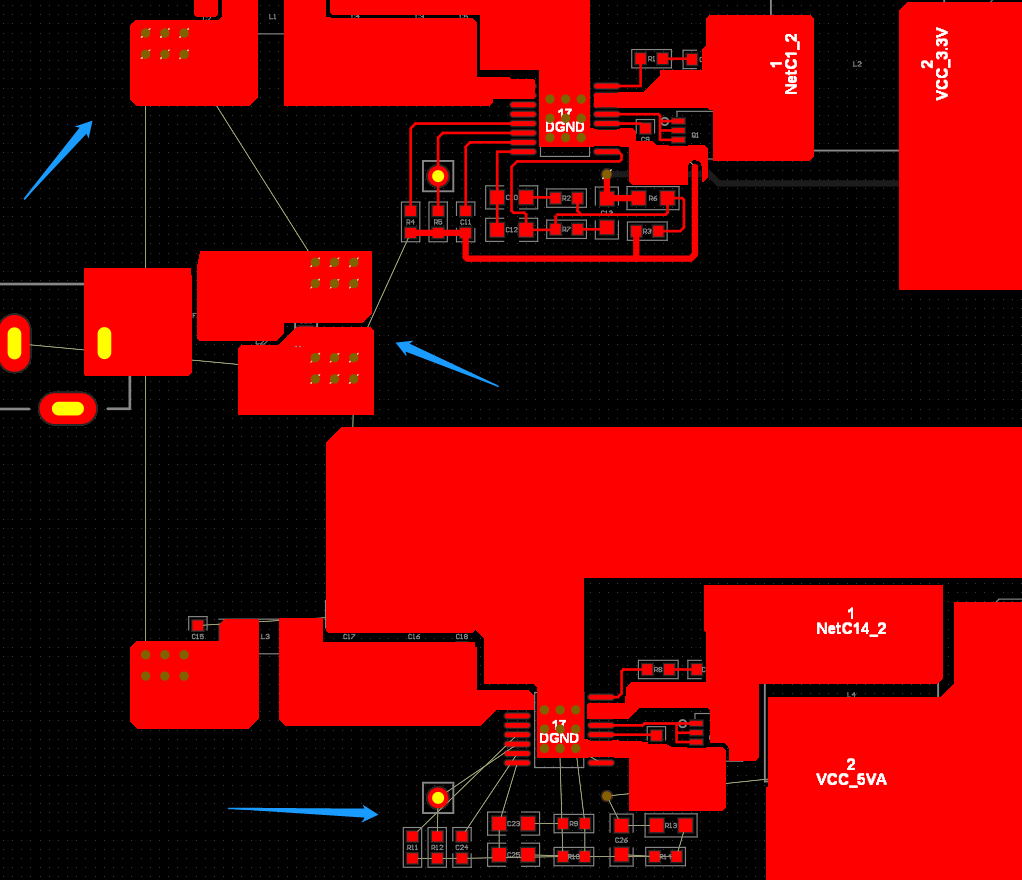

USB2.0:差分走线是需要保持耦合,需要修改,不合格:USB3.0:还有一块铜皮存在板外,自己删除下:此处器件注意整体中心对齐放置:差分信号打孔换层的过孔两侧打上地过孔:此处差分需要优化,要耦合走线 :注意此处焊盘出线,需要从两侧边拉线出

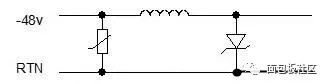

电感、电阻、导线本身并不是保护器件,但在多个不同保护器件组合构成的防护电路中,可以起到配合的作用。防护器件中,气体放电管的特点是通流量大、但响应时间慢、冲击击穿电压高;TVS管的通流量小,响应时间最快,电压钳位特性最好;压敏电阻的特性介于这两者之间,当一个防护电路要求整体通流量大,能够实现精细保护的

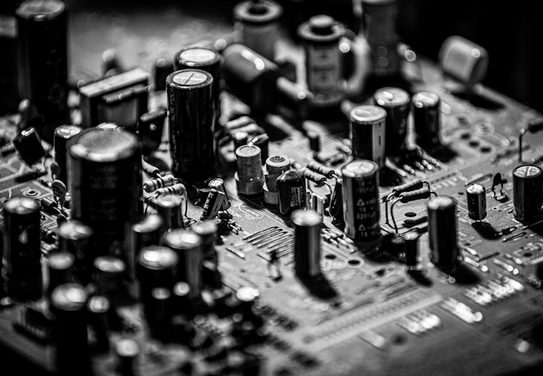

在电子产品制造中,插装元器件是必不可少的,不仅关乎产品的性能稳定,还影响着整体的生产效率及成本,为确保元器件的正确安装及产品的可靠运行,工程师必须遵循一系列原则进行操作,下面我们来看看有哪些原则需要遵循?1、安装顺序的合理性在手工操作中,应

差分信号尽量包地包完全:此处上述一致原因,可以优化:此处电源信号的铜皮尽量优化宽一点,不然整体的铜皮载流量是从最窄处计算的:差分对内需要做等长处理,误差胃5MIL:此对差分没有做等长处理:其他的没什么问题。以上评审报告来源于凡亿教育90天高

一直以来,有很多人询问数字芯片验证行情如何?发展如何,然后也有不少回答,基本上都是正向的:薪资高、机会多、发展好。有位大佬表示:做验证更锻炼整体思维,更能全面的接触到系统设计需求。做验证学习的知识通用性更广,和具体应用领域的知识关联不那么紧

电源也没连接,地也没连接,信号也没连接:建议设计完成之后再把文件提交评审。注意铜皮尽量不要直角,尽量钝角铺铜:存在类似问题的都自己优化下。电源输入部分的器件靠近IC输入管脚布局,不要太远,整个路径都是要尽量短的:器件建议整体中心对齐:走线不

在电子设计中,模数转换器(ADC)和数字模拟转换器(DAC)的布局布线是影响系统性能的关键因素,合理的布线不仅可提高信号质量,减少噪声干扰,还能优化系统的整体性能。1、预划分布先区域2、分离模拟与数字信号3、优化ADC与DAC的布线①ADC

在PCB设计中,晶体振荡器(晶振)作为时钟信号的源头,其稳定性和准确性对系统整体性能至关重要,在双面板设计中,可能会遇见这个说法“晶振下方不得走线”,这个说法是否属实?为什么不能走线?1、晶振的工作原理及特性晶振通过石英晶体的压电效应,产生

电源损耗是如何分布的?

在电源设计中,电源损耗是很重要的关键考量因素,将直接关联到电源的整体效率、稳定性和可靠性,在电源内部,损耗的分布情况复杂多样,涉及多种元件和电路环节,所以工程师是必须要深入了解电源损耗的分布情况,以此优化电源设计。1、开关关(如MOS管)损

在电子设计中,输出模式的选择对电子系统的整体性能有重要影响,而开漏输出作为其中一种常见的输出模式,在多种场景中发挥重要作用。本文将介绍开漏输出,希望对小伙伴们有所帮助。1、开漏输出是什么?开漏输出是一种基于MOSFET(金属氧化物半导体场效

扫码关注

扫码关注