- 全部

- 默认排序

答:在制作封装时,建议使用的封装字体可如下示。如果字体的太小了,生产会有困难并且可能丝印印出来不方便识别,字体过大需要很大的PCB板空间放置,不利于设计,如表4-2所示:线宽字长字高42520单板器件/局部布局较密,一般不推荐用53025常规设计,推荐使用64535单板密度较小,有摆放足够空间表4-2 封装字体大小示意图

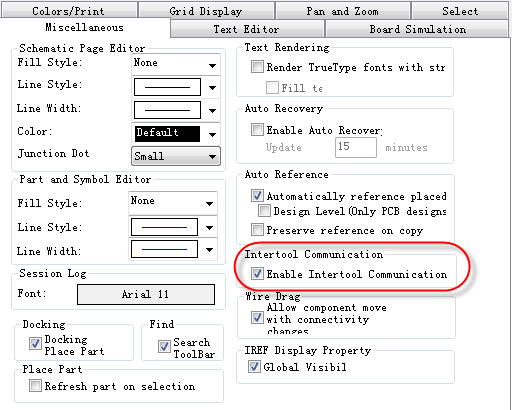

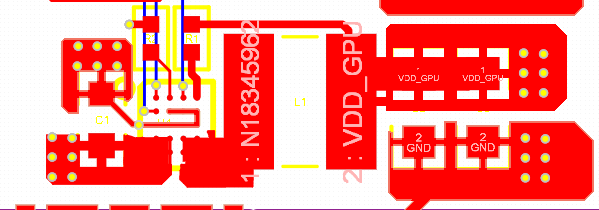

答:我们使用Allegro软件进行布局,是需要按照原理图进行布局的,按照模块进行布局,不能随意的去摆放元器件,所以我们需要进行交互式操作,这样才能提高设计的效率。Orcad软件与Allegro软件交互操作的具体步骤如下:

答:PCB版图,根据原理图画成的实际元件摆放和连线图,供制作实际电路板用,可在程控机上直接做出板来。

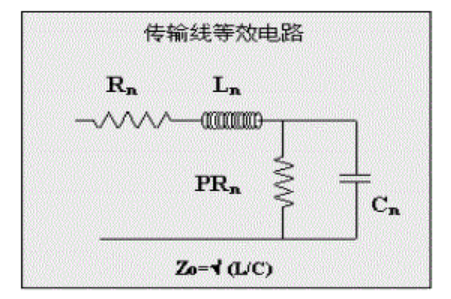

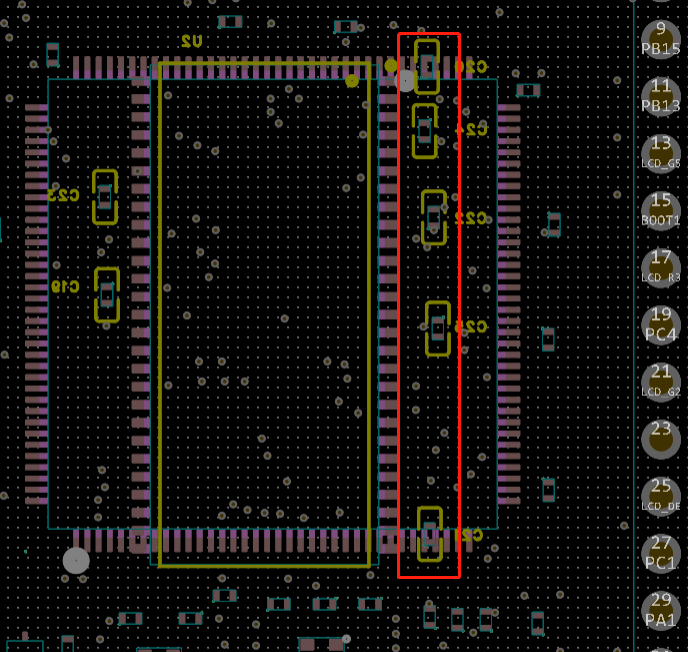

高速PCB板设计的学习难点在于布局布线环节,很多小白在学习过程中都会困惑:传输线是什么,如何摆放传输线?传输线为什么存在严重的电磁干扰等诸多问题,归根结底在于小白对传输线了解程度不高,所以今天谈谈高速PCB电路上的传输线。如图所示,该图是串

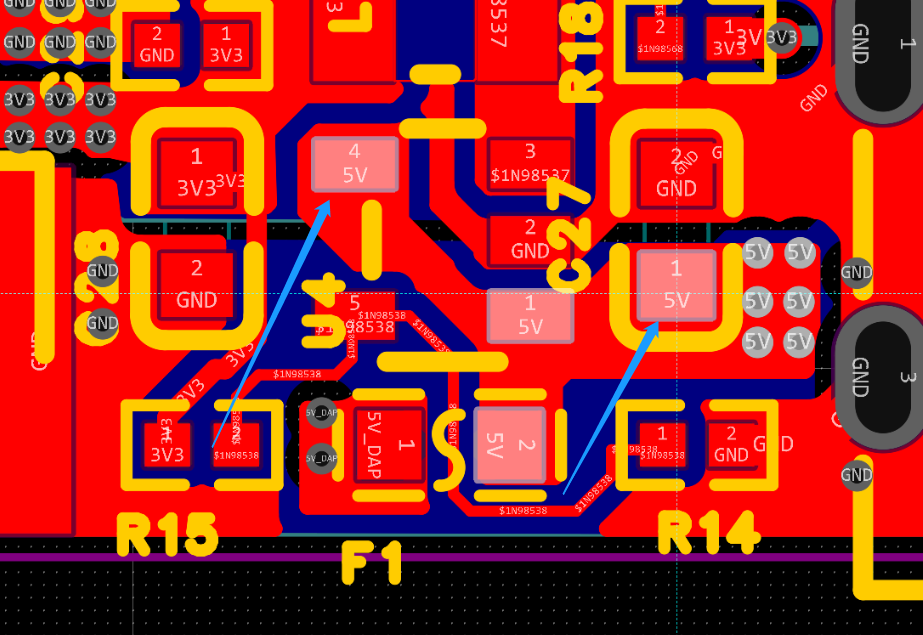

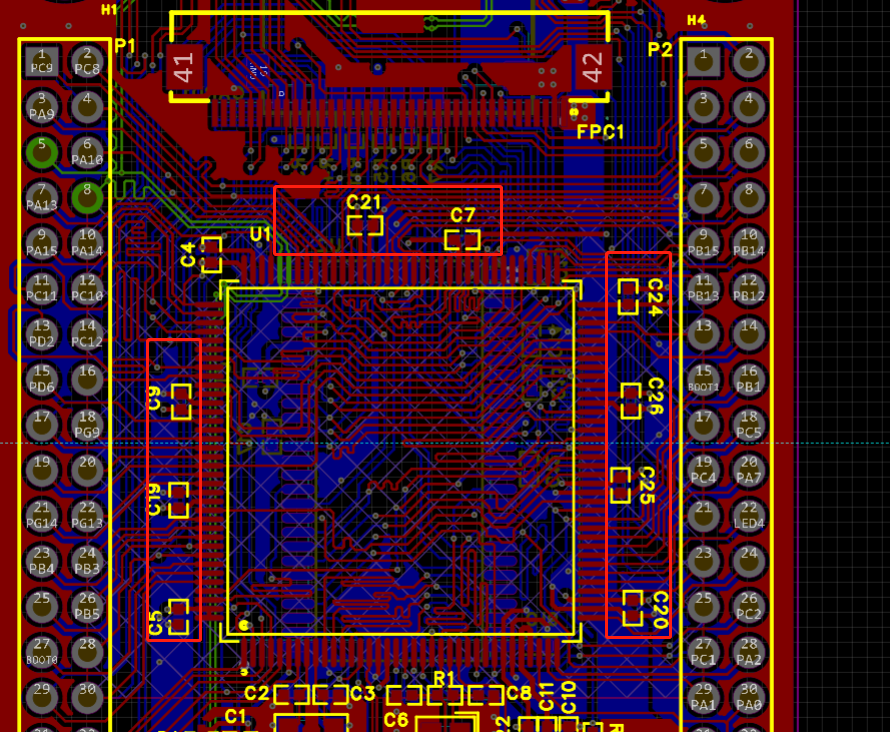

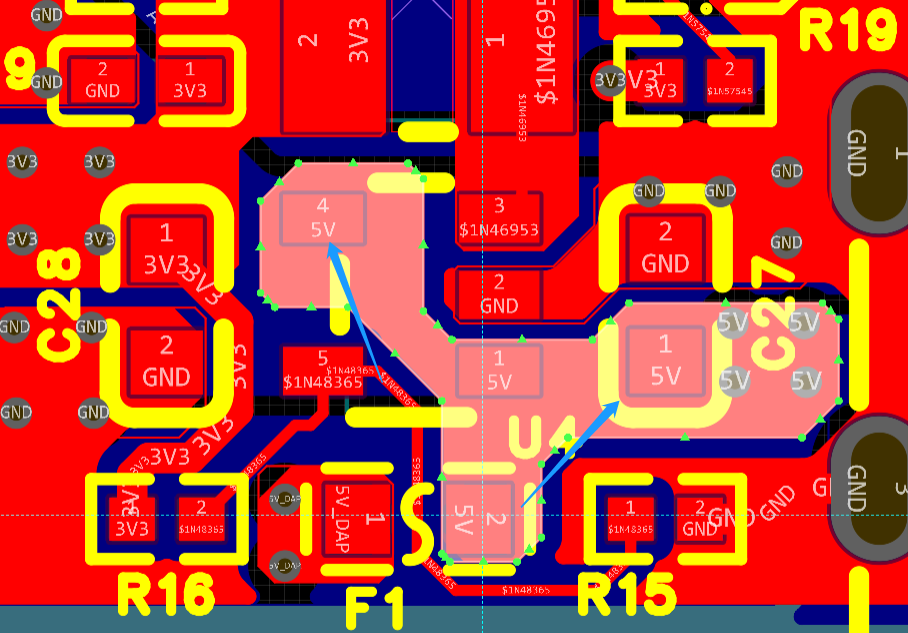

电源输入的滤波电容应该靠近输入管脚(4脚)放置2.此处走线需要优化一下,尽量不要有直角,走线不要从器件中间穿3.差分线处理不当,锯齿状等长,凸起高度不得超过线距的两倍4.器件摆放注意局部对齐处理5.logo图片最好不要放在焊盘上【问题改善建

器件摆放注意局部对齐处理2.注意器件干涉3.电源输出的滤波电容要靠近输出管脚放置4.电源输入输出换层打孔处理不当,输入应该打在滤波电容的前面,输出打在滤波电容的后面5..差分线处理不当,锯齿状等长,凸起高度不得超过线距的两倍6.确认一下此处

器件摆放注意局部对齐处理2.电源输入的滤波电容应该靠近输入管脚(4脚)放置3.焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊4.确认一下此处是否满足载流【问题改善建议】:加粗线宽或者铺铜处理5.差分线处理不当,锯齿状等长,

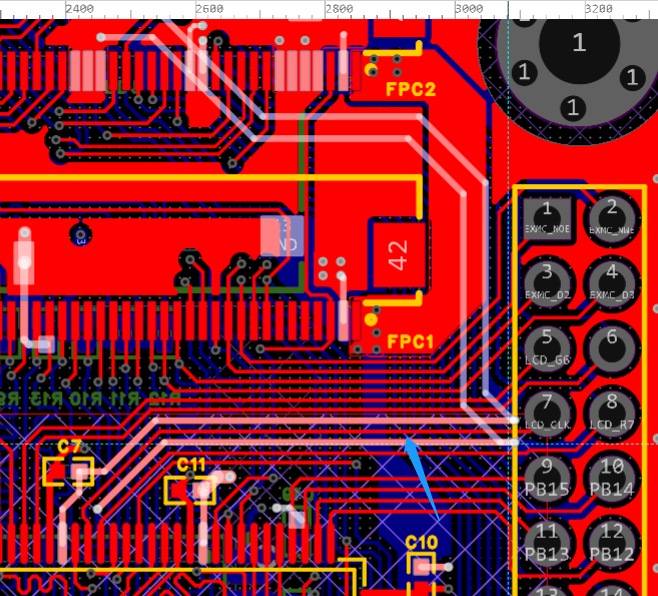

器件摆放注意对齐处理处理2.差分线处理不当,锯齿状等长,凸起高度不得超过线距的两倍3.此处走线需要优化一下,尽量从焊盘长边出线4.焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊5.晶振下面尽量不要走线6.线宽突变,确认一下

1.电源输入的滤波电容应该靠近输入管脚(4脚)放置2.走线尽量不要从器件中间穿,自己调整一下走线路劲3.此处出线载流瓶颈,载流计算都是以铜皮在窄处进行计算4.差分线处理不当,锯齿状等长,凸起高度不得超过线距的两倍5.器件摆放尽量对齐处理6.

时钟信号包地需要在地线上间隔150mil-200mil打上一个地过孔2.差分线处理不当,锯齿状等长,凸起高度不得超过线距的两倍3.器件摆放注意对齐处理4.焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊;地网络打一个孔即可,

扫码关注

扫码关注