- 全部

- 默认排序

电路进行验证,就只能通过ADS这类的工具来进行仿真验证和评估,如果知道芯片的类型并且有模型,可以针对性的进行特定的仿真,如果不知道芯片的型号或者没有模型,就使用ADS中的TX_Diff和Rx_Diff元件,在元件可以设定信号的速率、PRBS的码型、抖动、均衡等参数,然后进行仿真评估;对于一些小公司而言,这就只能凭经验了。 在获得了连接器、线缆或者PCB背板的测试或者仿真S参数之后,可以在ADS中非常方便的判断是否满足总线或者设计的要求: 本文就和大家分享下在ADS中如何对这类的情况进行仿真分

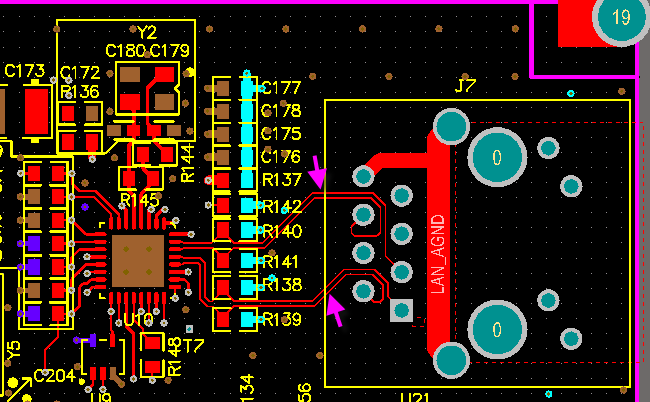

差分走线,信号换层过孔数量,等长长度把控,阻抗控制要求,跨分割的损耗,走线拐角的位置形状,绕线方式对应的插损和回损,布局不妥当造成的一系列串扰和叠层串扰,布局不恰当操作焊盘存在的stub。

仅看近30年的发展,以PC为代表的行业几度繁荣而后归于平静,从最早的百兆级处理器速度倍频直到今天的几个GHz级别,总线位宽从16位扩展到今天的64位,以Intel为首的行业龙头公司将CPU的处理能力整整提升了成百上千倍。 在总线宽度和处理器速度达到瓶颈后的近10年里,整个行业将突破的战场放在了高速接口上,外部串行高速接口的速率从Gbps迅速飞升到几十个Gbps,为了实现更高的吞吐量,还采用了复杂的高阶调制和增加链路宽度的办法。这一切简直是以“迅雷不及掩耳盗铃之势”汹涌而至,作为“攻城狮”的你做

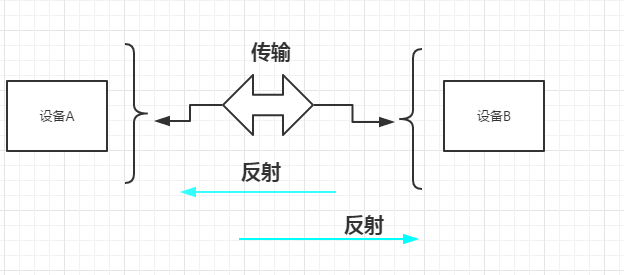

我们在用allegro进行PCB设计完成以后,都需要对一组传输的总线进行时序等长,在做时序等长的时候,分为绝对传输延迟与相对传输延迟。绝对传输延迟,顾名思义,信号传输在PCB设计中都是有一个走线的长度,我们通过设置这个信号线传输的最大值与最小值,来实现等长的方法,就称之为绝对传输延迟。

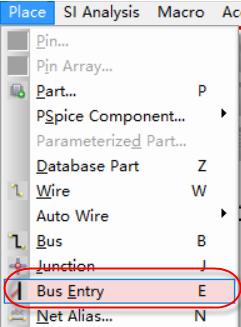

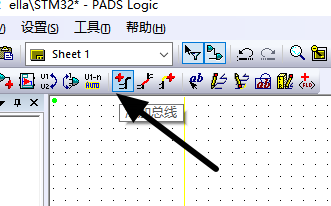

我们创建好总线,给总线命名好以后就需要将创建好的总线与个分支信号连接起来,操作的步骤如下所示:第一步,放置总线入口Bus Entry,点击菜单Place→Bus Entry或者按快捷键E来进行放置,如图3-28所示;第二步,Bus Entry会悬挂在鼠标上,按快捷R可以进行旋转,选择好正确的方向,然后放置到总线上,与总线进行连接,如图3-28所示;第三步,在放置Bus Entry的时候,放置好一个以后,按快捷键F4可以进行快速放置,也可按住Ctrl键,鼠标拖动来进行快速放置,如图3-28所示;&

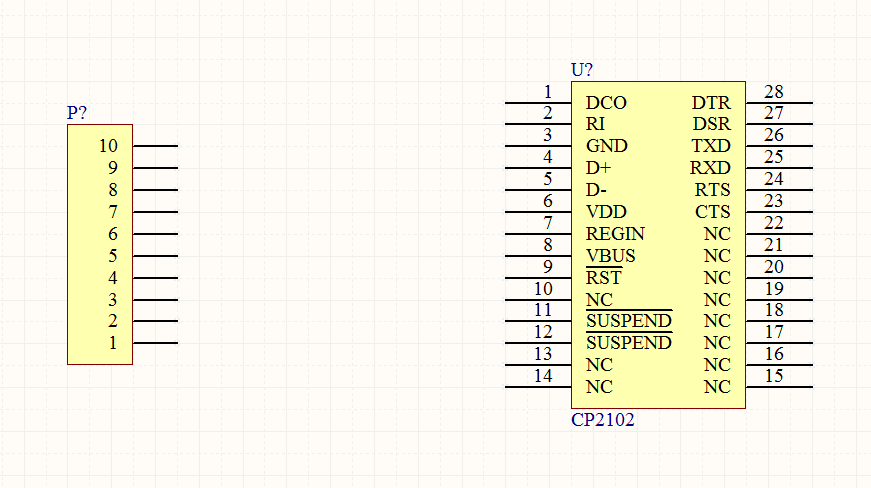

通用串行总线(英语:Universal Serial Bus,缩写:USB)是连接计算机系统与外部设备的一种串口总线标准,也是一种输入输出接口的技术规范,被广泛地应用于个人电脑和移动设备等信息通讯产品,并扩展至摄影器材、数字电视(机顶盒)、游戏机等其它相关领域。最新一代是USB 3.1,传输速度为10Gbit/s,三段式电压5V/12V/20V,最大供电100W ,新型Type C插型不再分正反,如图4-8所示,展示了几种常用的USB接口实物,这类型USB接口广泛应用于MID的产品中

以太网(Ethernet)是一种计算机局域网组网技术,该技术基于IEEE制定的IEEE 802.3标准,它规定了包括物理层的连线、电信号和介质访问层协议的内容。 以太网是当前应用最普遍的局域网技术。Ethernet的接口是实质是MAC通过MII总线控制PHY的过程。

在PCB设计中,绘制原理图时避免不了要用到总线,但是在我们使用Altium Designer绘制总线时总是出现一些问题,导致总线无法使用。

扫码关注

扫码关注