- 全部

- 默认排序

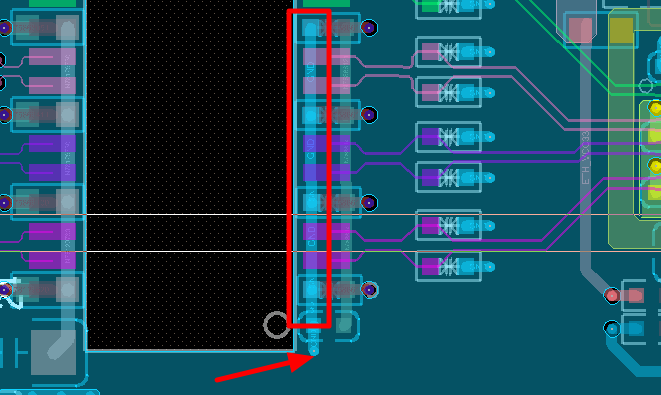

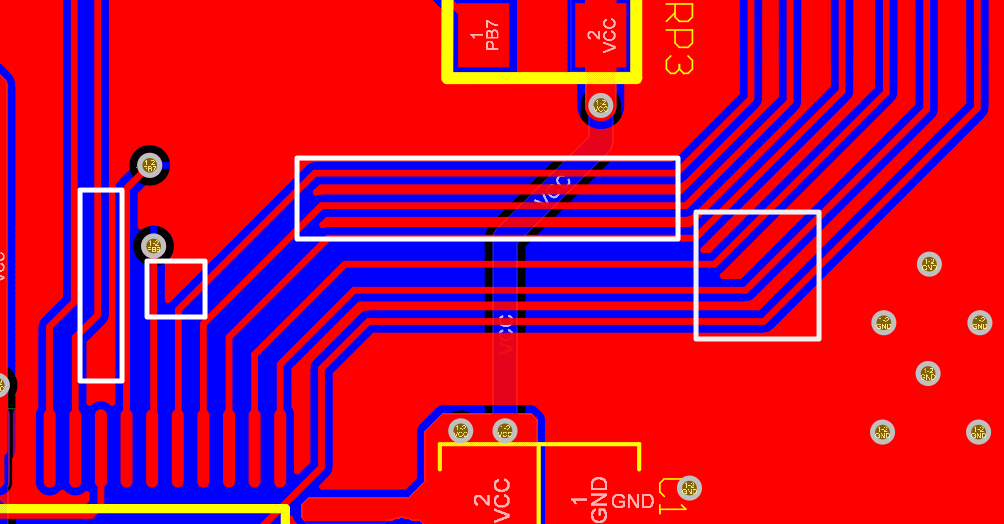

差分对内等长绕线不符合规范差分对布线线宽不一致,会导致阻抗不一致多个器件没有布局布线内层电源和地没有铜皮,导致电源和地都是开路变压器前后电源线宽不一致,变压器除差分外所有走线加粗到20mil时钟信号没有布线,应包地打孔连接rx,tx应建立等

地网络焊盘就近打孔接地晶振应走类差分形式包地打孔处理重要信号线尽量少换层,最多打三次孔以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.com

多处尖岬铜皮未处理电源模块输出应在最后一个器件后打孔、232串口模块C、V走线应加粗到10mil以上焊盘要从中心链接,不要从长边出线、锐角出线电容靠近管脚放置存在drc未处理,多处过孔只连接一个层造成天线报错 以上评审报告来源于凡亿教育90

以太网硬件电路设计

点击上方名片关注了解更多实现以太网通信硬件电路方法很多,一般情况是CPU MAC PHY 网络变压器 RJ45。整个硬件电路最多用5个电子器件完成。随着集成电路的发展,很多功能被集成在一起,简化硬件电路的设计。上述那种方法,器件较多,开发难度比较大。下面列举其它3种方法。1、CPU(集成MAC层),

C语言可以说是一种"古老"的编程语言,也是目前嵌入式中主流的编程语言,没有C语言就没有今天的各种嵌入式系统以及操作系统等等。C语言虽然说是编程开发的基础,那到底你掌握到了什么程度呢?下面我们一起看看C语言熟练到精通的几个层级:新手村在大学学过《C语言程序设计》相关的书籍,掌握的不错的获得计算机二级等

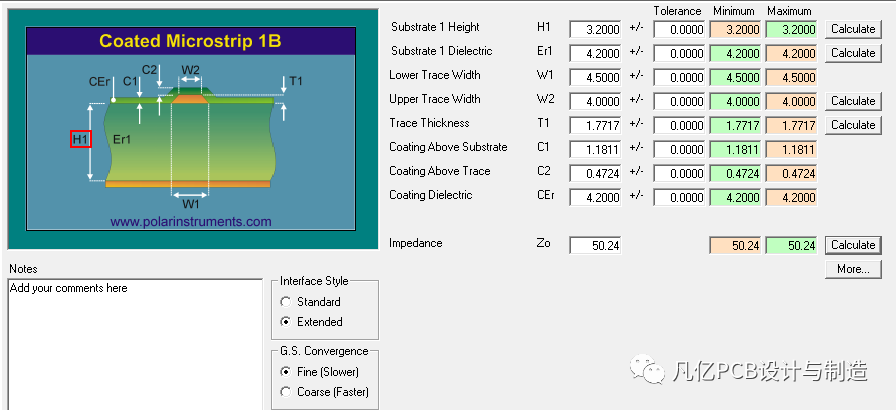

PCB是现代电子设备的核心组成部分,其设计和制造对设备性能和可靠性至关重要。在 PCB 设计中,阻抗控制和叠层设计是关键因素之一。本文将深入研究 PCB 的阻抗知识,并探讨八层板与“假八层板”之间的区别,分析它们各自的优劣势。1. PCB阻

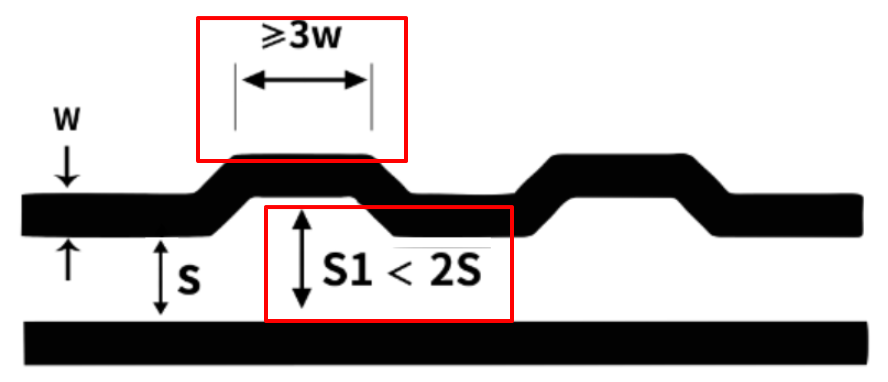

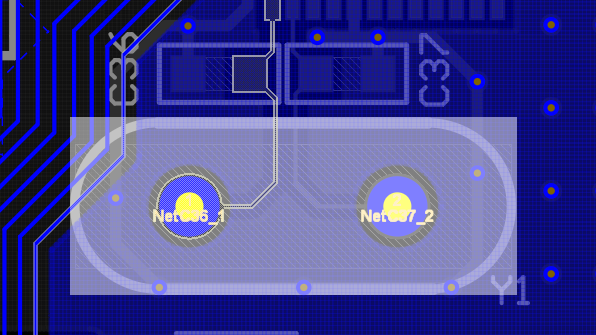

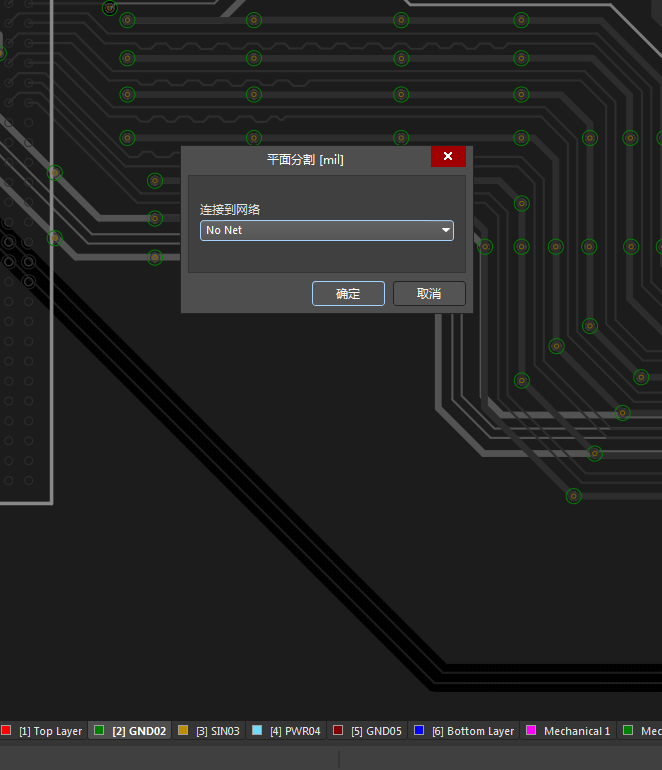

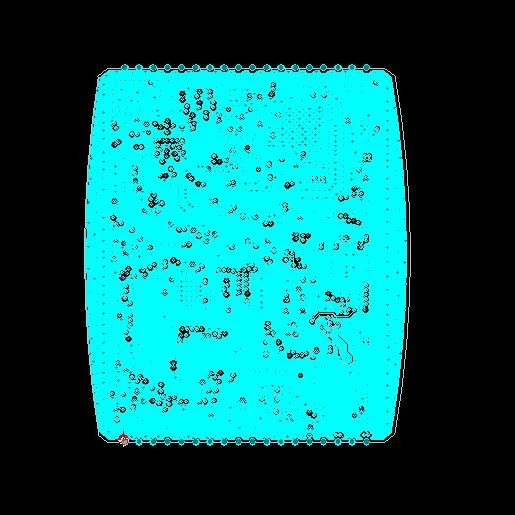

DD3 四片:注意不要出现这种锐角走线:负片层并未赋予网络:注意设计完了之后检查下走线的连接性:并未保证3W间距原则:差分对内等长注意规范:差分对内等长误差为5MIL:以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特

晶振底部不要走线:电源反馈信号8-12mil即可:直接可以顶层连接,无需在扇孔:上述一致原因:可以直接连接地线打孔包地:电路地与机壳地至少满足2MM间距:等长线满足3W原则:还存在等长报错:还存在两处开路报错:以上评审报告来源于凡亿教育90

地负片层并未赋予网络:差分对内等长注意规范:上述一致原因:差分对内等长5MIL:以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.com/it

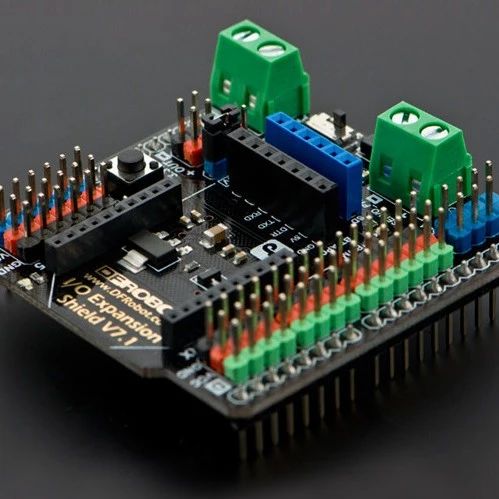

8层PCB设计成的核心板

01、前言在做硬件开发时,很多时候要把核心的东西设计成核心板,做成模块。因为核心的电路需要运行稳定,可靠,往往要花很多时间去设计,调试,测试,优化,最终才能达到稳定,可靠。如果每次设计项目时,都要重新去设计核心的电路的PCB,做电路板去调试,测试,优化,那么每个项目的研发周期就会很长,这样搞研发就没

扫码关注

扫码关注