- 全部

- 默认排序

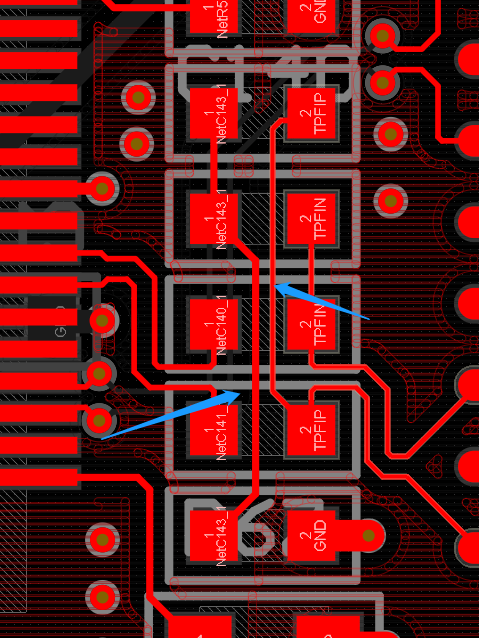

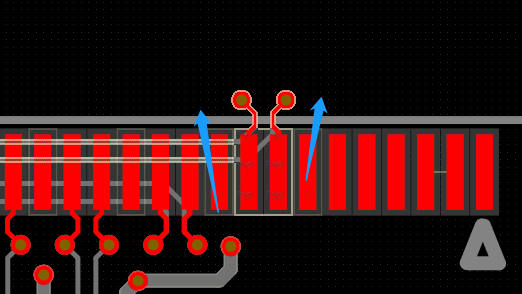

走线不要从电阻电容中间穿,后期容易造成短路,可以打孔走底层2.跨接器件旁边尽量多打地过孔3.数据线和地址线等长都需要满足3W4.电感下面尽量不要走线以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接

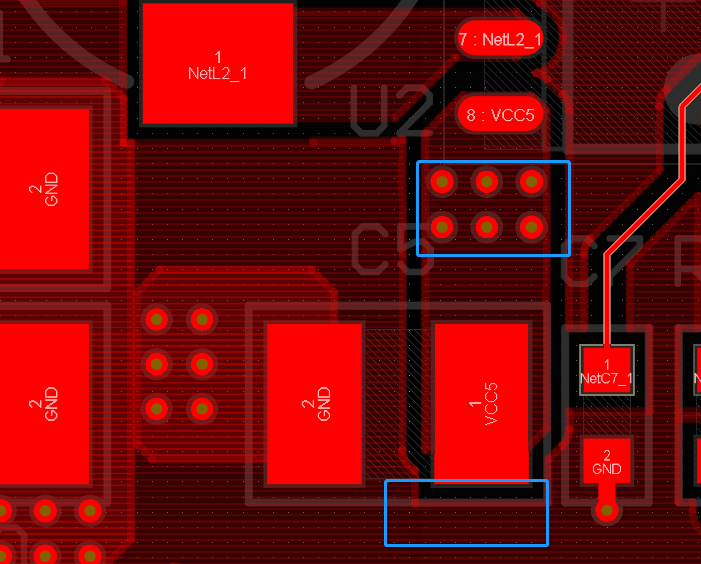

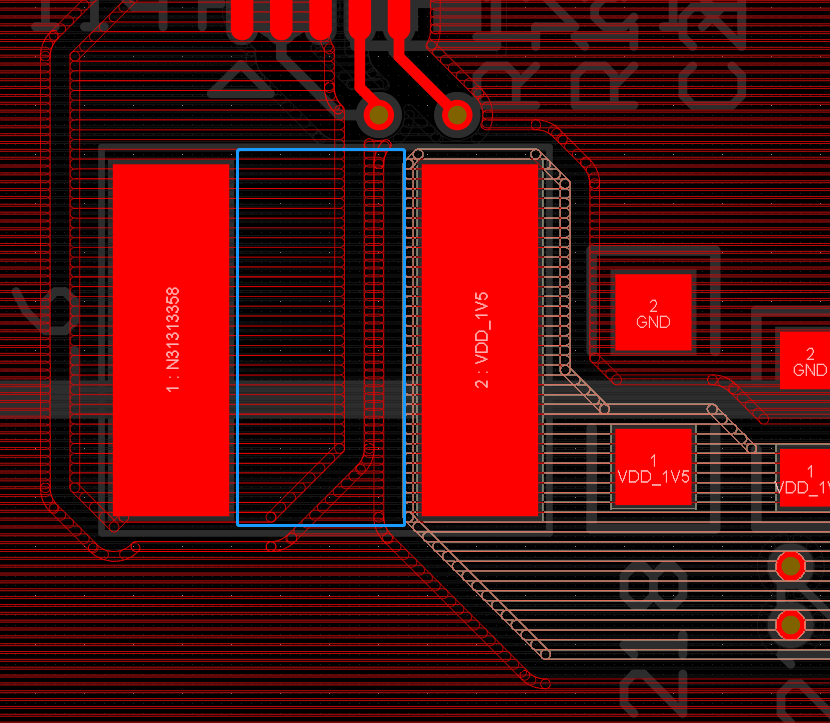

输入打孔要打在 电容的前面,先经过电容在进入管脚2.顶层BGA里面的铜皮可以挖掉,避免有碎铜,孤铜3.存在多余的线头其他就没什么问题了以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教

什么是射频封装技术?

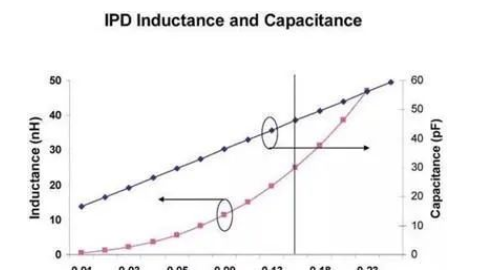

封装这个词对于工程师来说应该不陌生,但是射频封装技术相对于普通封装技术来说显得更为复杂。射频和无线产品领域可以使用非常广泛的封装载体技术,它们包括引线框架、层压基板、低温共烧陶瓷(LTCC)和硅底板载体(Si Backplane)。由于不断

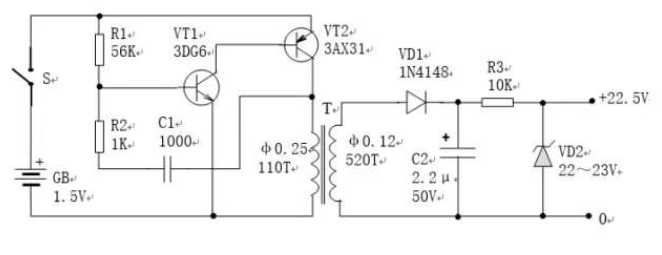

万用表是从事电工、电子技术工作者的必备工具,它的高阻挡通常使用一块9V、15A或22.5V的叠层电池。这种电池不但价格较高,而且寿命短,经常更换很不经济。这里介绍几款适合万用表使用的小型直流升压器电路,这些电路结构简单、元件少,改装后可将电

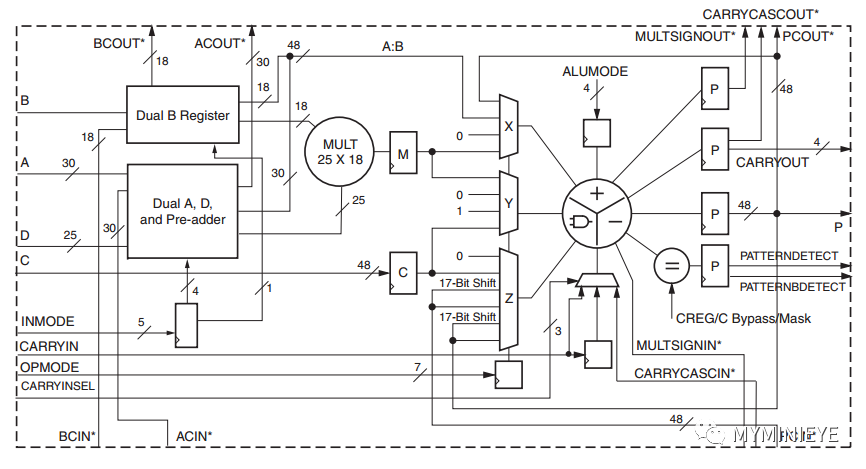

FPGA中DSP资源是宝贵的且有限,我们在计算大位宽的指数、复数乘法、累加、累乘等运算时都会用到DSP资源,如果我们不了解底层的DSP特性,很多设计可能都无法进行。逻辑综合往往是不可控的,为了能够充分利用DSP资源,我们需要对DSP48E1有所了解。1.DSP48E1介绍 DSP48E1

差分线换层需要再旁边添加一堆回流地过孔2.差分线处理不当,锯齿状等长不能超过线距的两倍3.差分对间等长误差10mil4.差分出现要尽量耦合5.地线上需要打过孔,这样容易产生天线以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解

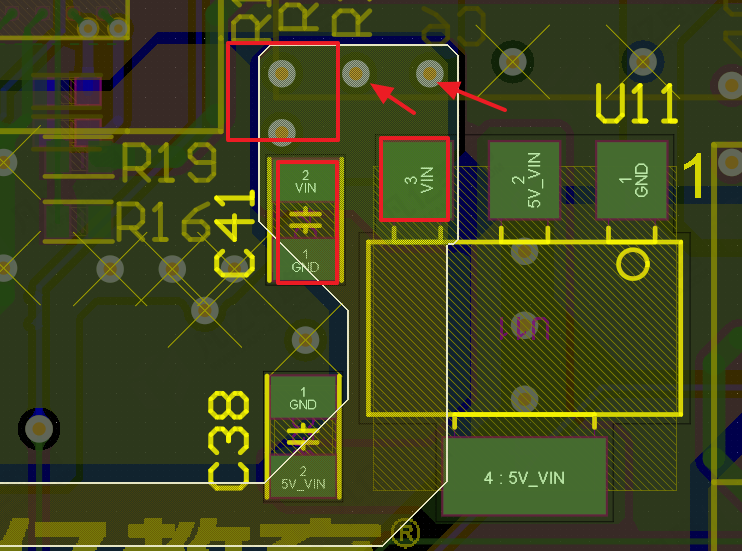

1.电源输入应打在电容前方先经过电容在到管脚。2.电源输出要先经过电容在打孔。3..电源输入滤波电容按照先大后小的顺序摆放,在连接到管脚;多处电容没有按照顺序摆放4.地焊盘就近打孔。5.同层连接不要打孔6.电源线加粗,电源输入电容不要合孔7

此处走线8mil不满足载流,建议铺铜处理2.电感所在层的内部需要挖空处理3.反馈需要从最后一个滤波电容后面取样4.反馈路劲上的器件需要靠近管脚放置5.存在开路以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可

电感所在层的内部需要挖空处理2.反馈线走一根10mil的线即可,不用进行铺铜3.存在开路4.地址线等长存在报错5.注意电源线宽尽量保持一下,满足载流,走线最少需要加粗到15mil以上6.地网络需要就近打孔以上评审报告来源于凡亿教育90天高速

注意低脂线等长需要满足3W2.数据线之间等长也需要满足3W3.电感所在层的内部需要挖空4.VREF的电源走线需要加粗到15mil以上5.电容摆放尽量保证一个管脚一个,靠近管脚放置6.除了散热过孔,其他的都可以盖油处理以上评审报告来源于凡亿教

扫码关注

扫码关注