- 全部

- 默认排序

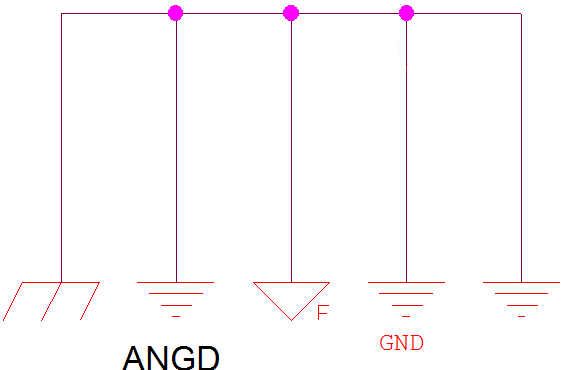

答:我们使用Orcad软件进行原理图的绘制的时候,总会遇到这样的问题:我们有多个地,网络名称是不同的,但是我们后面是统一连接在一起的,这时候最终导入到PCB之后,只会显示一个网络名称,我们想知道最终显示网络名称的优先级是什么呢?我们这里呢,一一给大家揭开这个谜底:第一步,我们绘制这样一张原理图,放置很多地,使用不同的网络名在同一张原理图中,如图3-238所示,它们所连接的网络分别为AGND、GND、GND_EARTH、GND_POWER等; 图3-238 各类不同的地放置示意图第二步,

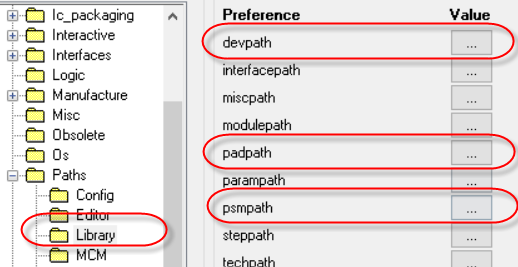

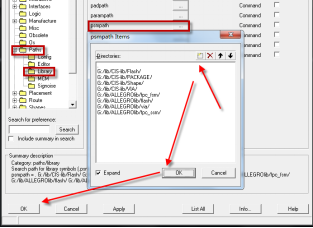

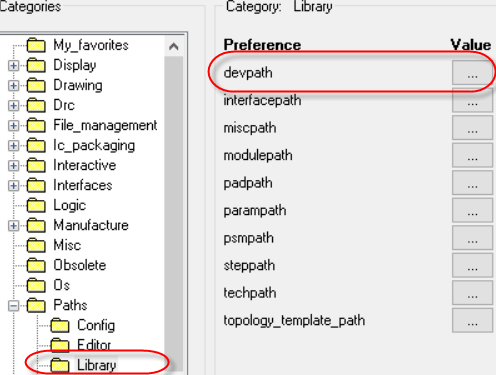

答:一般我们会在Allegro软件中指定这几个与封装库有关的路径。第一步,点击Allegro软件的Setup命令的最后一项User Preferences...,如图4-25所示; 图4-25 用户参数设置示意图第二步,在弹出的对话框中,选择Library中的devpath、padpath、psmpath三项设置路径,如图4-26所示; 图4-26 封装库路径指定示意图Ø Devpath:第三方网表(Other方式导出的网表)导入PCB时须设

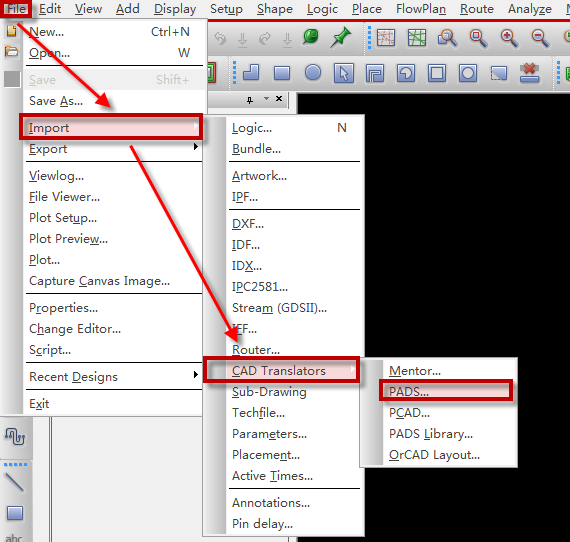

答:Pads封装导入到Allegro,一般先是通过Pads PCB转Allegro PCB,转换完成后,将封装导出,再逐个对PCB封装进行检查修改,修改为标准可用的封装。第一步,将Pads PCB导出ASC文件,打开PCB点击文件-导出选项,在弹出的对话框中设置好导出文件的文件夹和文件名,然后点击保存,如图4-78所示; 图4-78 导出asc文件示意图第二步,在弹出的对话框中勾选所有内容,格式中选择PADS Layout V2007选项,然后点击确定,就能生成ASC文件,

答:在将网表导入到PCB的过程中,经常会出现封装内管脚名或者数目与原理图内的器件管脚不一致,从而导致导入过程中报错,如图4-90所示: 图4-90 导入网表提示解析示意图上图是一个比较典型的封装中管脚与原理图中不一致而出现的报错内容。从上示报错内容(红色框标识的内容)可以获取以下信息点:Ø 器件的封装名为ERF8-40。Ø 封装中有几个多余的管脚,管脚名为41、42、43、44、45、46、47、48。Ø 封装中缺少了几个管脚,管脚名为H1、H

答:在将网表导入到PCB的过程中,常会由于带通孔的PCB封装内的焊盘中Flash在相应的路径中找不到,而导致导网表报错,报错内容及提示如图4-93所示: 图4-93 错误提示示意图根据图4-93所示,我们可以分析得出以下几个结论:Ø 导网表时报错的器封装名是CON2X5_2P54M。Ø PCB封装中焊盘名为PAD100SQR165THR的焊盘不能被完整提取到,原因是在设置的库路径下找不到名为THR100X165C150X180X040的Flash。对于此

答:导网表时,常会用到第三方网表(用Other方式导出的网表)导入到PCB中,导入时常会发生找不到device的报错,具体报错内容可查看以下内容,如图4-97所示: 图4-97 错误提示示意图根据4-97所示,我们可以分析得出以下几个结论:Ø 导网表时,器件C1的封装报错。Ø 导网表时找不到封装名为SMD_0603的device文件。可以按照以下几个步骤来解决此问题:第一步,查看device路径是否设置正确。在命令Setup-UserPreference

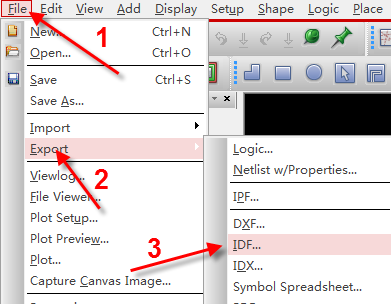

答:在进行PCB设计时,完成布局操作之后,为了更好的核对结构,除了导出2D的DXF文件之外,还需要导出3D文件,导入到PROE软件中进行对比,这样更能非常显著的看出结构是否有问题,具体导出的方法如下所示:

答:在进行PCB设计时,完成布局操作之后,为了更好的核对结构,除了导出2D的DXF文件之外,还需要导出3D文件,导入到PROE软件中进行对比,这样更能非常显著的看出结构是否有问题,具体导出的方法如下所示:

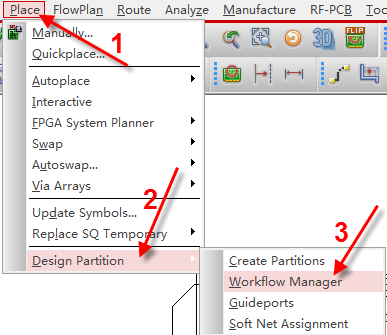

答:我们遇到比较复杂的PCB设计时候,需要我们进行协同设计,分为主设计这以及从设计者,采用的是Allegro软件自带的 Team Design功能,Team Design功能是一种用于团队设计的功能模块,它可将一块复杂的PCB板分成多个部分,通过分区合作设计,在需要的时候可以全自动导入,可以大大提高设计的效率,缩短设计周期。我们下面详细介绍一下Team Design功能的使用,具体如下:

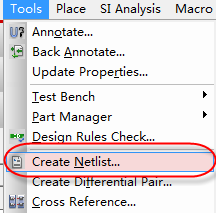

答:现在市面上用的最多的是,Orcad软件绘制原理图,Allegro软件绘制PCB版图。我们现在讲解一下怎么使用Orcad软件将绘制好的原理图,输出第一方的网表,然后将第一方的网表导入到Allegro软件中,具体操作如下:

扫码关注

扫码关注