- 全部

- 默认排序

在规则里面这么多拓扑结构,很多时候我们只需要使用第一个shortest规则就可以,在ad中这几个出线规则其实并不需要我们去太多的纠结,因为对于器件而言不同的器件我们使用的布局方式又是不一样的,比如DDR什么时候用T点,什么时候用菊花链 ,什么时候用fly-By,等等这些,都是需要按照我们的行业规范进行布局和布线。

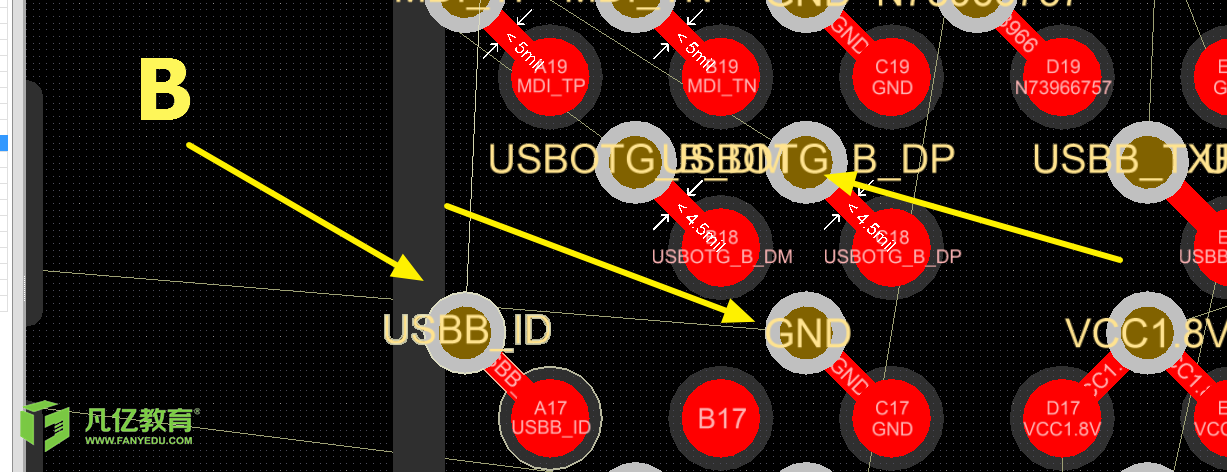

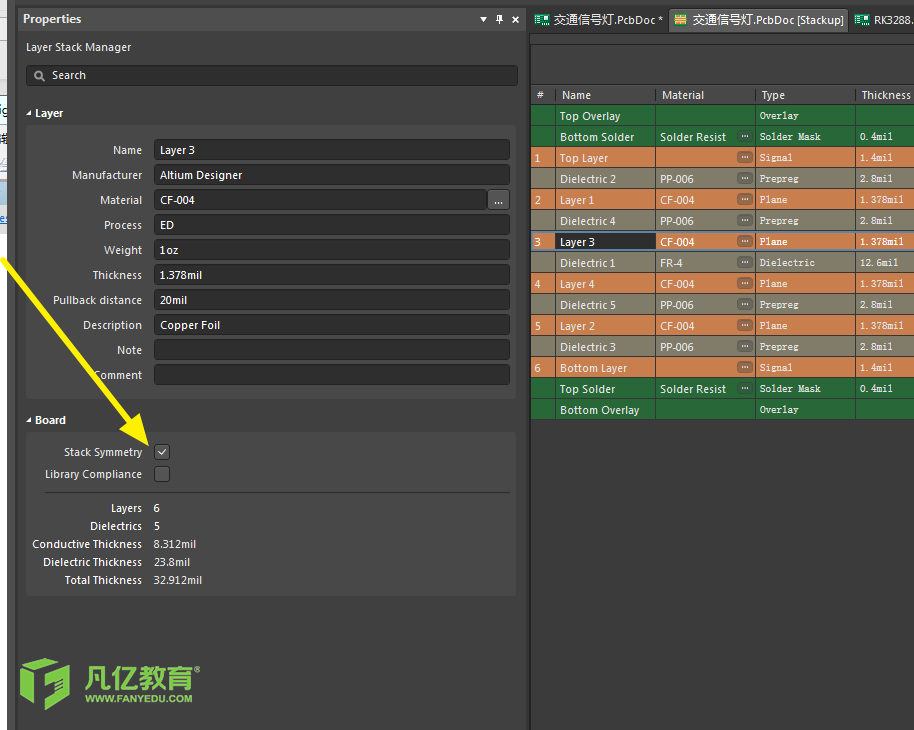

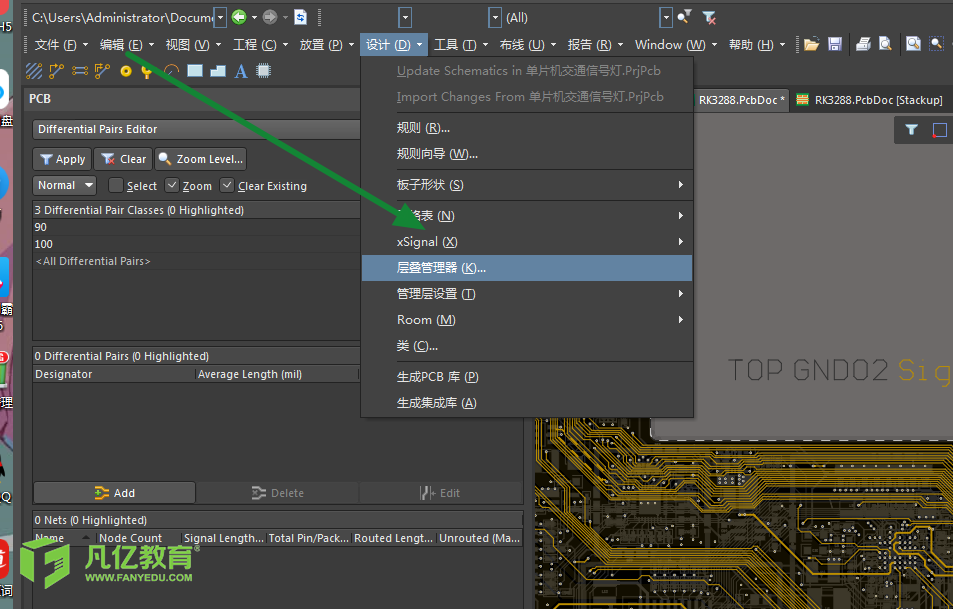

对于AD爱好者来说,每一次的版本更新都是新功能的添加和旧功能的优化或者是移除,在新版AD19在内电层内缩pullback进行了位置变化,同时内电层改变内缩还相邻的内缩会一起变动。

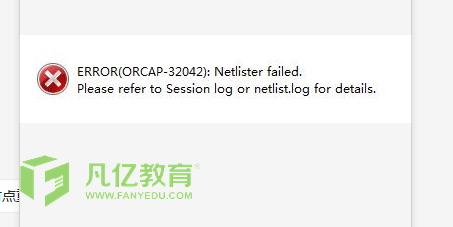

我们在进行原理图设计的时候,完成之后就需要去进行网表的导出,然后在pcb中去进行设计。有很多学员在原理图导出网表的这一操作中会出现各种各样的报错,那么今天我们就来看看最常见的一项导出网表的报错的解决办法,即”Netlister failed”的报错。

我们有时在进行PCB设计的时候,肯定会选择直接拖动 一个元器件或者一个模块去进行自己想要的布局。那么,就会遇到我们在拖动的时候,这个元器件或者这个模块是高亮,但是其它元器件与区域全部都是完全黑暗的,我们根本都看不清楚,此刻拖动的元器件或者模块被放置在哪里了,是不是重叠了其它的元器件放置。所以,遇到这个问题,我们应该如何解决呢?

对于AD爱好者来说,每一次的版本更新都是新功能的添加和旧功能的优化或者是移除,在新版AD19在内电层内缩pullback进行了位置变化,同时内电层改变内缩还相邻的内缩会一起变动。

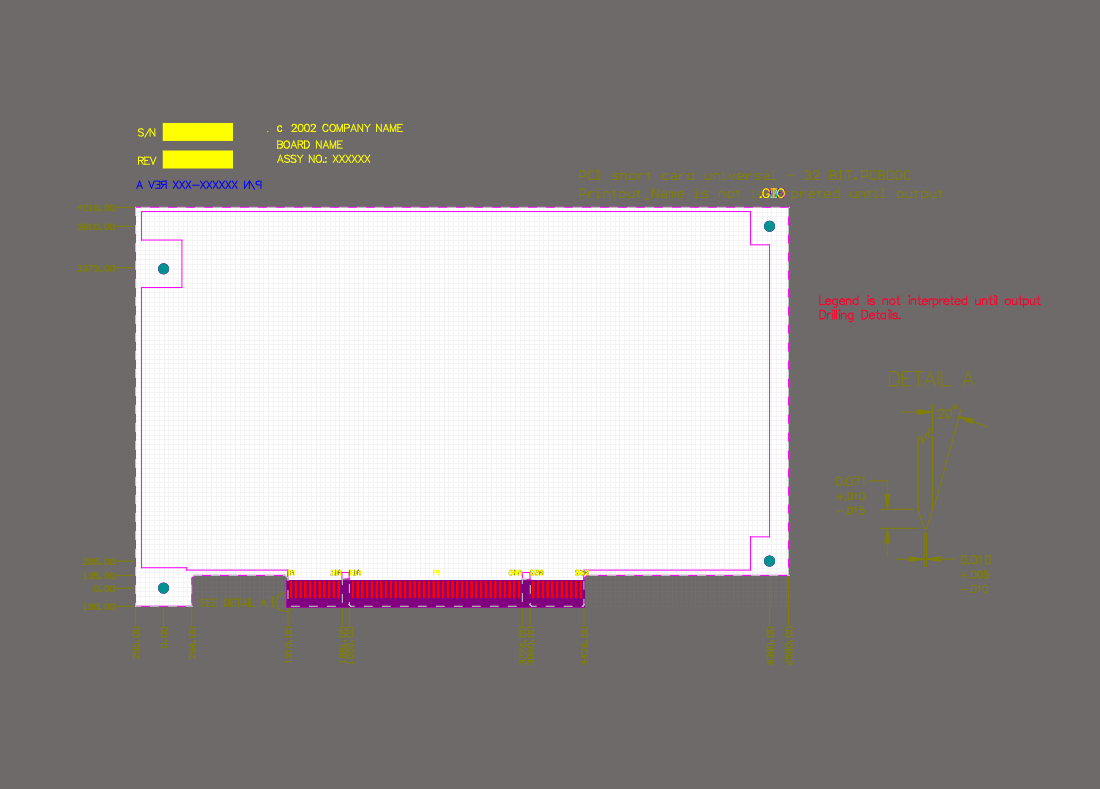

AD19PCB界面出现白色如何解决,对于我们的高版本此处位置发生变动,不在是右击option进行解决,我们使用我们的高版本,使用我们的快捷键即可。

扫码关注

扫码关注