- 全部

- 默认排序

高速PCB设计在当今的电子工程中扮演着至关重要的角色,但在高速信号传输中,阻抗设计是保证信号完整性和稳定性的重要环节,因此了解高速PCB设计的阻抗原理是很有必要的。1、阻抗的定义及类型在高速PCB设计中,阻抗是指信号线和地平面之间的电阻、电

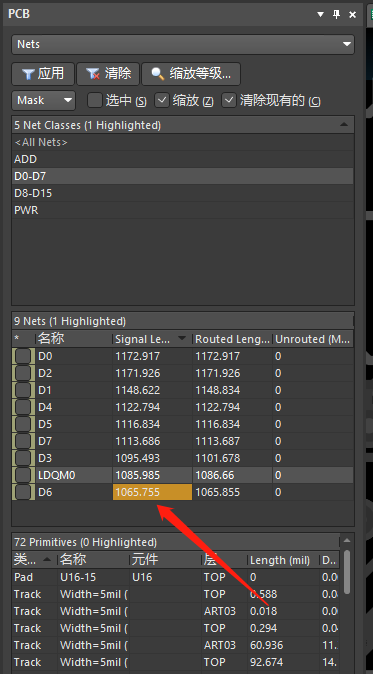

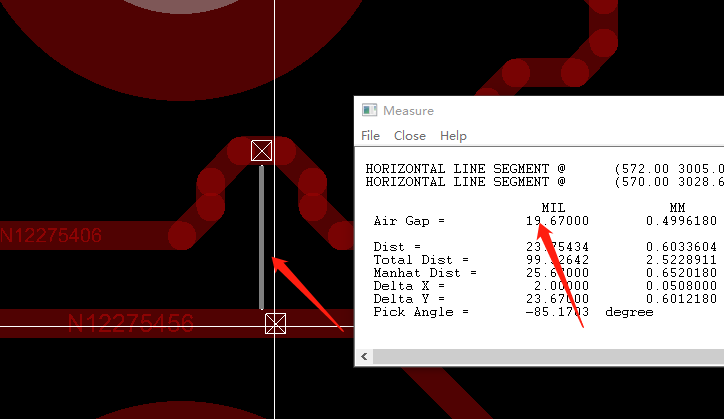

数据线等长存在误差报错2.数据线与地址线之间的分割线上要打地过孔,建议150mil一个3.这几个信号也要加入地址线的类里面进行等长(就是片选,读写,行选,列选)4.注意器件摆放不要干涉5.地网络应该就近打孔,与第二层的地平面相连电源网络也同

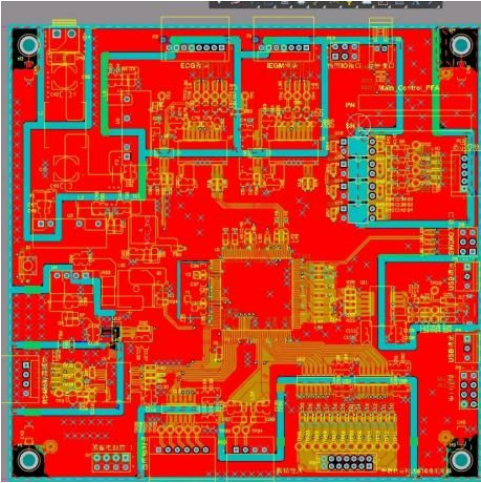

在PCB布线中,地线和电源线的规划和布局非常重要,可以影响电路的稳定性、抗干扰能力和信号质量。下面是一些常见的规划和布局建议:分离地平面:将地线分为模拟地和数字地两个区域,并使用两个独立的地平面来布线。这样可以防止模拟信号和数字信号间的互相

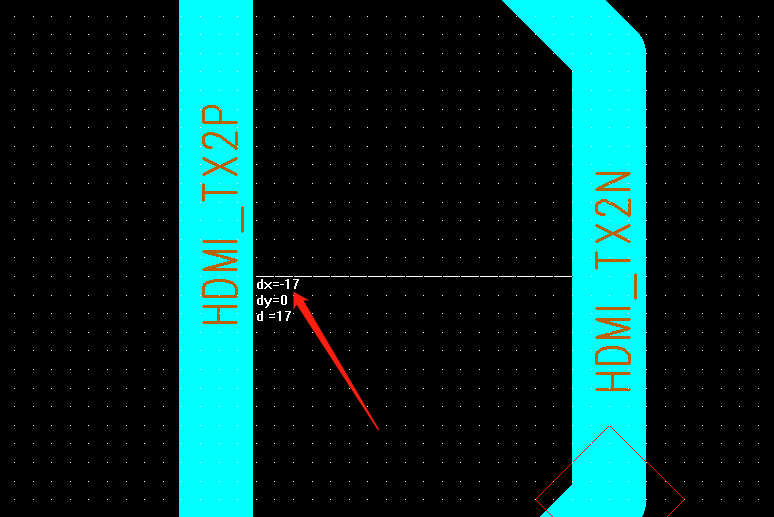

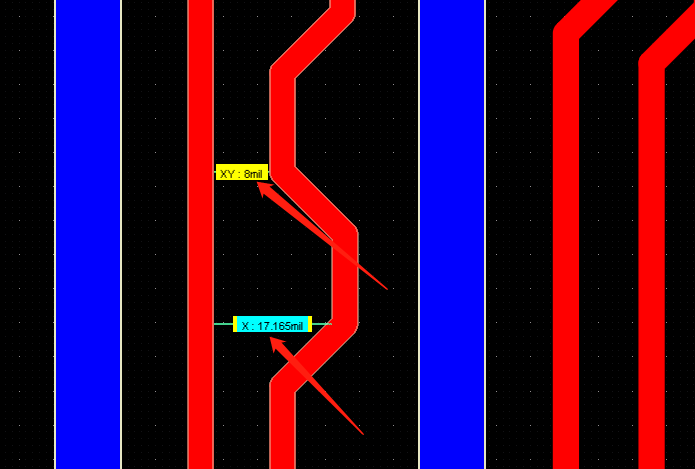

差分对内等长凸起高度不能超过线距的两倍2.地网络尽量在地平面层铺铜进行处理3.TX和RX需要创建等长组进行等长4.注意器件摆放不要干涉5.注意电源要尽量满足载流,线宽保持一致以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解P

跨接器件旁边要尽量多打地过孔,地分割间距最少1.5mm2.网口差分要进行对内等长,误差5mil3.模拟信号走线需要加粗4.地网络要就近打孔,回流到地平面5.反馈信号压迫从电容后面取样,走线要加粗6.注意数据线之间等长需要满足3W规则7.等长

PCB设计,细节要牢记,技巧规范,别忘记。元件选择,要慎重权衡,性能优化,细节考虑。电路布局,尺寸精确,差分信号,清晰准确。地平面铺,阻抗匹配,多层堆叠,功耗降低。信号路径,长度平等,串扰减小,信噪比增。参考设计,莫忽略,静电防护,接地要密

差分线对内等长凸起高度不能超过线距的两倍2.差分对内绕等长绕一边即可3.走线需要优化一下,尽量不要走任意角度4.差分出线需要优化一下5.存在开路6.地网络尽量就近打孔连接到地平面走线尽量不要超过器件外框丝印,走线离焊盘太近,后期容易短路差分

在PCB设计过程中,若是在电源平面或地平面的分割处理不当,很容易导致平面的不完整,信号走线时,其参考平面将出现在一个电源面跨接到另一个电源面,这种现象叫做信号跨分割。跨分割对低速信号影响不大,但在高速数字信号系统重影响很大,所以电子工程师该

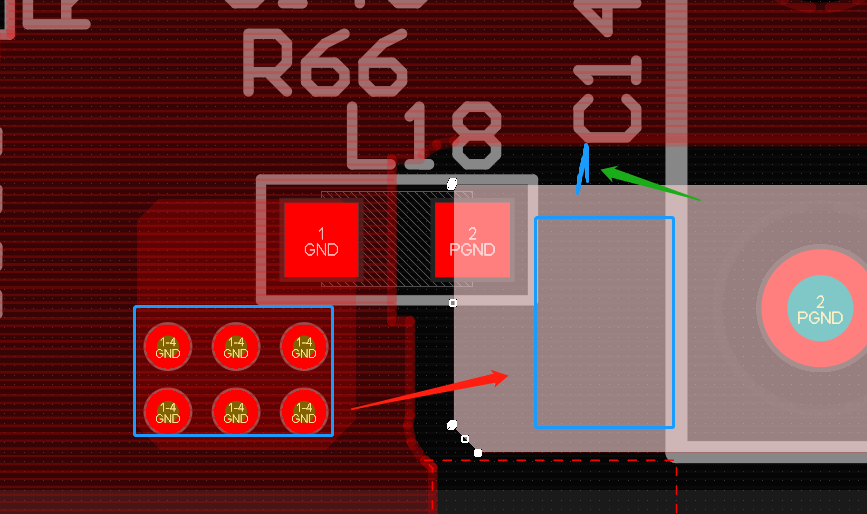

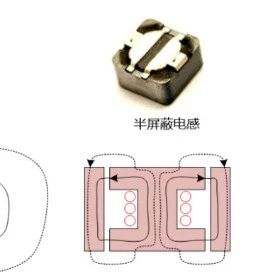

电感下方到底要不要铺铜?

PCB设计,电感下面怎么处理?针对不同类的产品,处理的方式也有所不同,一直以来,都是有不同看法的。电感通过交变电流,电感底部铺铜会在地平面上产生涡流,涡流效应会影响功率电感的电感量,涡流也会增加系统的损耗,同时交变电流产生的噪声会增加地平面的噪声,会影响其他信号的稳定性。在EMC方面来看,在电感底部

差分线对内等长凸起高度不能超过线距的两倍2.存在开路3.注意差分需要进行对内等长,误差5mil4.注意等长尽量不要直角,建议钝角,后期自己优化一下5.后期自己在地平面和电源平面指定网络进行连接6.差分需要按照阻抗线距走,后期自己注意一下以上

扫码关注

扫码关注