- 全部

- 默认排序

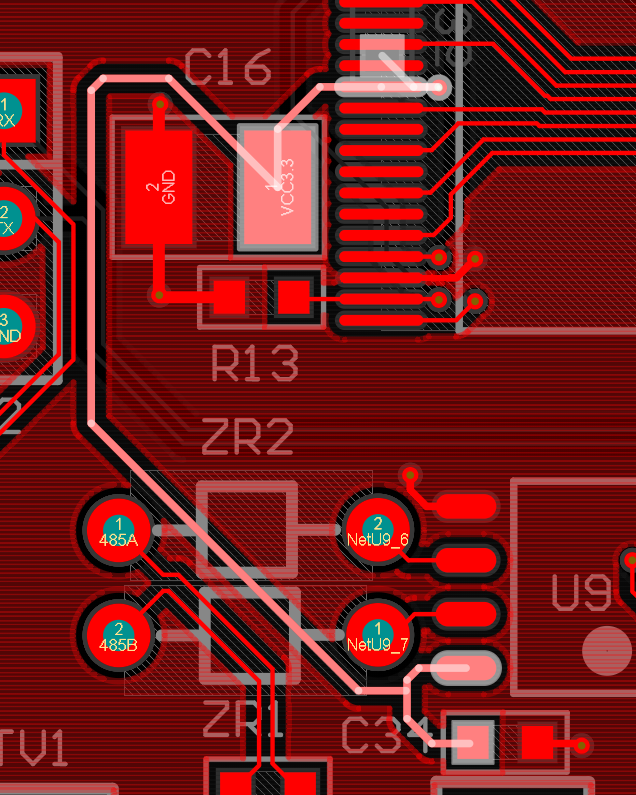

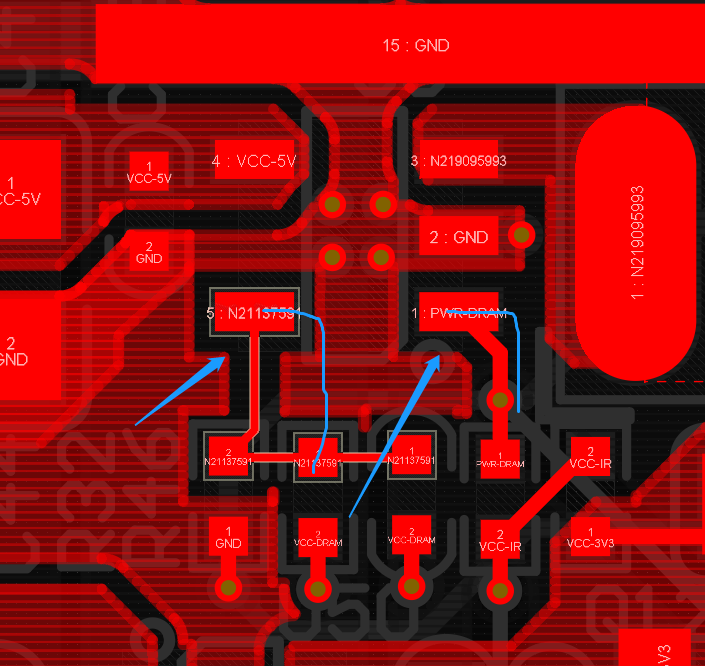

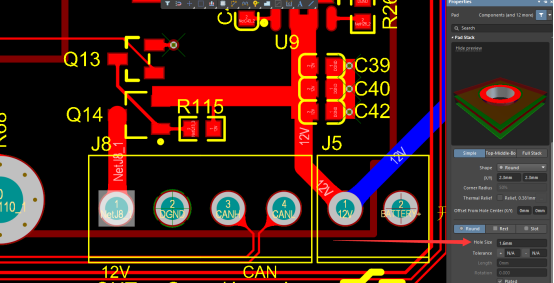

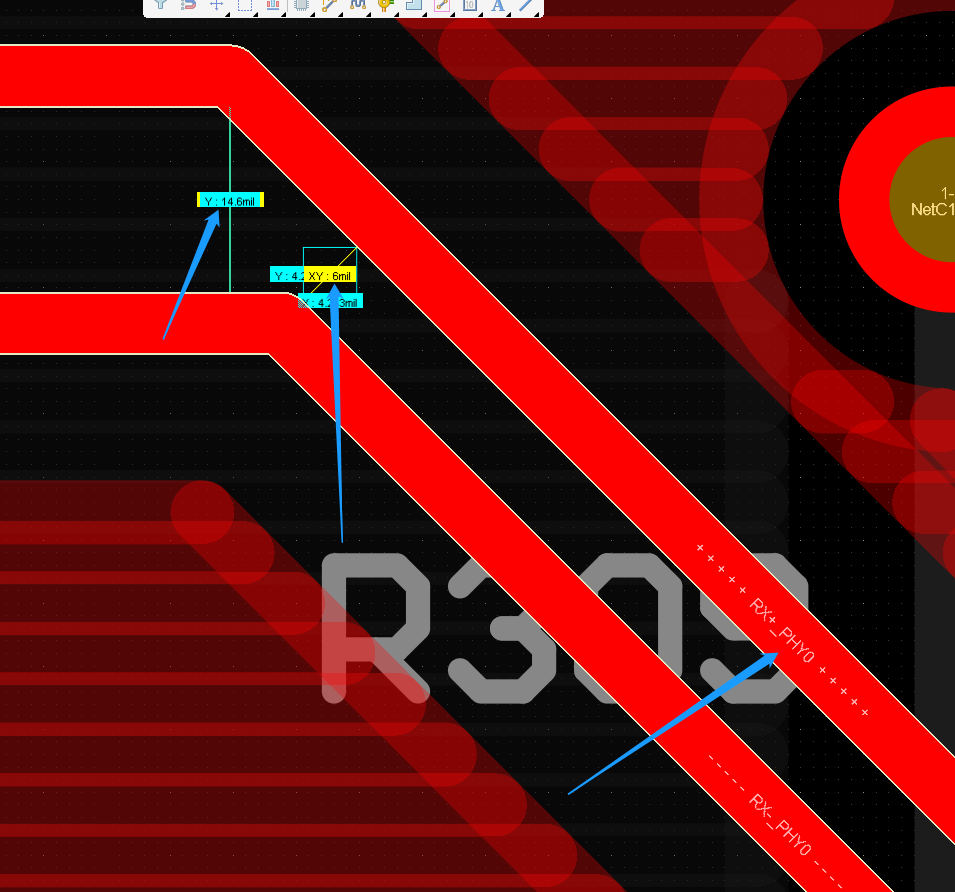

电源网络就近打孔即可2.晶振包地多打地过孔,晶振下面尽量不要走线3.VGA属于模拟信号,走线需要加粗,并包地处理,下面不要穿其他信号线4.没有添加网口4对差分的class5.差分对内等长误差5mil6.变压器需要所有层挖空7.确认一下此处是

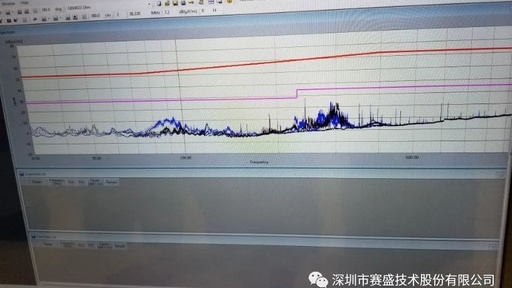

合作概要合作单位:国内某著名合资车厂问题点:一款混合动力车 GB 18387、GB 14023摸底测试未通过关键点:4月26号必须全部测试通过, 5月10日要取得公告整改时长:原计划7天,实际3天完成整改地点:襄阳试验场24小时支持热线:13510538235合作过程4月中旬,某车厂通过老客户介绍找

焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊2.天线一般需要加粗到20mil,天线下面不要走线,周围多打地过孔3.网口差分需要进行对内等长,误差5mil4.HDMI需要差分对间等长,误差10mil5.网口的其他信号都需要

差分线处理不当,锯齿状透气高度不能超过线距的两倍2.注意地址线等长需要满足3W规则3.注意器件摆放不要干涉1脚标识4.器件干涉以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:htt

DIP就是插件,采用这种封装方式的芯片有两排引脚,可以直接焊在有DIP结构的芯片插座上或焊在有相同焊孔数的焊位中。其特点是可以很方便地实现PCB板的穿孔焊接,和主板有很好的兼容性。但是由于其封装面积和厚度都比较大,而且引脚在插拔过程中很容易

在PCB设计中,布线是完成产品设计的重要布置,可以说前面的准备工作都是为了保证布线而做的,而且在整个PCB中,以布线的设计过程限定最高、技巧最细、工作量最大,非常考验工程师的功力,所以如果工程师遇到数字电路和模拟电路的共地处理,该如何做好布

PCB板的布线设计过程是一个复杂而又简单的过程,要想很好掌握布线,电子工程师需要经过多次项目设计多次试验学习积累经验,而EDA工具的自动布线功能只能帮工程师缩短一些时间,工程师需要刻苦学习巩固基础,所以今天我们阿里学习如何为电源和地线做好布

概述MAX V系列低成本和低功耗CPLD提供更大的密度和每占地面积的I/O。MAX V器件的密度从40到2210个逻辑元件(32到1700个等效宏单元)和多达271个I/O,为I/O扩展、总线和协议桥接、电源监控和控制、FPGA配置和模拟I

轻轻地我将离开你,请将眼角的泪拭去没有你的日子里,我会更加珍惜自己没有我的岁月里,你要保重你自己新品一小眼睛无线通信5G开发系统高性能双发双收新品二SDR2.0开发板全新升级

差分走线不满足间距2.差分出线要尽量耦合,走线不要有直角差分走线都存在问题,自己后期重新优化一下3.网口差分要进行对内等长,误差5mil5.pcb上存在开路6.线宽尽量保持一致7.时钟信号包地可以在地线上多打地过孔8.确认此处是否满足载流9

扫码关注

扫码关注