- 全部

- 默认排序

前期为了满足各项设计的要求,我们会设置很多约束规则,当一个PCB单板设计完成之后,通常要进行DRC(Design Rule Check)检查。DRC检查就是检查设计是否满足所设置的规则。一个完整的PCB设计必须经过各项电气规则检查。常见的检查项包括间距、开路以及短路的检查,更加严格的还有差分对、阻抗线等检查。

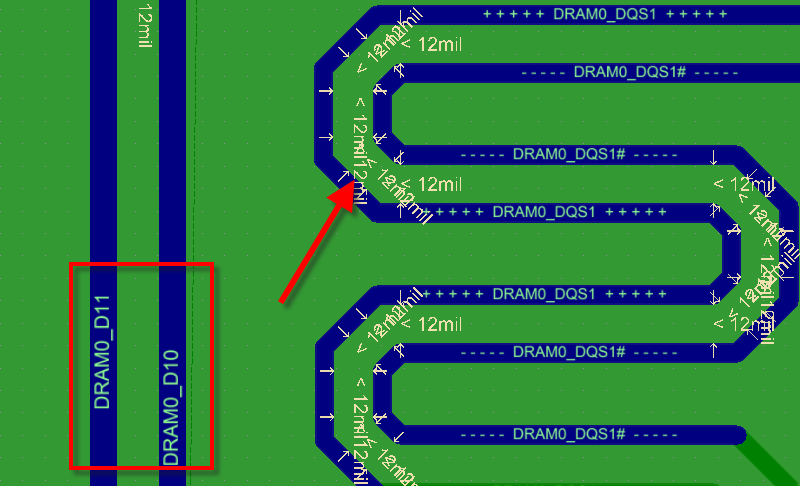

PCB设计:检查线间距时差分间距报错的处理方法 为了尽量减小单板设计的串扰问题,PCB设计完成之后一般要对线间距3W规则进行一次规则检查。一般的处理方法是直接设置线与线的间距规则,但是这种方法的一个弊端是差分线间距(间距设置大小不满足3W规则的设置)也会DRC报错,产生很多DRC报告,难以分辨,如图12-23所示。

为了尽量减小单板设计的串扰问题,PCB设计完成之后一般要对线间距3W规则进行一次规则检查。一般的处理方法是直接设置线与线的间距规则,但是这种方法的一个弊端是差分线间距(间距设置大小不满足3W规则的设置)也会DRC报错,产生很多DRC报告,难以分辨

【摘要】在某单板开发工作中,高速信号线非常多,为了保证单板的EMI性能,在PCB布线中,尽可能保证信号线走内部信号层,防止因为过多表层高速信号线产生的EMC问题无法定位。但是该方案带来的直接问题是高速信号线跃层过多,过孔较多,极大的增加了信号线的插入损耗,影响了信号完整性。在本单板设计中,为了兼顾性

在单板设计中,需要密切关注接地部分,其中接口器件的接地是至关重要的,它直接影响到系统的稳定性和电磁兼容性,不当的接地设计可能导致信号质量下降,出现误码、丢包等,还可能成为电磁干扰源,向外辐射噪声。1、分割接口地单独划分出一块区域作为接口地,

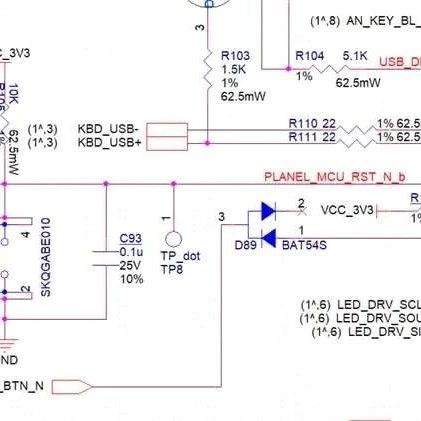

FPGA的IO用于做外部的MCU的复位功能,导致MCU内部复位失效问题详细描述为了方便在板卡板卡复位,我们的硬件工程师在做单板设计时,把MCU的复位IO 连接了到FPGA,可以通过FPGA来复位板卡的MCU。但是测试时发现,如果是单板状态,可以顺利下载固件,但是如果是集成情况下无法正常下载固件,且看

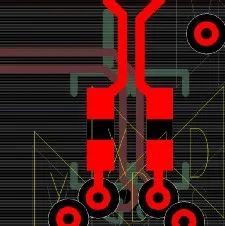

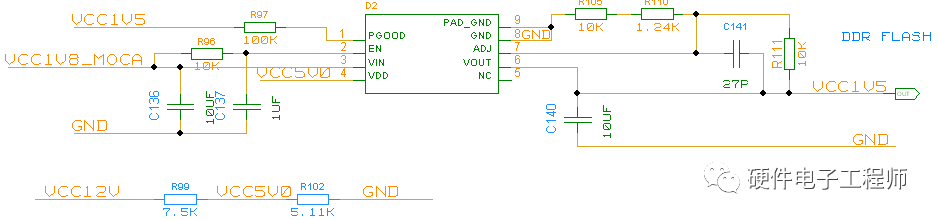

【摘要】本文介绍了曾经趟过的那些坑之DCDC调试。在调试过程中,遇到的RT9018电源芯片的上电故障的分析、定位和解决方法,对产生的故障的原因和解决问题的思路做了简要介绍。1、问题现象图1 RT9018及其外围电路如图1所示为RT9018及其外围电路,在单板设计中,使用1.8V作为输入和使能信号,V

随着新技术带来的组装密度的大幅度增加,随着用户对设计生产周期不断缩短的需求,随着电子产品可靠性要求的提高及产品外包模式的实施,有力地推动着可制造性设计的发展。因此,设计师必须要具备DFM并行设计能力,掌握工艺规则和遵循禁限用工艺,让电路设计与可制造性要求高度匹配。

扫码关注

扫码关注