- 全部

- 默认排序

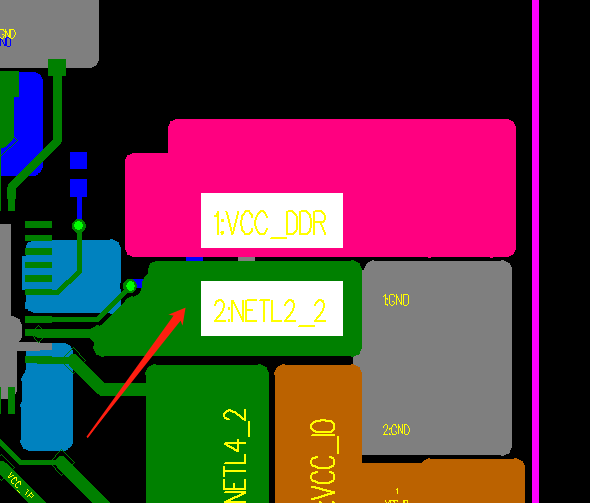

电感底部不要放置器件:可以吧电阻电容放置到中间IC的底部。电感内部也需要挖空处理:DCDC电源主干道建议铺铜处理满足其载流大小:LDO 电路部门扇孔注意过孔对齐:走线不要直角:LDO电源信号尽量拉出焊盘就加粗,不要拉出很多之后再去加粗:以

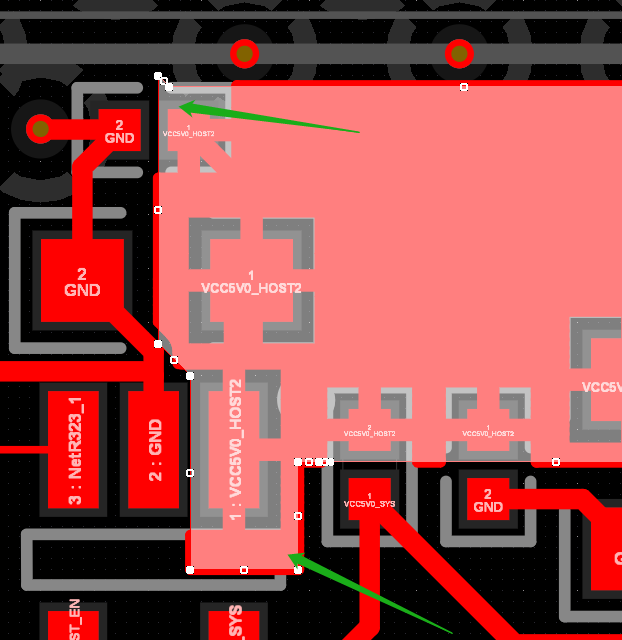

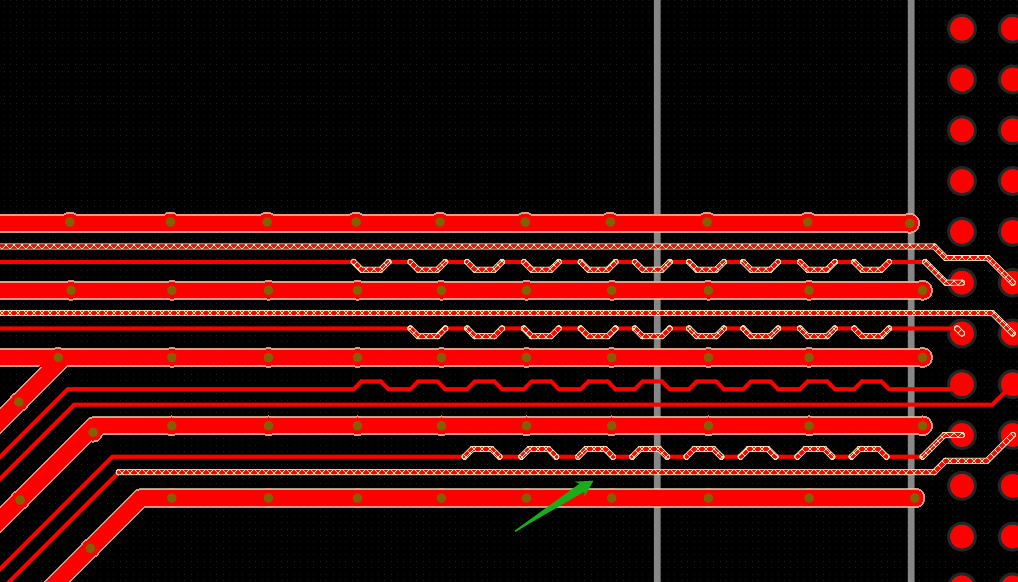

USB3.0:铺铜不要出现直角以及尖角,需要钝角,都修改下:差分没有耦合走线,重新走线:差分打孔不符合规范,重新扇孔下:走线没连接的删除掉:差分都没有注意耦合走线,都要检查修改:都没有耦合不符合规范。差分对内等长误差为5MIL:自己修改以上

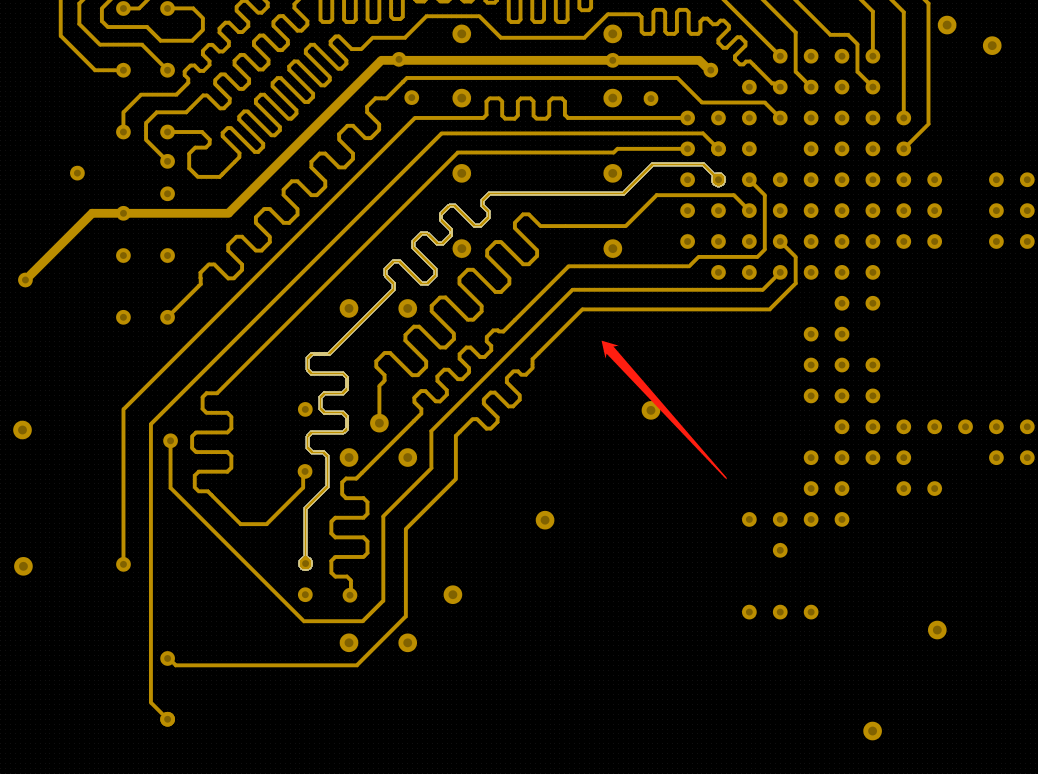

注意大电感左右摆放对齐对称,你这样自己看下有没有设计感:电感底部不能放置器件也不能走线,自己修改:过孔堆在一起了,注意间距:电感内部要挖空:这一路的DCDC管脚输入输出就有问题,按照原理图上的来进行PCB设计,建议看下视频看完了之后再去PC

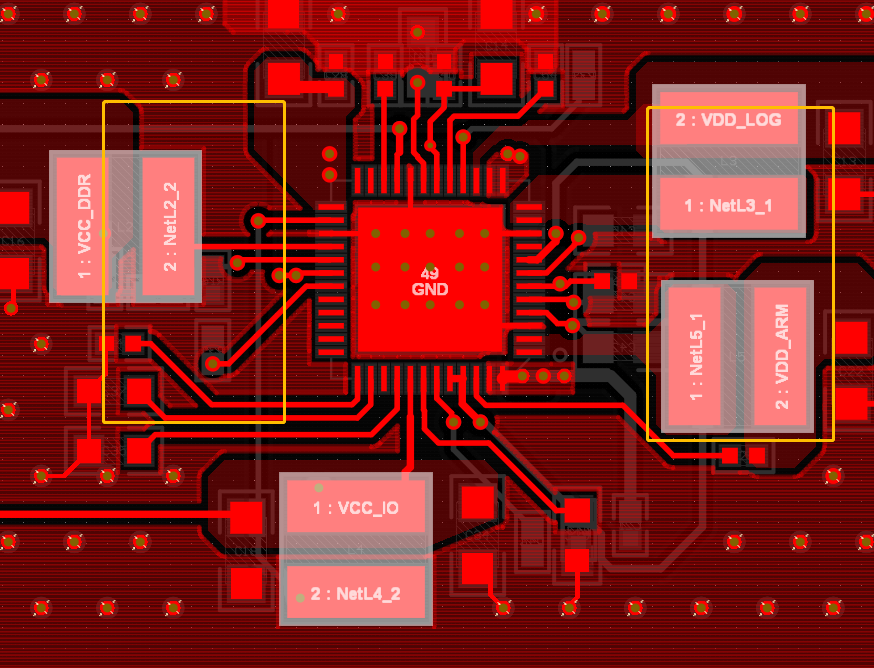

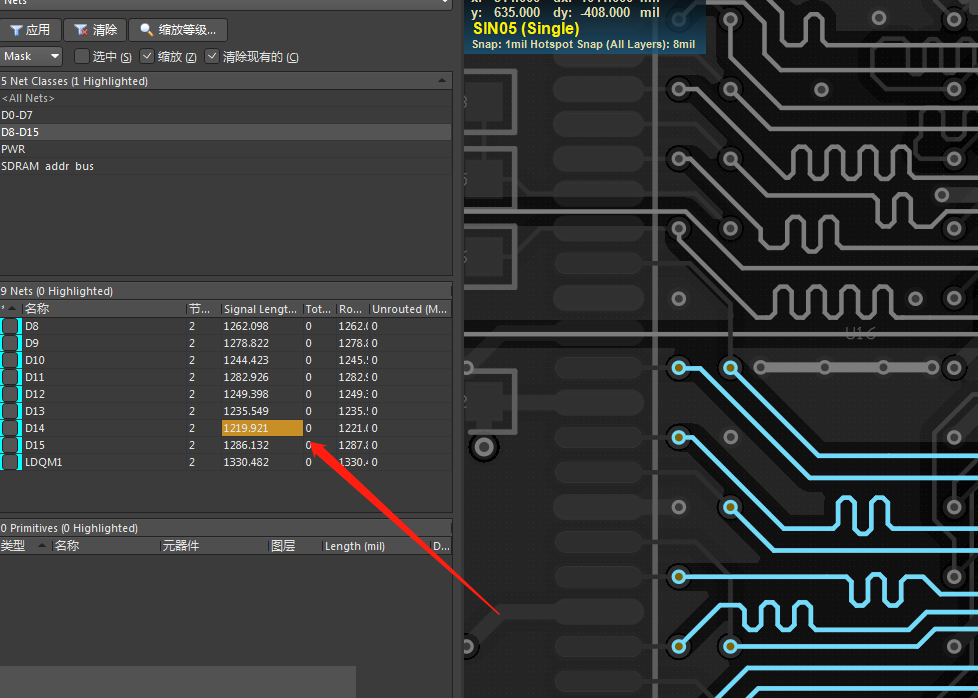

组内等长误差还存在报错:自己注意修改下等长,让组内误差没有报错。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.com/item.htm?s

注意走线不要直角:这里可以直接GND焊盘扇孔出来连接即可。这里的铜皮跟焊盘没连接是因为铜皮属性没有设置,不需要再放置填充了:铜皮属性设置第二项然后重新灌下此块铜皮就跟同网络的焊盘连接了。此处电源跟地的过孔数量要对应上:其他的没什么问题。以上

下面这一组数据线尽量还可以稍微紧凑点:等长可以咬合等长,比较节省空间并且也比较美观:平面分割的分割带建议宽度20MIL:其他的没什么问题,等长尽量可以紧凑并且美观点。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训

SATA:可以直接把差分规则里面的耦合度设置大一点就不会报错了:此处差分直接走顶层不用扇孔了:MIPI:注意差分组跟组等长误差为10MIL:此对差分对内等长误差是5MIL:以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PC

还存在网络并未连接完全,自己后期铺地铜进行连接:注意调整下器件位号丝印,不要覆盖在焊盘上或者是重叠,直接就近放在器件旁边整齐排列即可:过孔散热焊盘上的开窗即可,其他的盖油处理:铺铜注意不要有这种尖角:电感内部注意挖空处理:自己看下过孔都没网

建议顶底层可以铺上大地铜:铜皮注意这种尖角:注意此处的铜皮 不要铺到晶振内部,晶振需要净空:晶振包地处理沿着器件丝印边框打孔:跨接器件两边可以多打地过孔:差分打孔换层的两侧可以放置地过孔,缩短回流路径:此处晶振净空调整下:等长之间注意保持3

全站最新内容推荐

- 1加码技术,打破困境,PSPice电路仿真助你解锁职场新高度!

- 2简谈稳压二极管和普通二极管的区别

- 3贴片元件如何拆卸及焊接?

- 4盘点电子工程师必须了解的21个电路

- 5英伟达GB300芯片受阻,存在过热问题

- 6WARELEO李增原创H04课程大纲的安排课程中内容及工具及课程的重点学习办法的讲解

- 7WARELEO李增原创H03根据自己的关注知识点和所需要的知识来选择需要的图书包邮递

- 8WARELEO李增原创H02理工男生李老师的介绍从51单片机驱动到FPGA到仿真设计之路

- 9WARELEO李增原创H01信号电源完整性设计与HFSS射频天线设计仿真验证研修课程主题

- 10WARELEO李增:反射仿真的信号观察办法及时域串扰的仿真设置及观察技巧

扫码关注

扫码关注