- 全部

- 默认排序

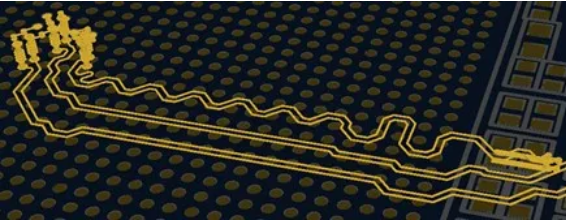

差分信号和普通的单端信号走线相比,最明显的优势体现在以下三个方面: a.抗干扰能力强,b.能有效抑制EMI,c.时序定位精确, 那么在实际设计当中,Altium Designer软件当中差分是怎么定义添加的,又是怎么设置相关规则的呢?我们一起来学习下吧!

凡亿深圳pcb培训讲解PCB设计走线时注意事项总结如下: 1. 一般规则 1.1 PCB板上预划分数字、模拟、DAA信号布线区域。 1.2 数字、模拟元器件及相应走线尽量分开并放置於各自的布线区域内。 1.3 高速数字信号走线尽量短。 1.4 敏感模拟信号走线尽量短。 1.5 合理分配电源和地。

我们PCB中的信号都是阻抗线,是有参考的平面层。但是由于PCB设计过程中,电源平面的分割或者是地平面的分割,会导致平面的不完整,这样,信号走线的时候,它的参考平面就会出现从一个电源面跨接到另一个电源面,这种现象我们就叫做信号跨分割。跨分割的现象如图1-52所示。

在高速PCB设计中,差分信号的应用越来越广泛,这主要是因为和普通的单端信号走线相比,差分信号具有抗干扰能力强、能有效抑制EMI、时序定位精确的优势。作为一名(准)PCB设计工程师,我们当然需要充分理解差分信号!

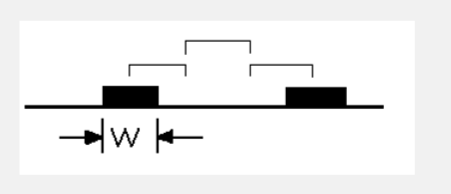

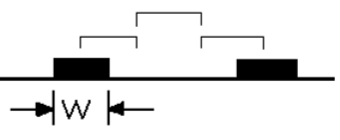

答:为了信号走线的质量,不产生串扰,我们保持信号走线与信号走线之间的间距为3倍线宽,这个间距指的是走线的中心到中心的间距,因为我们的线宽英文是width,所以这个规则我们通常就叫做3W原则。当我们的走线的中心间距不少于3倍线宽时,可以保证70%的线间电场不互相干扰,如果信号需要达到98%的线间电场不互相干扰,可以使用10W规则。3W原则是一种设计者无须其他设计技术就可以遵守PCB布局的原则。但这种设计方法占用了很多面积,可能会使布线更加困难。使用3W原则的基本出发点是使走线间的耦合最小。这种原则

答:我们PCB中的信号都是阻抗线,是有参考的平面层。但是由于PCB设计过程中,电源平面的分割或者是地平面的分割,会导致平面的不完整,这样,信号走线的时候,它的参考平面就会出现从一个电源面跨接到另一个电源面,这种现象我们就叫做信号跨分割。跨分割的现象如图1-52所示。跨分割,对于低速信号,可能没有什么关系,但是在高速数字信号系统中,高速信号是以参考平面作为返回路径,就是回流路径。当参考平面不完整的时候,会出现如下影响:Ø 会导致走线的的阻抗不连续;Ø 容易使信号之间发生串扰;Ø

答:高速信号、低速信号的区分取决于以下两个因素:信号的有效频率F;信号走线的有效长度U。一般来说,信号的有效频率F约等于信号频率的5倍,信号走线的有效长度等于U=(0.35/F)/D,其中D是PCB上的走线延迟,在FR4的材质中D约等于180,得出的结论就是在信号走线的长度小于有效长度的1/6,信号为低速信号;反之,信号为高速信号。所以我们判定信号是否为高速、低速信号的步骤如下:Ø 获取信号的有效频率与信号走线的长度;Ø 计算出信号走线的有效长度;Ø 比较信号长度与

答:端接,Butt Joint,是指消除信号反射的一种方式。在高速PCB设计中,信号的反射将给PCB的设计质量带来很大的负面影响,采用端接电阻来达到线路的阻抗匹配,是减轻反射信号影响的一种有效可行的方式。端接,分为一下两类:Ø 源端端接,接在信号源端或信号发送端的端接,一般与信号走线串接;Ø 终端端接,接在信号终端或信号接收端的端接,一般与信号走线并接。源端端接的优点是接供较慢的上升时间,减少反射量,产生更小的EMI,从而降低过冲,增加信号的传输质量。我们在PCB设计中处理源

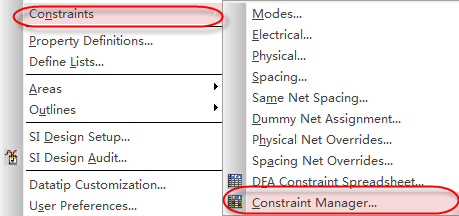

答:添加完成走线的阻抗线宽之后,这样PCB板上信号走线就会按照所设置的物理走线线宽进行。除了添加走线的线宽之外,还需要添加间距规则,来规范不同元素之间的间距,满足生产的需求,添加间距的操作步骤如下所示:

答:为了信号走线的质量,不产生串扰,我们保持信号走线与信号走线之间的间距为3倍线宽,这个间距指的是走线的中心到中心的间距,因为我们的线宽英文是width,所以这个规则我们通常就叫做3W原则。

全站最新内容推荐

- 1加码技术,打破困境,PSPice电路仿真助你解锁职场新高度!

- 2简谈稳压二极管和普通二极管的区别

- 3贴片元件如何拆卸及焊接?

- 4盘点电子工程师必须了解的21个电路

- 5英伟达GB300芯片受阻,存在过热问题

- 6WARELEO李增原创H04课程大纲的安排课程中内容及工具及课程的重点学习办法的讲解

- 7WARELEO李增原创H03根据自己的关注知识点和所需要的知识来选择需要的图书包邮递

- 8WARELEO李增原创H02理工男生李老师的介绍从51单片机驱动到FPGA到仿真设计之路

- 9WARELEO李增原创H01信号电源完整性设计与HFSS射频天线设计仿真验证研修课程主题

- 10WARELEO李增:反射仿真的信号观察办法及时域串扰的仿真设置及观察技巧

扫码关注

扫码关注