- 全部

- 默认排序

随着科技进步和需求不断提升,高速PCB和硬件在全球半导体行业具有重要地位。高速PCB提供了高频率信号传输和数据处理的技术支持,为通信和计算设备的快速发展奠定基础。而硬件作为电子设备的核心组成部分,其性能和功能直接影响产品的竞争力和市场表现。

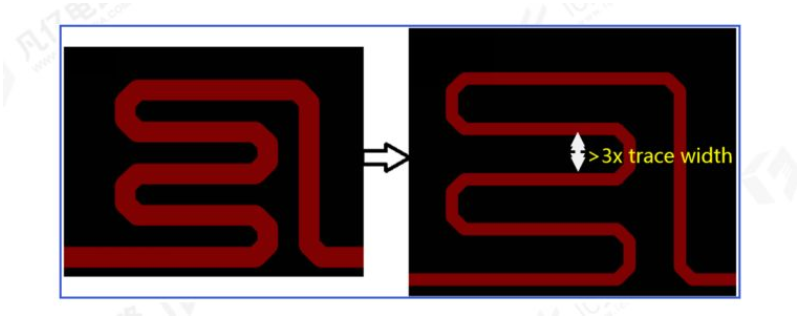

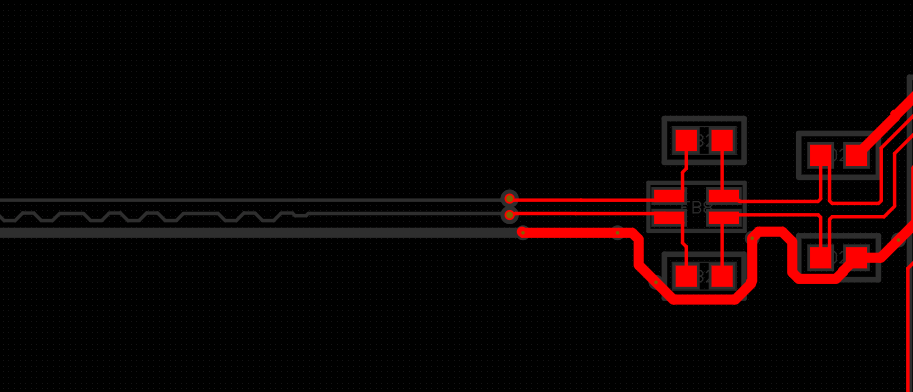

1、在做 PCB 设计时,为了满足某一组所有信号线的总长度满足在一个公差范围内,通常要使用蛇形走线将总长度较短的信号线绕到与组内最长的信号线长度公差范围内,这个用蛇形走线绕长信号线的处理过程,就是我们俗称的 PCB 信号等长处理。等长的目标

高速PCB设计是很多电子工程师在职业发展时会自主学习的重要技能,而走线方式是高速信号传输中的关键记步骤,在高速PCB设计中,合理的走线方式将提高电路板的信号完整性,抑制信号干扰,保证了电路性能的稳定和可靠。1、直线走线方式直线走线方式毫无疑

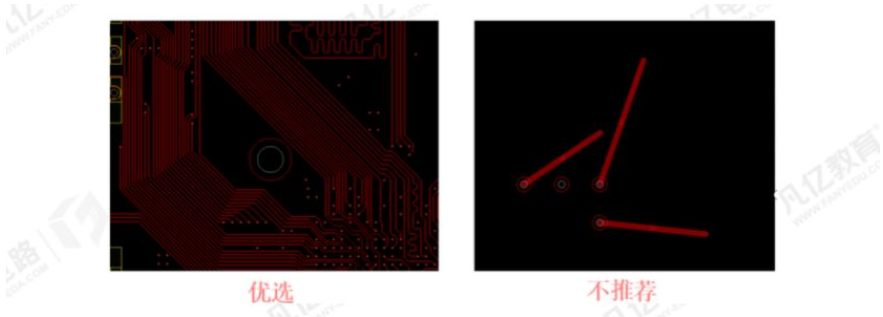

1、走线长度应包含过孔和封装焊盘的长度。2、布线角度优选135°角出线方式,任意角度出线会导致制版出现工艺问题。图1 PCB布线的角度3、布线避免直角或者锐角布线,导致转角位置线宽变化,阻抗变化,造成信号反射,如图2所示。图2 走线的锐角与

EMC辐射超标如何解决?

在电子工程领域,电磁兼容性(EMC)问题永远是电子工程师的学习难点,其中之一是EMC辐射超标,导致EMC辐射超标的原因有很多种,如接口滤波不好、结构屏效低、电缆设计有缺陷等,那么如何解决?一般来说,EMC辐射问题主要归于电子设备内部高速信号

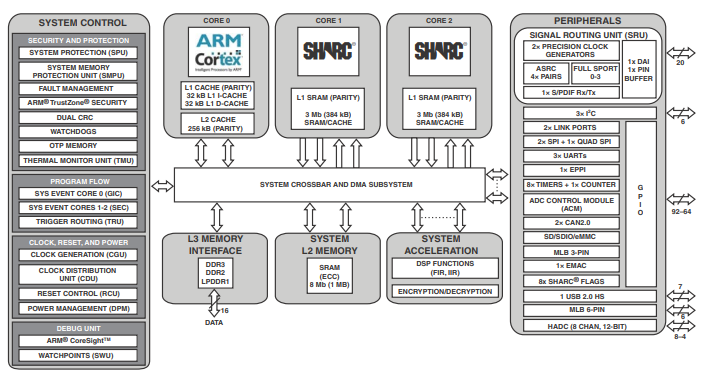

ADSP-2157x处理器属于SHARC®系列产品。ADSP-2157x SHARC处理器属于单指令多数据(SIMD) SHARC系列数字信号处理器(DSP),采用ADI公司的Super Harvard架构。这些32/40/64位浮点处理器

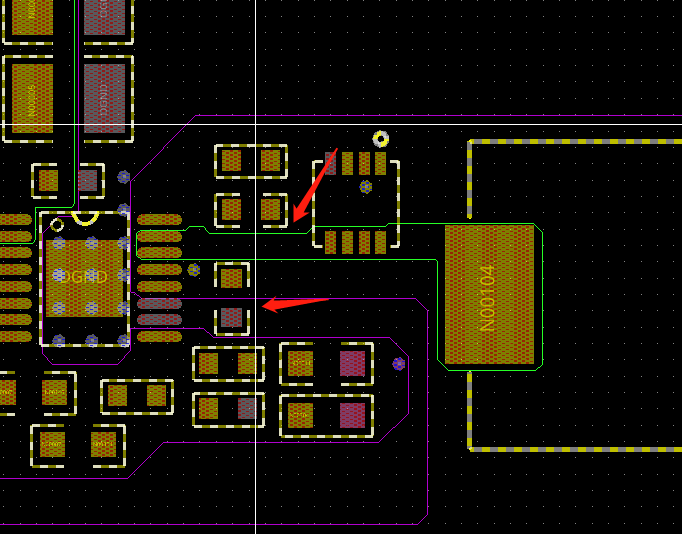

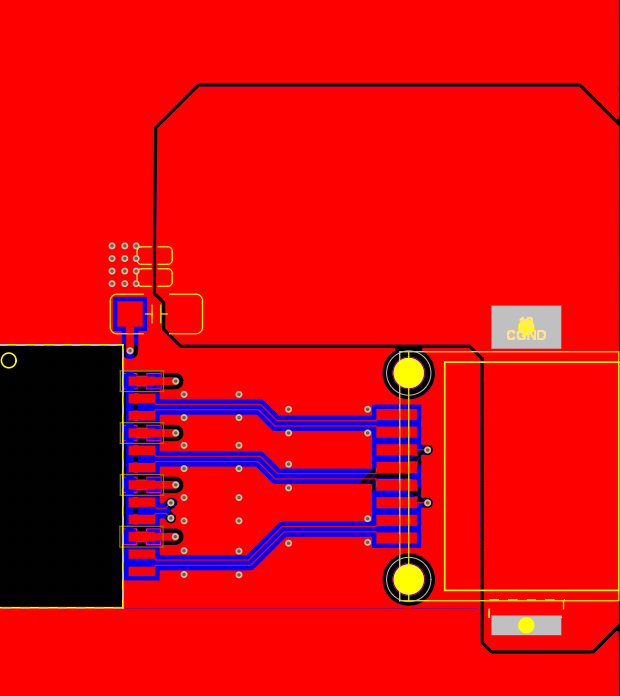

配置电阻电容可以稍微移动下,留出空间给主干道铺铜:注意电感当前层内部挖空处理:反馈信号没有连接:第二路DCDC的电源跟地都没有处理,都是需要处理的 :以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链

为了减少在高速信号传输过程中的反射现象,必须在信号源、接收端以及传输线上保持阻抗的匹配。单端信号线的具体阻抗取决于它的线宽尺寸以及与参考平面之间的相对位置。特定阻抗要求的差分对间的线宽/线距则取决于选择的PCB叠层结构。由于最小线宽和最小线

注意差分信号包地包全:差分走线可以优化对称点:差分连接进入过孔的 看是否有多余线头 优化走线:此处差分对内等长的走线不满足规范:此处相同网络的GND铜皮并未跟焊盘连接:铜皮属性设置第二项 然后重新灌铜。CC1 CC2 管脚需要加粗走线:对内

机壳地与电路地需要间距2MM:跨接器件两边多打点地过孔:走线需要连接到焊盘中心:RX TX信号分组 组跟组用GND走线隔开:以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:http

扫码关注

扫码关注