- 全部

- 默认排序

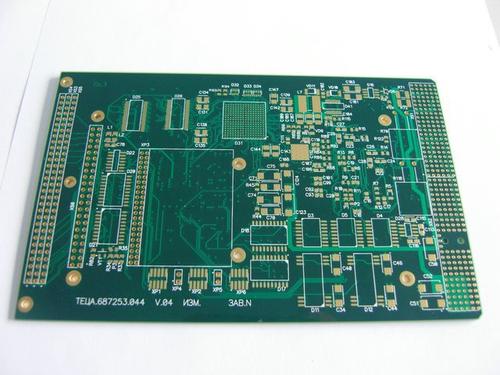

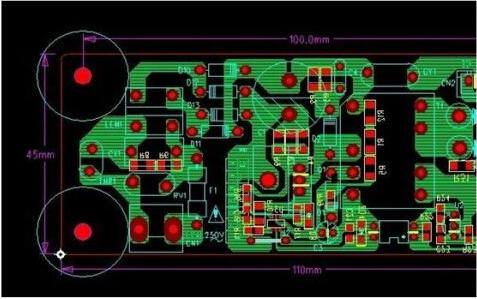

纵观成功的电子产品,基本都要具备五个特点:一 性能稳定; 二 整体美观; 三 便于应用; 四 成本合理 ; 五 方便量产; 偏重哪一点,都不能称之为成功的产品。这五点都与pcb布局有关,换句话说,好的,合理的布局是要充分考虑以上五点的,,所以说布局是产品成功与否非常重要的一环。高速PCB设计中,布局更是重要,其合理性直接关系到后续的布线,信号传输的质量,EMI, EMC,ESD等问题,

在高速PCB电路设计过程中,经常会遇到信号完整性问题,导致信号传输质量不佳甚至出错。那么如何区分高速信号和普通信号呢?很多人觉得信号频率高的就是高速信号,实则不然。我们知道任何信号都可以由正弦信号的N次谐波来表示,而信号的最高频率或者信号带宽才是衡量信号是否是高速信号的标准。在高速PCB电路设计过程中,经常会遇到信号完整性问题,导致信号传输质量不佳甚至出错

一、8 层 Allegro T 点星型拓核心板课程详情这个是一个非常经典的 T 点星型拓核心板设计,主要采用飞思卡尔 IMX6 主控芯片,4 片DDR3 同层设计,采用 DDR3 常见的 T 点拓扑结构,讲解了 DDR3 设计的信号 class 分组,信号的同组同层及常用规则注意事项,信号完整性的规划等。

全新版本的 Altium Designer 19 来进行讲解,这个版本很多新功能及应用都有进行说明,采取的案例也不是太复杂的一个评估板来讲解,更加契合新手去学习,很完整,从创建原理图库、原理图、PCB 库到 PCB 设计的布局布线,全流程,每个器件是怎么画的?怎么摆放的?每一根线怎么拉线?哪些是电源线?哪些是信号线都是一个一个的详细讲解的,新手一般看一遍就能够自己动手做了。

此Altium Designer视频是专门针对 DDR3 设计来的,采用飞思卡尔 IMX6 主控芯片, 4 片 DDR3 同层设计,采用 DDR3 常见的 T 点拓扑结构,一个大 T 点两个小 T 点的方式。讲解了 DDR3 设计的信号 class 分组,信号的同组同层及常用规则注意事项,信号完整性的规划等,让学习者知其然知其所以然。

模拟电路设计难在哪些地方

20世纪80年代以来,数字信号处理算法和集成电路迅猛发展,虽然许多类型的信号处理已经由模拟电路转换成数字电路来实现,但是在一块芯片中,模拟电路是必不可少的。作为一个模拟电路设计师中说一下自己学习和工作中的一些心得体会。模拟电路设计比数字电路设计困难

一、PADS8层DDR3 Fly-by拓扑结构视频课程详情本pads视频课程基于飞思卡尔 i.MX6 处理器的 8层PCB设计,重点介绍 DDR3 内存的设计思路,一共四颗 DDR3,采用菊花链(Fly-By)的拓扑结构。讲解了 DDR3 设计的信号 class分组,信号的同组同层布线、信号时序等长及常用规则注意事项、信号完整性、电源完整性的规划等。

我们在用allegro进行PCB设计完成以后,都需要对一组传输的总线进行时序等长,在做时序等长的时候,分为绝对传输延迟与相对传输延迟。绝对传输延迟,顾名思义,信号传输在PCB设计中都是有一个走线的长度,我们通过设置这个信号线传输的最大值与最小值,来实现等长的方法,就称之为绝对传输延迟。

三极管的介绍及用途

三极管的介绍:三极管,全称应为半导体三极管,也称双极型晶体管、晶体三极管,是一种控制电流的半导体器件。其作用是把微弱信号放大成幅度值较大的电信号,也用作无触点开关。三极管是半导体基本元器件之一,具有电流放大作用,是电子电路的核心元件。三极管是在一块半导体基片上制作两个相距很近的PN结,两个PN结把整块半导体分成三部分,中间部分是基区,两侧部分是发射区和集电区,排列方式有PNP和NPN两种。(图一)c图一三极管主要用途:1.放大,(工作时,三极管工作在放大区)用来组成放大电路。 &n

滤波电容:在电源整流电路中,用来滤除交流成分,使其输出的直流更加的平滑。 去耦电容:在放大电路中不需要交流的地方,用来消除自激,使放大器稳定工作。 旁路电流:在电阻连接时,接在电阻两端使交流信号顺利的通过。(1)关于去耦电容蓄能作用去耦电容主要是去除高频如RF信号的干扰,干扰的进入方式是通过电磁辐射。而实际上,芯片附近的电容还有蓄能的作用,这是第二位的。如果微观来看,高频器件在工作的时候,其电流是不连续的,而且频率很高,而器件V

扫码关注

扫码关注