- 全部

- 默认排序

在高速PCB设计中,确保信号完整性是至关重要,而地过孔的布置,可以减少信号反射、串扰和电磁干扰(EMI),特别是在高速信号孔旁。合理的地过孔数量可显著改善信号质量,那么应该增加几个?1、最少数量对于高速信号(如频率超过1GHz),建议在信号

对工程师来说,最难的电路设计,莫过于信号电路,不仅需要投入大量的仪器设备,而且还考验刚才说的丰富理论及高水平实操经验,才有可能设计出符合要求的信号电路。但如果分析那些从电子小白到大佬的信号电路作品,不难发现,这些大多数工程师对信号电路的设计

相控阵天线:从军用到5G

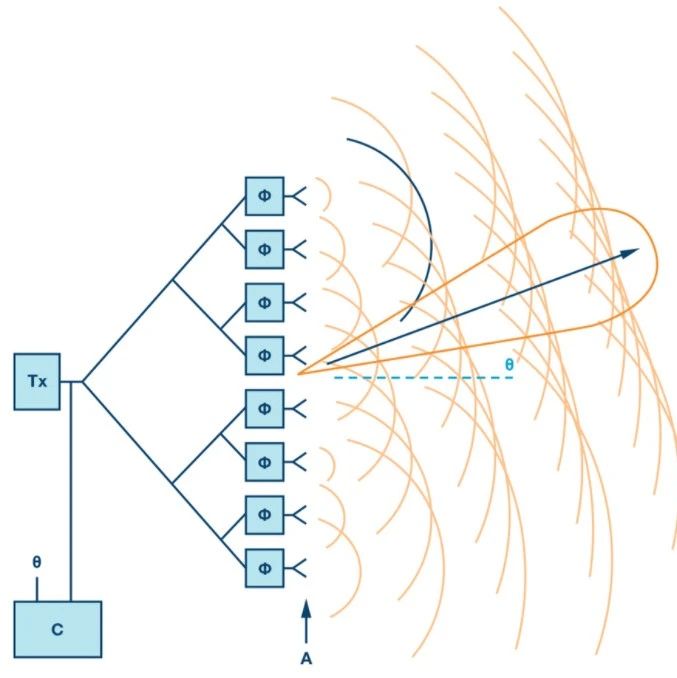

相控阵技术远非新技术,已经在各种军事应用中用了几十年了。然而如今,该技术在频段2的5G系统中的应用正迅速获得关注,这是因为该技术能改善信号强度、增益、方向性和带宽等多方面的性能。相控阵使用多个天线单元,通过改变每个单元的相对相位来控制辐射方向图或波束。通过微波传输线和功率分配器系统连接天线单元。在相

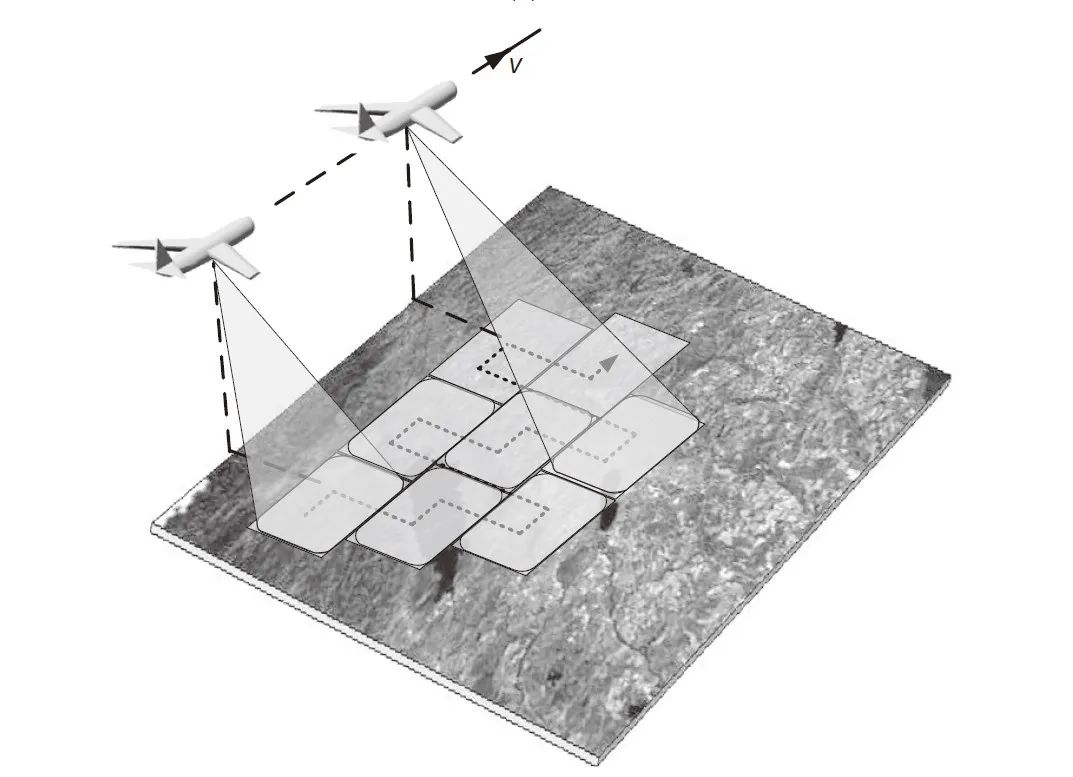

合成孔径雷达 (SAR) 是一种高分辨机载和星载遥感技术,用于对地形等场景上的远程目标进行成像。1951 年,Carl Wiley 意识到,如果在雷达沿直线路径移动时收集回波信号,则接收信号的多普勒频谱可用于合成更长的孔径,以便提高沿轨道维度的分辨率。1953 年,当一架 C-46 飞机绘制佛罗里达

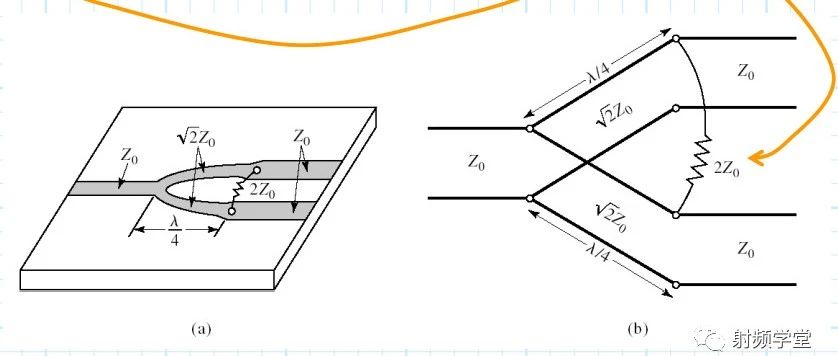

威尔金森功分器是一款比较常用的射频器件,是由射频工程师E.J. Wilkinson 在1960年的文章中提出的,这篇文章在IEEE网站上还能下载到:An N-Way Hybrid Power Divider。方便的同学可以下载学习一下。威尔金森功分器常见的使用场景是将一路信号按照一定的比例分成两路

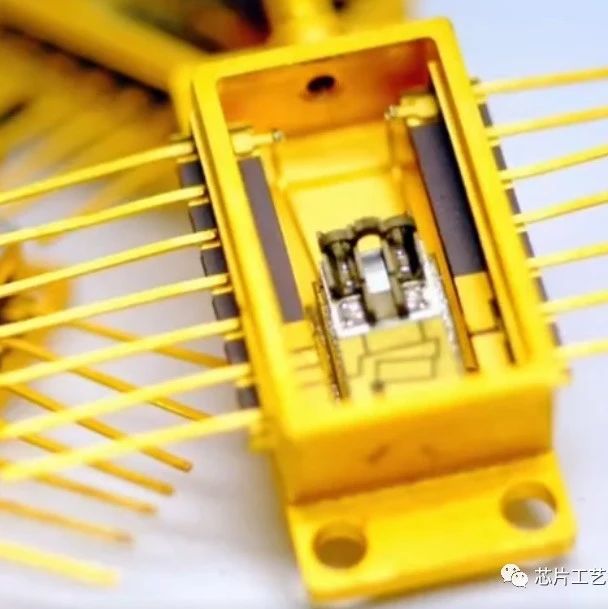

半导体激光器的热耗散功率

半导体激光器的热状态和工作方式有关,一般有三种工作方式:1) 在直流驱动下的CW连续工作;2)直流偏置在阈值附近的小信号调制;3)在脉冲状态下工作,常将具有高占空比的脉冲工作方式称为准连续QCW。 在QCW模式下的一个特立,占空比为1时就是连续工作模式,激光器所产生的热耗散功率为:IV分别为激

如果接到了关于LED调光电源的设计项目,有一定概率碰到电源频闪现象。一般来说,人眼最多感知到频率高达70Hz的光闪烁,高于该频率无法感知,因此,如果脉冲信号出现低于70Hz的低频,人眼就会感受到闪烁,一般是回路电流不到可控硅的维持电流。1、

如果学习LED照明系统,那一定对其频闪现象不陌生,频闪,即光源发出的光在视觉上呈现出的周期性明暗变化,在LED照明中,当调光电源输出的脉冲信号频率低于人眼可感知的70Hz时,频闪现象尤为明显。因此如果LED电源出现频闪现象,将对人眼造成伤害

PCB高频板材,作为现代电子工业中的关键技术材料,专为应对高频率信号传输及微波领域的需求而生。它们不仅承载着电路元件的连接,更在高速数据传输、无线通信、雷达系统等领域发挥着不可或缺的作用。1、按材质分类有机材质:包括酚醛树脂、玻璃纤维/环氧

了解芯片制造的人都知道,为了保证产品的顺利上市,流片阶段是必不可少的,而I/O(输入输出)接口的正确性与稳定性直接关系到芯片的整体性能与可靠性,如何在流片阶段确保I/O状态?下面一起来看看!1、信号强度隔离确保弱信号与强信号的模拟I/O分开

扫码关注

扫码关注