- 全部

- 默认排序

PCB元件布局思路分析

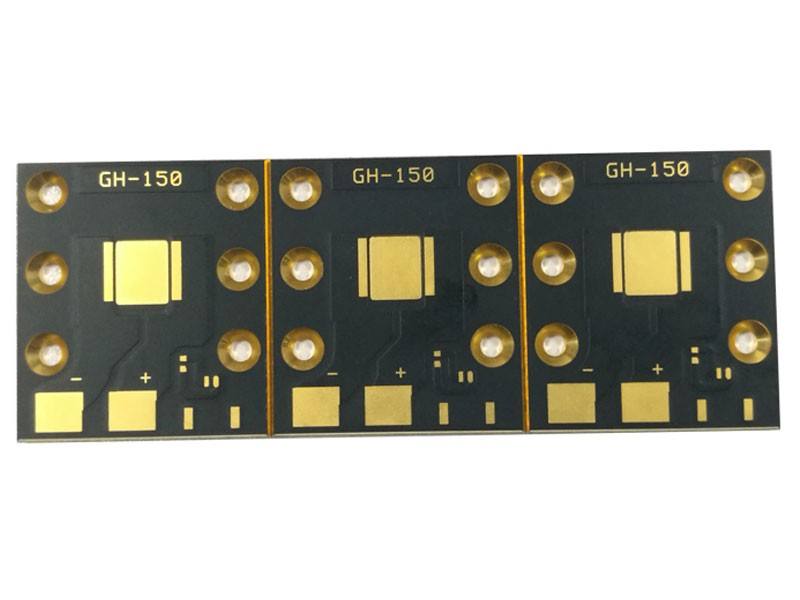

1、首先,我们会对结构有要求的器件进行摆放,摆放的时候根据导入的结构,连接器得注意1脚的摆放位置。 2、布局时要注意结构中的限高要求。 3、 如果要布局美观,一般按元件外框或者中线坐标来定位(居中对齐)。 4、 整体布局要考虑散热。 5、 布局的时候需要考虑好布线通道评估、考虑好等长需要的空间。 6、 布局时需要考虑好电源流向,评估好电源通道。 7、 高速、中速、低速电路要分开。

关于信号完整性的绪论

随着信息宽带化和高速化的发展,以前的低速PCB已完全不能满足日益增长信息化发展的需要,人们对通信需求的不断提高,要求信号的传输和处理的速度越来越快,相应的高速PCB的应用也越来越广,设计也越来越复杂。

刚大学毕业或者已经参加工作 1-2 年的你,是否慢慢的发现了很多你当初进入的行业或者目前从事的 PCB 画板行业所设计的PCB 层级过于简单,一直在 2 层低速这类板卡转悠呢? 于个人发展,前景及钱景是否和之前想象的存在差距,可能目前公司上班所学到的技能对自己职业生涯的提高已经达到了瓶颈,如何突破是你现在阶段的你急需要思考的问 题,趁自己还年轻,趁自己还冲劲的时候努力给自己寻求另外一条道路呢,要么看到前景, 那么看到钱景,促使自我“价值”提高! &

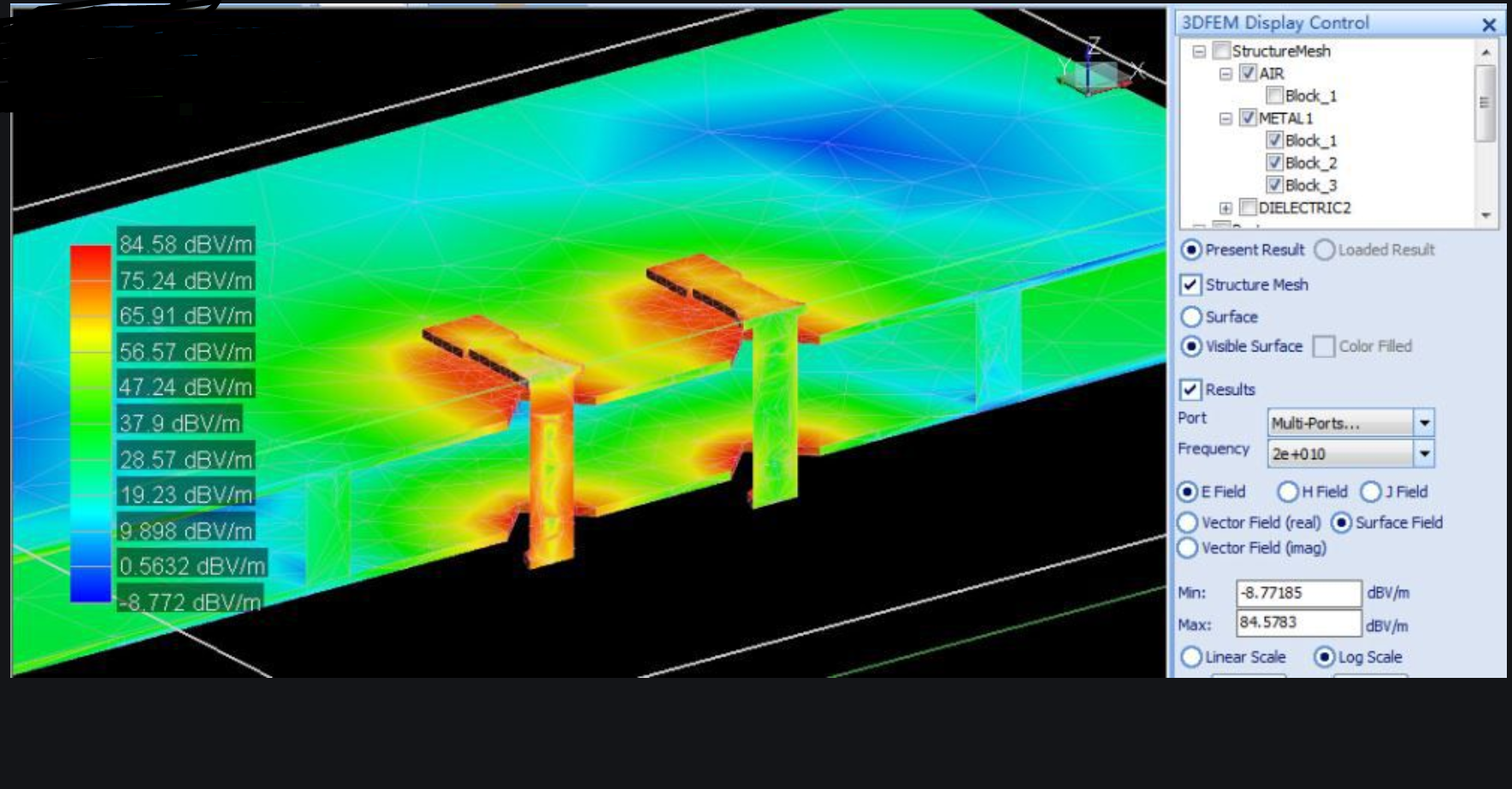

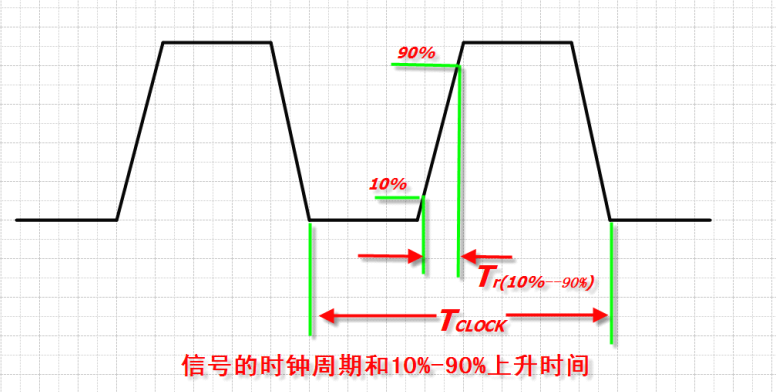

判断一个信号是否为高速信号首先要区分几个误区。误区一:信号周期频率FCLOCK高的才属于高速电路设计其实我们在电路设计时考虑的最高频率往往取决于信号的有效频率(亦称转折频率)Fknee。 如上图信号周期频率与有效(转折)频率定义为:(实际中多数信号)误区二:电容、电感式理想器件在低速领域,电容、电感工作频段比较低,可以认为他们是理想器件。但在高速领域,PCB上的电容电感等已经不能简单的视为纯粹的电容电感了。例如:在低速领域电容我们可以视为断路,而在高速电路中,假设工作频率为F,则电容C

答:我们PCB中的信号都是阻抗线,是有参考的平面层。但是由于PCB设计过程中,电源平面的分割或者是地平面的分割,会导致平面的不完整,这样,信号走线的时候,它的参考平面就会出现从一个电源面跨接到另一个电源面,这种现象我们就叫做信号跨分割。跨分割的现象如图1-52所示。跨分割,对于低速信号,可能没有什么关系,但是在高速数字信号系统中,高速信号是以参考平面作为返回路径,就是回流路径。当参考平面不完整的时候,会出现如下影响:Ø 会导致走线的的阻抗不连续;Ø 容易使信号之间发生串扰;Ø

答:高速信号、低速信号的区分取决于以下两个因素:信号的有效频率F;信号走线的有效长度U。一般来说,信号的有效频率F约等于信号频率的5倍,信号走线的有效长度等于U=(0.35/F)/D,其中D是PCB上的走线延迟,在FR4的材质中D约等于180,得出的结论就是在信号走线的长度小于有效长度的1/6,信号为低速信号;反之,信号为高速信号。所以我们判定信号是否为高速、低速信号的步骤如下:Ø 获取信号的有效频率与信号走线的长度;Ø 计算出信号走线的有效长度;Ø 比较信号长度与

在进行嵌入式开发中你一定遇到了各种总线,包括芯片内的地址总线和数据总线,高速总线和低速总线,还有芯片外的各种通信总线等等。而往往大家对总线似乎还是把握得不太好,所以今天挑选了一篇关于总线的文章供大家阅读。如果一座只能容一个人来往的独木桥,两

在之前分享的一篇文章:如何让自动驾驶汽车“认得路”中,主要聊了聊自动驾驶汽车中高精度地图的重要性,有一位朋友留言“如果作者了解申通快递分拣的那些自动移动小车的工作场景,恐怕就不会有这篇文章的观点看法了吧?”,在此对话中,涉及了低速自动驾驶与

扫码关注

扫码关注