- 全部

- 默认排序

在电源PCB设计中,很多电子工程师经常会看见电路板上有很多槽孔设计,这些槽孔并非随意布置,而是出于电气安全和性能优化的考量,但细究原因也没那么简单,下面将对电源PCB板的槽孔设计进行分析。1、爬电间距要需求爬电间距是指沿绝缘表面测得的两个导

在电源PCB设计中,很多电子工程师经常会看见电路板上有很多槽孔设计,这些槽孔并非随意布置,而是出于电气安全和性能优化的考量,但细究原因也没那么简单,下面将对电源PCB板的槽孔设计进行分析。1、爬电间距要需求爬电间距是指沿绝缘表面测得的两个导

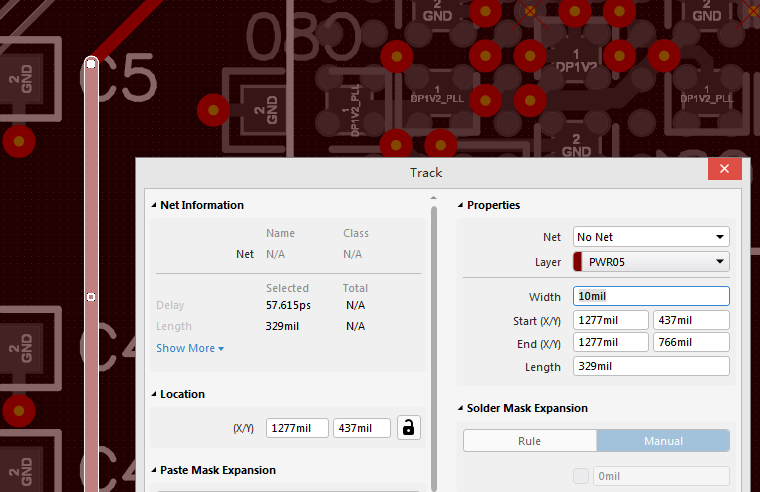

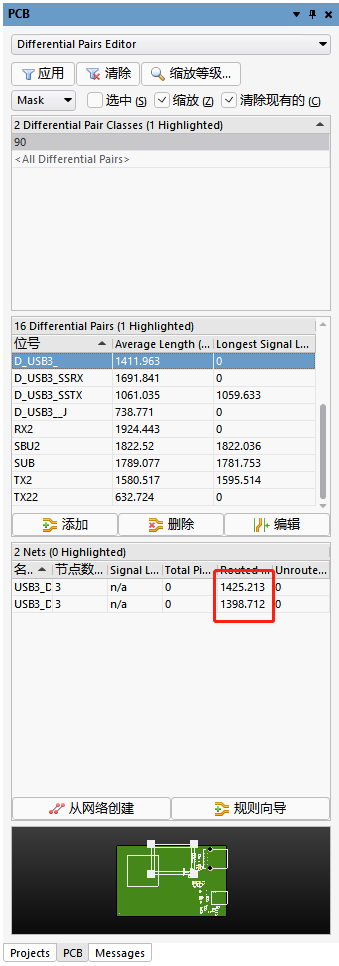

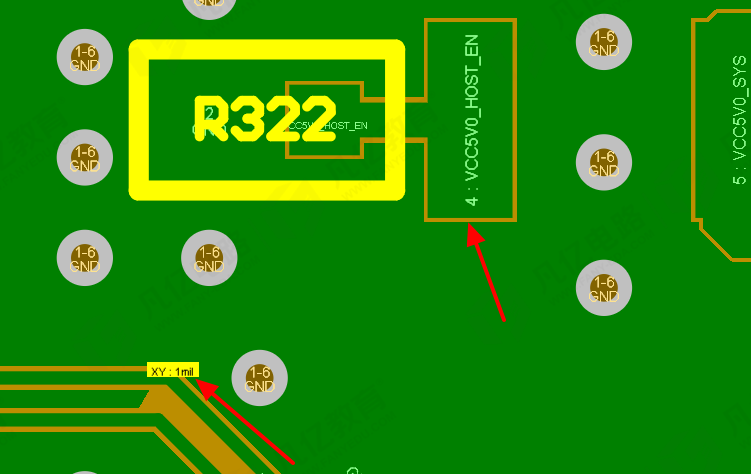

注意焊盘出线规范后期自己优化一下2.差分对内等长凸起高度不能超过线距的两倍3.注意差分走线要尽量耦合4.一层连接不用打孔,注意不要出现STUB线头5.CC1和CC2属于重要信号,走线需要加粗6.注意差分信号包地要在地线上打上地过孔7.过孔需

随着万物互联时代的发展,5G网络、AI大模型的崛起,信号频率日益增高,产品逐渐高密度化。面对高速高密度的PCB设计挑战,仿真工程师需要改变的不仅仅是工具,还有设计方法、理念及流程。光靠在大学期间所学到的仿真工具及电路原理,动手做过信号仿真项

建议平面层的分割带宽度至少20MIL:地址信号类的等长还存在个别信号的误差报错:误差报错的信号自己再去等长优化。建议地址跟数据线两个类之间的信号可以走一根GND信号线进行分割开:或者自己预留20MIL的宽度。整个电源平面的信号都是3.3V信

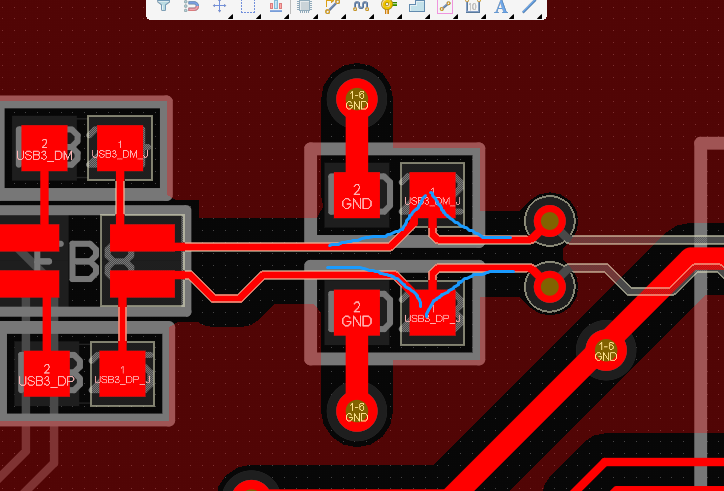

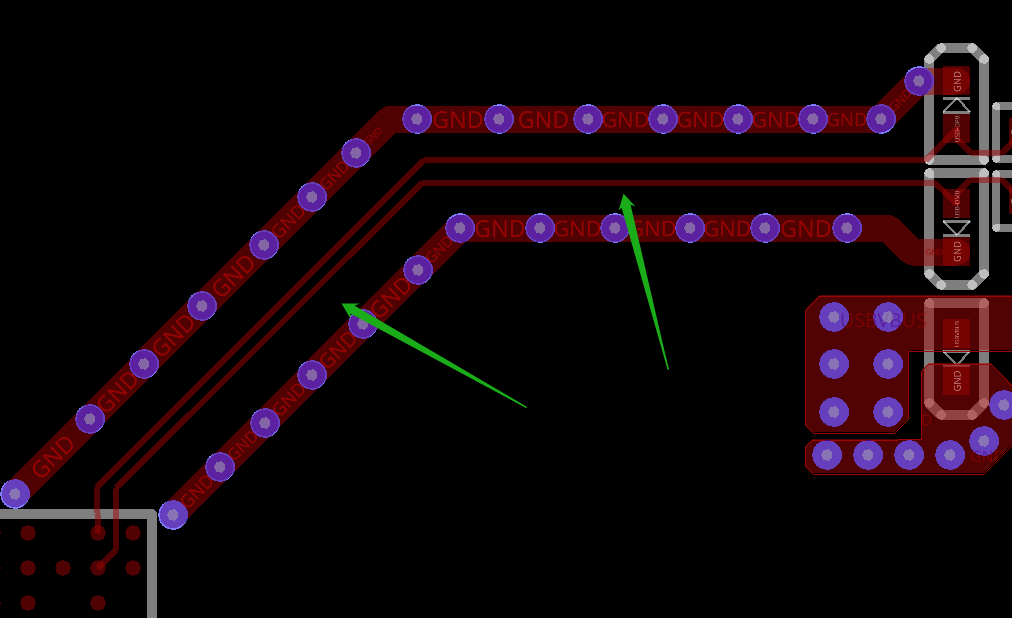

USB2.0:差分走线是需要保持耦合,需要修改,不合格:USB3.0:还有一块铜皮存在板外,自己删除下:此处器件注意整体中心对齐放置:差分信号打孔换层的过孔两侧打上地过孔:此处差分需要优化,要耦合走线 :注意此处焊盘出线,需要从两侧边拉线出

差分对内等长误差超过+-5mil这里走线要优化一下这个cc1线不要比焊盘宽可以拉出后在加粗以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.c

在PCBA焊接加工时,电子工程师可能会遇见PCB板上产生气泡问题,导致PCB板焊接不到位,最终影响其性能,因此如何避免产生气泡问题是个很重要的事情,下面将谈谈如何做?!1、优化焊接参数焊接温度、时间和冷却速度是影响气泡形成的关键因素。过高的

在电子制造行业,PCBA(印刷电路板组装)打样是一个关键而耗时的环节。对于工程师而言,减少打样时间不仅能提高工作效率,还能降低制造成本,加速产品上市。本文将探讨如何有效减少PCBA的打样时间。1、优化设计方案设计方案的合理性直接影响到打样时

铜皮间距太小,所有间距最小不能小于4mil多处孤岛铜皮、尖细铜皮差分出焊盘尽快耦合优化布局走线尽量靠近,不会可以查看参考板走线太细,走线一般情况最细4mil,明明可以走4mil线宽差分对内等长绕线在引起不等长处绕线差分对内等长绕线拱起处长度

扫码关注

扫码关注