- 全部

- 默认排序

SiC MOSFET沟槽结构将栅极埋入基体中形成垂直沟道,尽管其工艺复杂,单元一致性比平面结构差。但是,沟槽结构可以增加单元密度,没有JFET效应,寄生电容更小,开关速度快,开关损耗非常低;而且,通过选取合适沟道晶面以及优化设计的结构,可以实现最佳的沟道迁移率,明显降低导通电阻,因此,新一代SiC

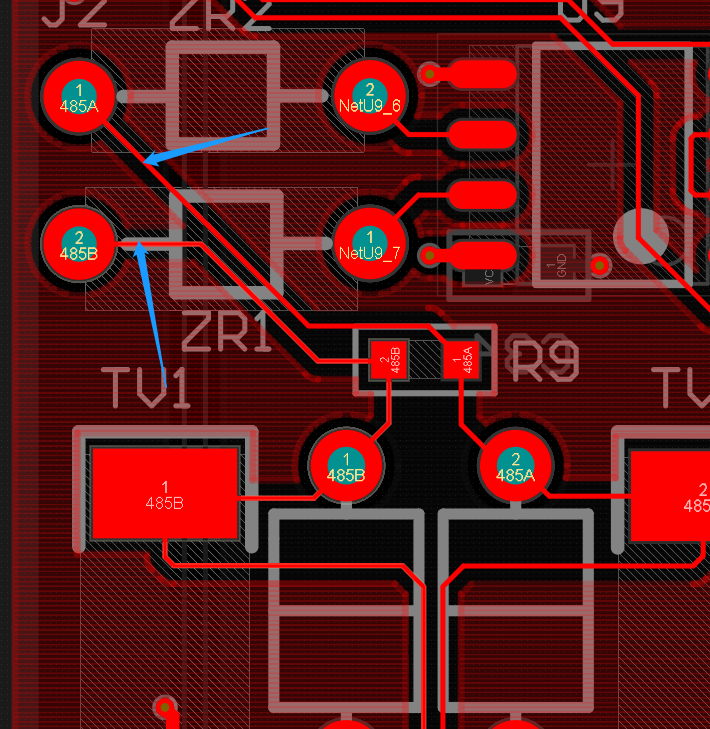

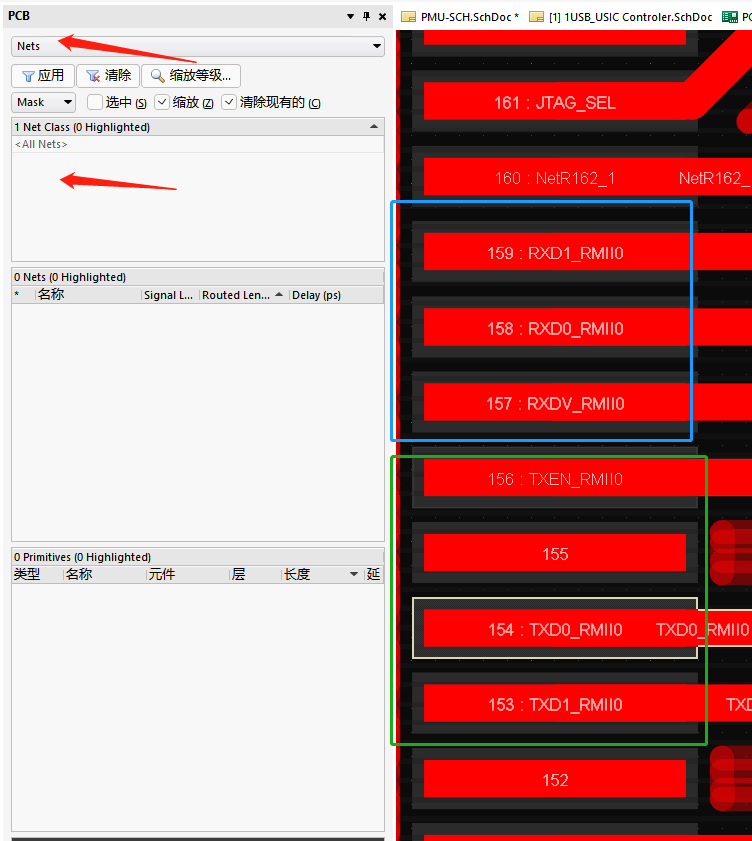

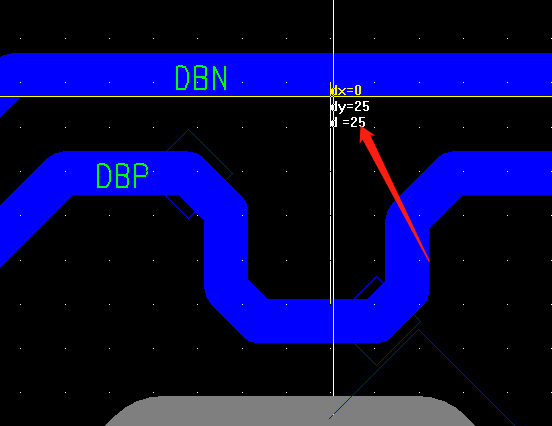

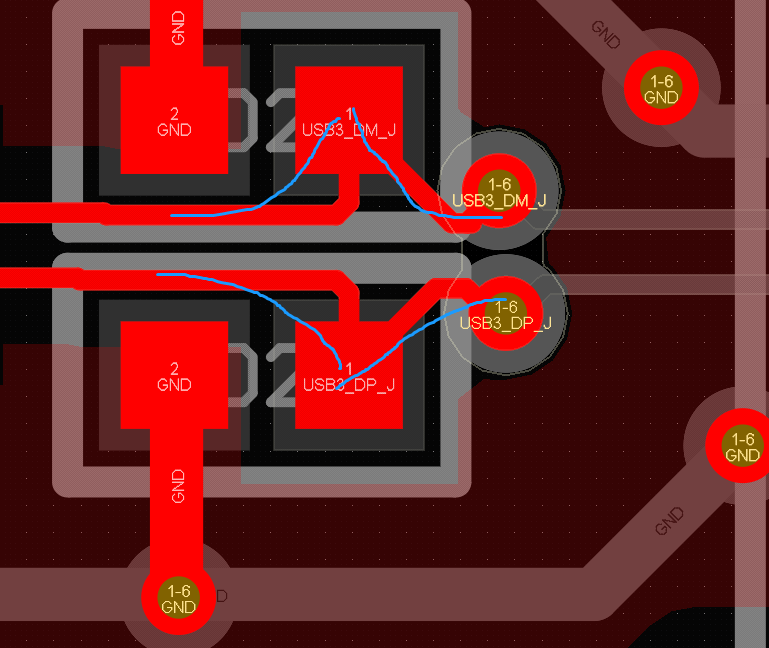

1.485需要走内差分,此处需要优化一下2.模拟信号需要单根包地,走线加粗,并且模拟信号下面不要有其他信号的走线3.差分对对内等长误差5mil4.百兆网口需要添加100oh的 class5.网口除差分信号外,其他信号都需要加粗到20mil6

当今,越来越多的电子产品急需高速和高性能的PCB板来满足需求,因此,如何提高PCB板的运行速度和性能已成为电子工程师的关注焦点,下面将聊聊一些技术方案,可以帮助工程师更好提升PCB板的性能和运行速度。1、优化布局PCB板的布局对其运行速度和

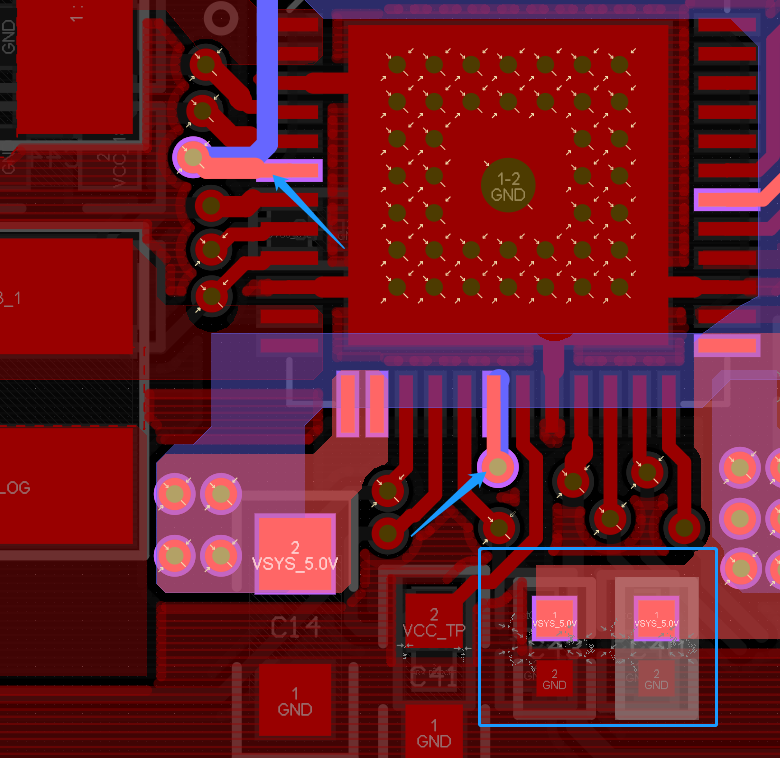

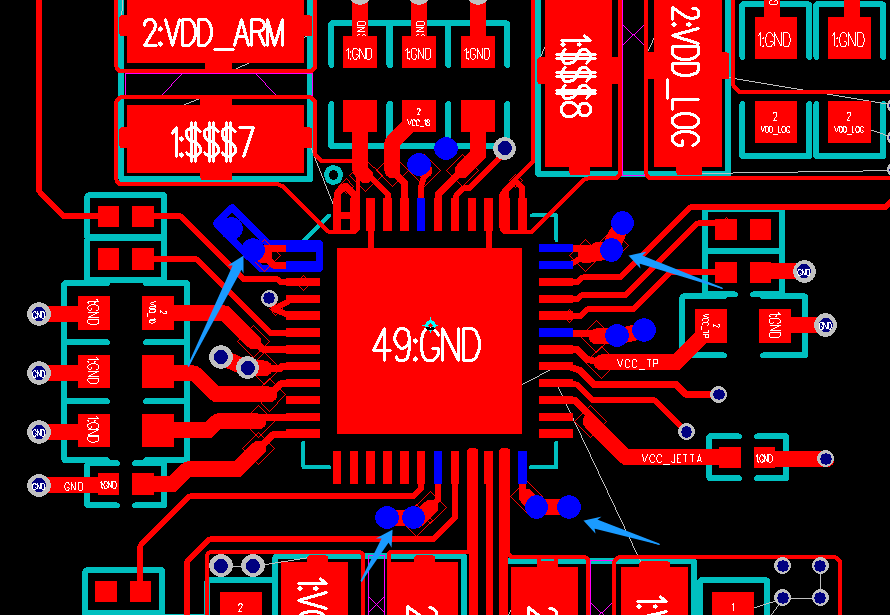

分割地尽量满足1mm,有器件的地方不满足可以忽略2.跨接器件旁边尽量多打地过孔3.差分线需要优化一下,尽量从焊盘拉出在走差分差分出线方式都需要再尽量优化一下4.晶振需要包地处理,晶振下面不要走线,不要放置器件5.焊盘出现不规范,焊盘中心出线

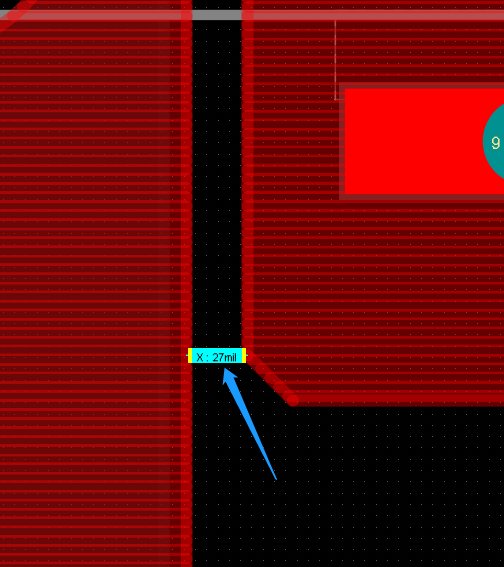

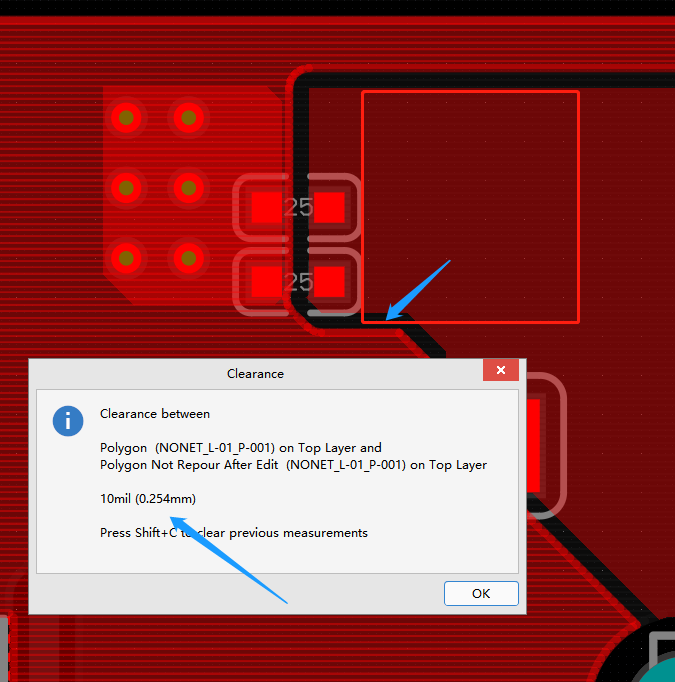

滤波电容放置尽量靠近管脚放置2.挖空后需要右键重新铺铜才有作用3.此处不满足载流4.电感下面尽量不要放置器件5.走线未连接到焊盘,存在开路6.铺铜尽量把焊盘包裹起来7.走线需要优化一下以上评审报告来源于凡亿教育90天高速PCB特训班作业评审

未创建TX和RX的class,分别等长误差100mil2.时钟信号要进行连通并包地处理3.焊盘出现需要优化一下4.变压器所有层需要挖空处理5.差分对内等长误差5mil6.差分出线要尽量耦合7.没有添加差分对的class8.pcb上存在多处开

跨接器件旁边尽量多打过孔,地分割间距尽量1mm,有器件的地方不满足可以忽略2.差分对内等长误差5mil3.差分走线需要优化一下4.晶振走内差分,需要包地处理5.走线没有连接到焊盘中心,存在开路6.未创建RX和TX class,误差范围100

DCDC 4路输入不满足载流,一般20mil过1A2.输出铺铜尽量大一点,地网络尅直接连接在散热焊盘上3.走线需要优化一下4.元件尽量优先顶层布局5.反馈器件尽量靠近管脚放置,走一根10mil的线即可6.反馈需要加粗到10mil7.此处电源

锯齿状等长不能超过线距的两倍2.差分出线需要优化一下3.滤波电容放置有问题,有网络没有导入成功4.这几个应该是一个网络,滤波电容靠近对应的管脚放置5.器件摆放不要挡住一脚标识6.TX和RX要添加等长组分别进行等长,误差100mil7.存在s

焊盘出现需要优化一下2.差分对内等长误差5mil3.其他没什么问题USB2.0注意差分走线要满足车分间距规则以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item

扫码关注

扫码关注