- 全部

- 默认排序

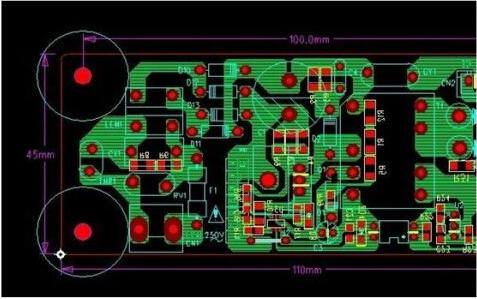

我们在平常的pcb设计中会遇到各种各样的安全间距的问题,比如像过孔跟焊盘的间距,走线跟走线之间的间距等等都是我们应该要考虑到的地方。那么我们今天就把这些间距要求分为两类,一类是:电气安全间距;另一类为:非电气安全间距。

Altium designer6层平板电脑RK3288PCB视频教程亮点(1)了解平板电脑的设计总体要求及设计框架(2)掌握电子设计的流程化设计(3)了解设计当中涉及到的基本概念(4)掌握pcb设计的布局布线规划(5)掌握软件模块化布局技巧(6)掌握各类接口器件和功能模块的布局布线菱(7)常见EMC/EMI的处理方式及注意事项

通过这一课程我能学到什么1)Allegro 4层板布局布线技巧2)Allegro 4层板TI主控设计3)Allegro软件基本操作技巧4)菊花链拓扑设计5)凡亿高手实战经验这个是一个非常经典的4层allegro达芬奇核心板设计,基于TI的主控DM642,全程讲解通过Allegro软件来设计一个4层的达芬奇开发板的pcb设计实战过程,从前期的原理图导入,导后期输出生产文件(GERBER )的全过程。

本套视频教程亮点(1)掌握pcb设计常用的设计技巧及熟悉pcb设计的整体流程(2)掌握Allegro软件的快捷键运用、提高pcb设计效率(3)掌握6层板设计过程中电源与地平面的处理方法(4)掌握6层板设计过程中BGA芯片的处理方法

纵观成功的电子产品,基本都要具备五个特点:一 性能稳定; 二 整体美观; 三 便于应用; 四 成本合理 ; 五 方便量产; 偏重哪一点,都不能称之为成功的产品。这五点都与pcb布局有关,换句话说,好的,合理的布局是要充分考虑以上五点的,,所以说布局是产品成功与否非常重要的一环。高速pcb设计中,布局更是重要,其合理性直接关系到后续的布线,信号传输的质量,EMI, EMC,ESD等问题,

硬件高手的网表妙招

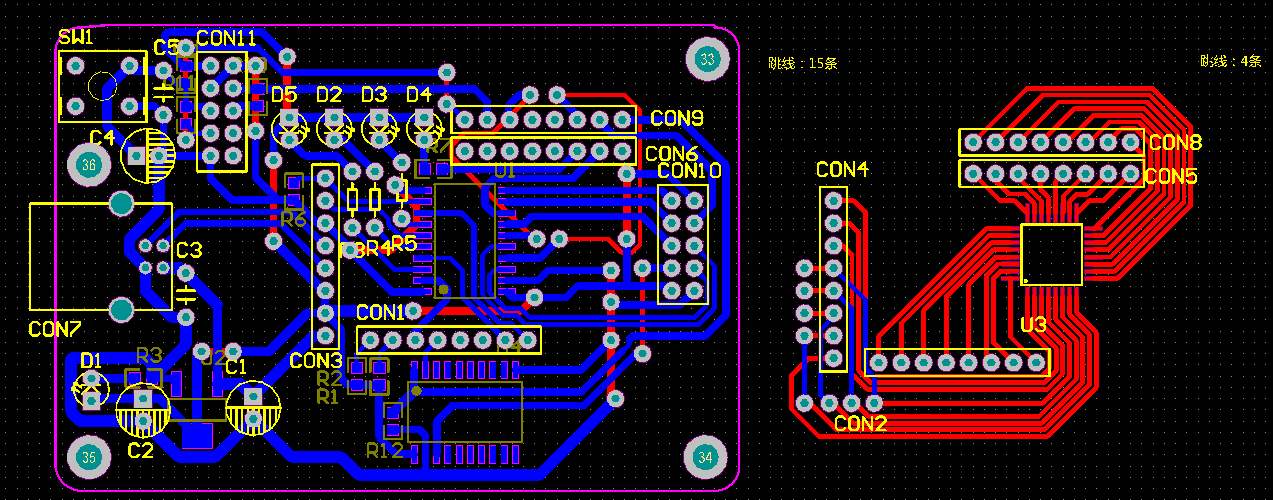

网表也称网络表,顾名思义,就是网络连接和联系的表示,其内容主要是电路图中各个元件类型、封装信息、连接流水序号等数据信息。在使用Altium Designer进行pcb设计时,可以通过导入网络连接关系进行PCB的导入。当今几大主流pcb设计软件都支持Altium Designer格式网表导出,这也极大地提高了Altium Designer对其他类设计软件的兼容性,如图8-10所示。

我们在进行pcb设计之前需要在原理图中去绘制原理图,那么绘制原理图我们又需要去创建元件库,这个时候就有很多学员会问到这个问题了。就是在我们的元件库或者原理图中,管脚字体的大小该如何更改,以及字体的类型该如何进行更改?这个就是我们今天需要去解决的问题。

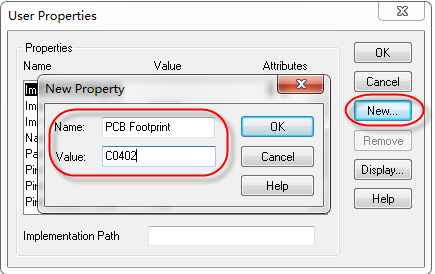

pcb设计:怎么显示与隐藏原理图库的PCB封装名称? 答:这里我们分为两种情况进行分析,一种是在绘制原理图库的时候,怎么显示与隐藏元器件封装名称;另外一种是在绘制原理图的时候,怎么显示与隐藏元器件封装名称。 ① 绘制原理图库时隐藏PCB封装的操作步骤如下; 第一步,打开所要隐藏PCB封装名的库文件,点击菜单Options→Part Properties编辑属性;

pcb设计:检查线间距时差分间距报错的处理方法 为了尽量减小单板设计的串扰问题,pcb设计完成之后一般要对线间距3W规则进行一次规则检查。一般的处理方法是直接设置线与线的间距规则,但是这种方法的一个弊端是差分线间距(间距设置大小不满足3W规则的设置)也会DRC报错,产生很多DRC报告,难以分辨,如图12-23所示。

一、PADS8层DDR3 Fly-by拓扑结构视频课程详情本pads视频课程基于飞思卡尔 i.MX6 处理器的 8层pcb设计,重点介绍 DDR3 内存的设计思路,一共四颗 DDR3,采用菊花链(Fly-By)的拓扑结构。讲解了 DDR3 设计的信号 class分组,信号的同组同层布线、信号时序等长及常用规则注意事项、信号完整性、电源完整性的规划等。

扫码关注

扫码关注