- 全部

- 默认排序

一、课程详情本次4 层 PADS DSP 芯片主控设计课程是一个难度适中的基于 DSP 芯片为主芯片的 4 层高速 pcb 设计项目,项目中涉及了 DSP、FPGA 芯片,使用了 SDRAM、FLASH、SRAM 等高速存储器模块。

一、课程详情这个是一个Cadence Allegro非常经典的 6 层一阶盲打孔设计,基于三星系列 S3C6410 ,全程讲解了通过Cadence Allegro,运用-阶盲埋孔的技术进行工控核心板卡的 pcb 设计教程视频,从前期的原理图导入,到后期输出生产文件( GERBER)的全过程。

EDA软件中Altium Designer的兼容性是最好的,在其他EDA平台设计的原理图、pcb等文件,有时候会统一到Altium Designer平台,或者将在Altium Designer平台设计的文件导入其他平台,这种时候需要用到导入导出的功能。

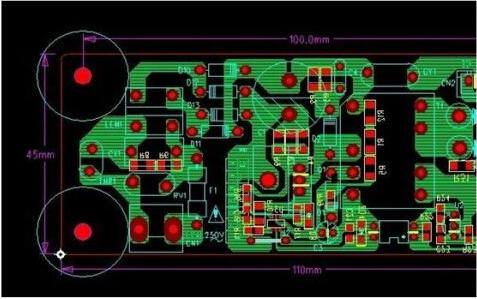

一、4层 PADS 路由器产品设计视频教程课程目录 01、视频内容介绍及设计资料准备 02、原理图分析及电源二叉树分析 03、原理图导入 pcb 04、pcb 板框导入及布局布线区域设置 05、pcb 设计默认设置及颜色方案设置

一、PADS8层DDR3 Fly-by拓扑结构视频课程详情本pads视频课程基于飞思卡尔 i.MX6 处理器的 8层pcb设计,重点介绍 DDR3 内存的设计思路,一共四颗 DDR3,采用菊花链(Fly-By)的拓扑结构。讲解了 DDR3 设计的信号 class分组,信号的同组同层布线、信号时序等长及常用规则注意事项、信号完整性、电源完整性的规划等。

在进行pcb布线之前,都需要先做扇出工作,方便内层布线。对于电阻电容后者是小的IC类器件,可以直接进行手动扇出,但是对BGA类的器件,管脚数目太多,如图5-122所示,这样手工去扇出的话,工作量太大,而却BGA区间必须要扇孔在焊盘的中心位置,所以手动扇出是不现实的,这里我们讲解下,如何对BGA器件进行自动扇出,提高设计的效率,具体操作如下所示:

究竟什么是产业互联网?为什么要发展产业互联网?这玩意和物联网有什么关系和区别?和嵌入式开发有什么关联?我需要关注吗?带着疑问阅读本文给你答案。

我们在用allegro进行pcb设计完成以后,都需要对一组传输的总线进行时序等长,在做时序等长的时候,分为绝对传输延迟与相对传输延迟。绝对传输延迟,顾名思义,信号传输在pcb设计中都是有一个走线的长度,我们通过设置这个信号线传输的最大值与最小值,来实现等长的方法,就称之为绝对传输延迟。

因为做教育的缘故,经常和大学生打交道。谈起自己的大学课堂教育大多觉得遗憾,很多人表示确实自己也没好好学,怪自己。然而同时也有老师的责任,因为确实无趣且难懂。很多人感慨,为什么大学课堂教学不能像网上的视频课程那样有趣且好懂且能学到东西呢?

扫码关注

扫码关注