- 全部

- 默认排序

一个layout工程师学习信号完整性之路刚开始听说和接触眼图时,是从DDR的仿真眼图开始的,看到别人的仿真结果,很是羡慕。然后自己开始仿真研究,设计PCB单板,提取S参数,使用ADS、SPEED2000、Ansys搭建电路,设置参数,调试仿

一个layout工程师学习信号完整性之路上一篇文章简单说了一下对眼图的理解,关于眼图细分的其实有好多的知识点,但是有些不是常用的,在我们进行信号完整性的仿真时,一般都会有个眼图的mask,我们会用其来判断眼图是否满足结果,从而来优化layo

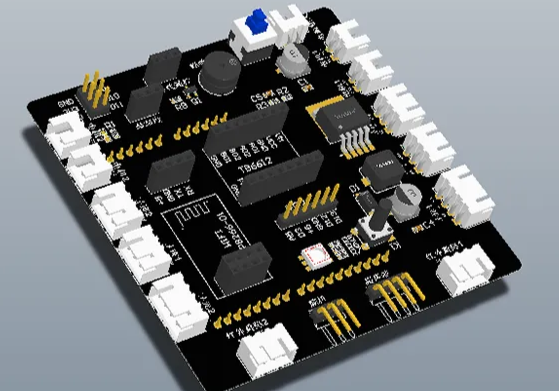

一个学习信号完整性的layout工程师今天整理下PCB封装的3D 模型添加,此步骤并不是所有的公司使用,因为我们平常给器件添加一个实际的高度,就已经OK了。只不过我们在看整版的3D模型是,每个器件都是方方正正的,不太美观。所以有的人要求完成

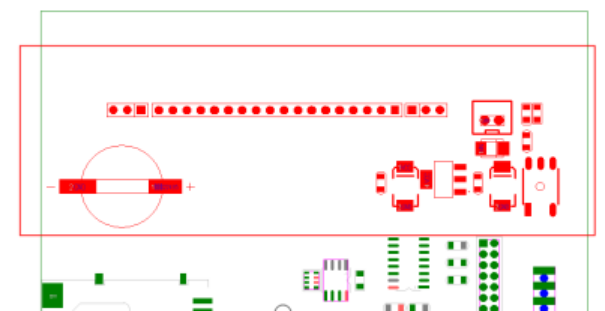

一个学习信号完整性的layout工程师在刚开始接触PCB设计时,使用的是Allegro软件。在进行第一个板子设计时就遇到了这个布局的问题。导入网表之后,发现有好多的模块是相同的。因为刚开始不知道Allegro有模块复用的功能,所以就一点一点

一个学习信号完整性的layout工程师Cadence Allegro是一款功能比较强大的软件,相比较其他的PCB设计软件来说,界面交互比较友好。其中的快捷键设置就是比较强大,我见过朋友完全使用快捷键进行画图的。但是个人感觉对于新手,还是新熟

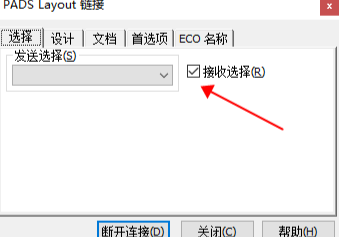

布局时一般需要与原理图同步,进行协作处理,提高布局效率。可同时打开Logic格式原理图与layout格式PCB文件,在Logic内执行“工具-Pads layout”命令,然后设置“选择”界面,与原理图同步的PCB须检查,以防文件不对应,一

一个学习信号完整性仿真的layout工程师上一篇和大家分享到铜箔的类型,压延铜和电解铜。本人讲述的仅仅是在PCB设计的领域。其实铜箔是在我们的生活方方面面都用到的。还有一个问题就是PCB的生产正负片的问题,这和铜箔的类型应该是两个概念的。今

一个学习信号完整性仿真的layout工程师作为layout工程师,首先的输入条件就是原理图,也就是常说的(原理图导出网表文件)网表文件,有硬件工程师会直接把网表发给我们,有的直接给我们dsn文件,要求我们自己导出导入网表,下面简单介绍导出导

一个学习信号完整性仿真的layout工程师一个layout工程可能不仅仅是画板子连线,要了解硬件原理知识、PCB板厂知识,还有就是器件焊接问题,可能这其中的每一点拉出来就是一个单独的领域。因为我们做的是交付任务,所以各个领域都要确认OK,才

PCB设计的项目之间或同一项目中会存在拓扑跟封装完全相同的电路,做完一个模块,其他相同的模块可复制;或者在一个项目中需要多人协作,可以将PCB分成若干个功能模块,分给多个设计师去进行功能模块的布局工作,然后利用PADS layout的Mak

扫码关注

扫码关注