- 全部

- 默认排序

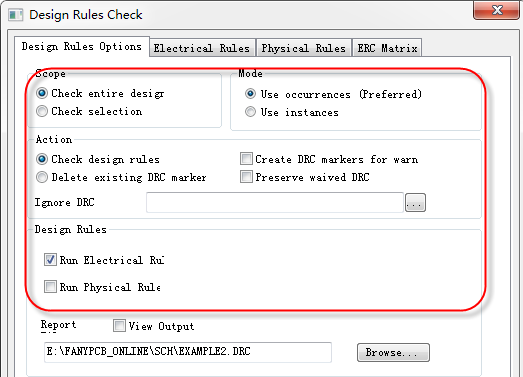

答:orcad进行DRC检测时,如图3-63所示,需要对参数进行设置,每个参数的含义如下所示: 图3-63 DRC参数上设置示意图Check entire design:DRC检查整个原理图;Check Selection:DRC检查选择的部分电路;Use occurrences:选择所有事件进行检查;Use instances(preferred):使用当前实体(建议)。所谓实体是指放在绘图页内的元件符号,而事件指的是在绘图页内同一实体出现多次的实体电路。例如,在复杂层次

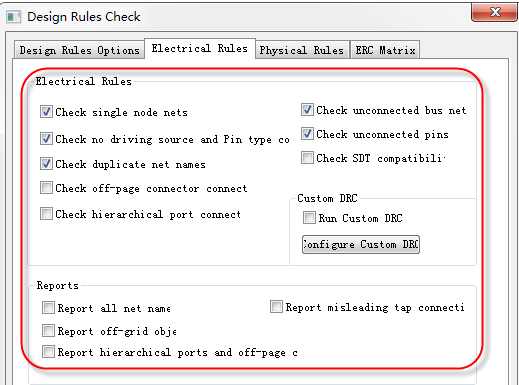

答:orcad进行电气DRC检测时,如图3-64所示,需要对检查的每一项参数进行设置,每个参数的含义如下所示: 图3-64 电气规则检查参数设置示意图Check single node nets:检查设计中的单端网络;Check no driving source and pin type…:检查器件属性无源管脚与有源管脚的连接是否正确;Check duplicate net name :检查重复的网络名称;Check off-page connector connect:检测分页图纸

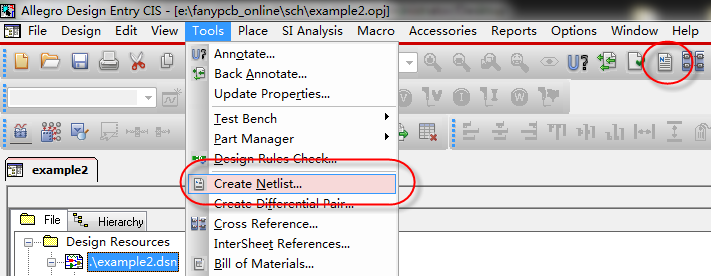

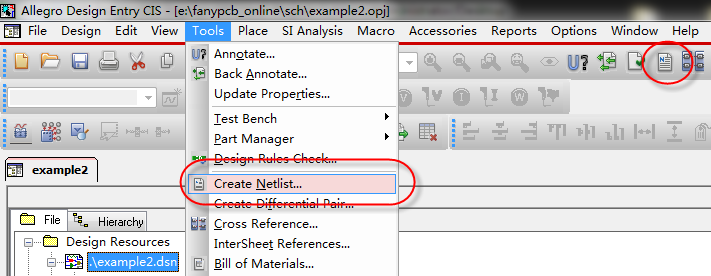

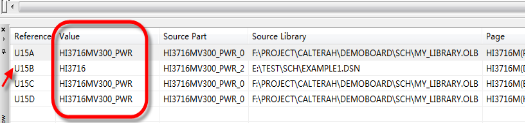

答:orcad产生Cadence Allegro的网表的操作步骤如下;第一步,选择原理图根目录,执行菜单Tools→Creat Netlist,或者是点击菜单栏上的图标,调出产生网表的界面,如图3-68所示; 图3-68 产生网表示意图第二步,弹出的Creat Netlist界面中,选择的是PCB Editor,产生Allegro的第一方网表,如图3-69所示; 图3-69 Allegro第一方网表参数设置示意图第三步,输入Allegro第一方网表需要注意下面几个

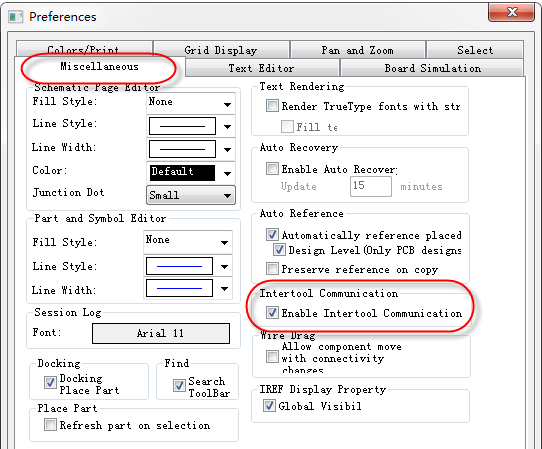

答:orcad与Cadence Allegro的交互式操作需要满足以下两个要求才可以实现:Orcad输出的是Allegro的第一方的网表,Allegro导入的是第一方网表,输出的具体方法见第3.35问;Orcad软件需要勾选以下选项,才可以实现交互式的操作,执行Options→Preference选项,选择Miscellaneous选项,如图3-71所示,在Intertoos Communication选项中,勾上下面的选项,才可以进行交互式操作; 图3-71 交互式操作示

答:orcad产生Cadence Allegro的网表的操作步骤如下;第一步,选择原理图根目录,执行菜单Tools→Creat Netlist,或者是点击菜单栏上的图标,调出产生网表的界面,如图3-74所示; 图3-74 输出网表示意图第二步,弹出的输出网表界面中选择Other选项,来输出第三方网表,如图3-75所示,在Formatters栏中选择orTelesis.dll选项,上面的Part Value栏需要用PCB Footprint来代替,不然会产生错误;

答:Allegro的第一方网表与第三方网表有以下几个区别点;与Allegro实现交互式操作的是第一方网表,第三方网表时不可以实现交互式操作;第三方网表不能将器件的Value属性导入到PCB中,输出时以封装属性来代替Value属性,第一方网表是可以的;网表导入到PCB中时,第三方的网表需要指定事先指定好PCB封装库文件,并产生device文件,才可以将网表导入到PCB中,第一方网表则可以直接导入。

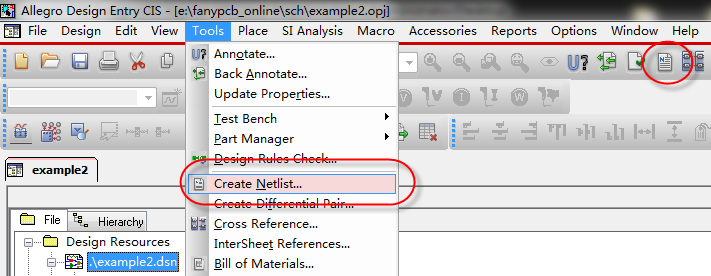

答:在使用Orcad软件输出Allegro第一方网表,出现如下错误:#6 ERROR(ORCAP-36003): Conflicting values of following Component definition properties found on different sections of U15. VALUE解决的办法如下所示:第一步,错误提示的含义是指U15这个器件分为了不同的PART,系统在进行识别的时候,属

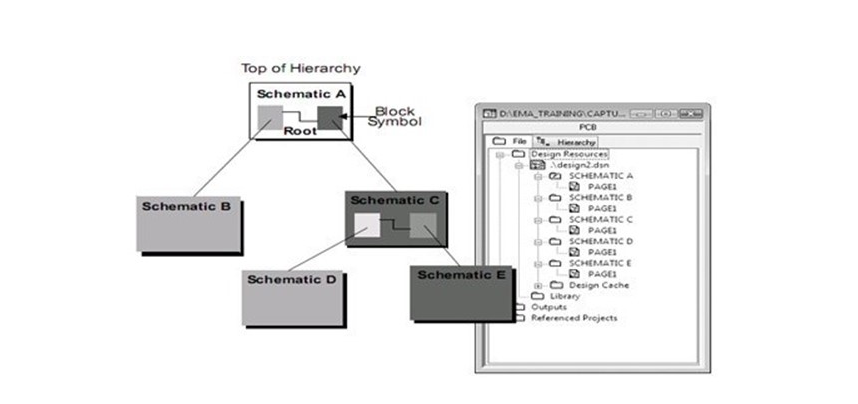

答:层次式电路设计(Hierarchical design),通常是在设计比较复杂的电路和系统时采用的一种自上而下的电路设计方法,即首先在一张图纸上设计电路总体框图,然后再在另外层次图纸上设计每个框图代表的子电路结构,下一层次中还可以包括框图,按层次关系将子电路框图逐级细分,直到最低层次上为具体电路图,不再包括子电路框图,如图3-107所示,是一个大概的层次式原理图的框架。 图3-107 层次式原理图示意图层次式原理图一种先进的原理图设计方法,使用符号代表功能,并且能够重复

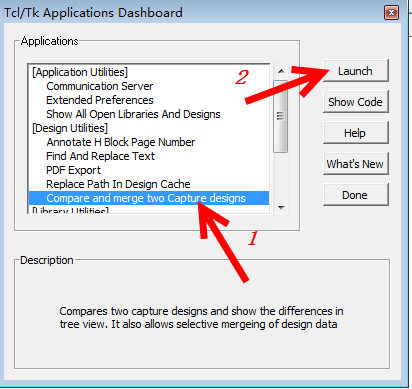

答:在电子设计中, 电路图的修改是非常频繁的,改动的多了,有时候会出现要改回去的情况,所以有时就会需要对两份原理图进行差分化的对比,操作步骤如下:第一步,首先,我们对一份原理图进行修改,修改一点点内容,做为测试之用,如图3-123与图3-124所示,方便后期查找; 图3-123 修改后的原理图示意 图3-124 修改前的原理图示意第二步,我们打开其中的任意一份原理图,选中原理图的根目录,然后执行菜单命令Accessories-Cadence TcL/Tk Utilities命

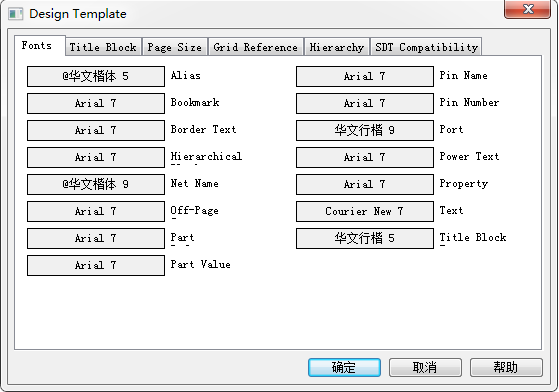

答:我们在运用Orcad进行原理图绘制时候,一般使用的都是默认的字体,用的最多的是就是网络标号的字体、位号的字体、封装属性的字体。当然使用默认字体是没有任何问题的,只是有时候我们将一些属性加以批示与标注,更加醒目这时就需要对其进行更改,一个一个去改费时费力,这里我们讲解下如何批量的去进行更改,具体操作的方法如下:第一步,首先打开原理图,对设计的模板进行更改,这样模板设定好了以后,原理图设计的内容都会根据模板来进行设定,执行菜单命令Options-design Template,会弹出如图3-13

扫码关注

扫码关注