- 全部

- 默认排序

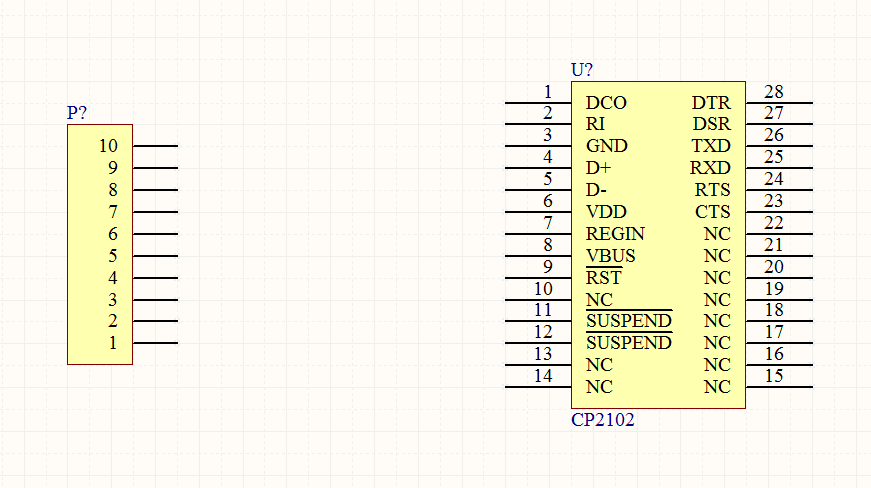

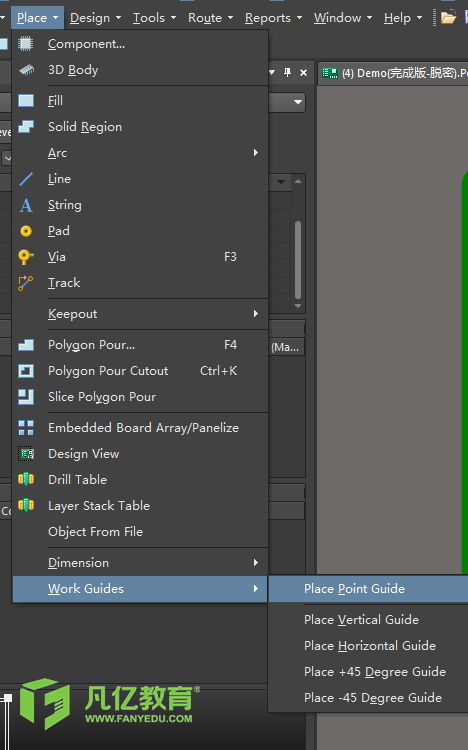

在PCB设计中,绘制原理图时避免不了要用到总线,但是在我们使用Altium designer绘制总线时总是出现一些问题,导致总线无法使用。

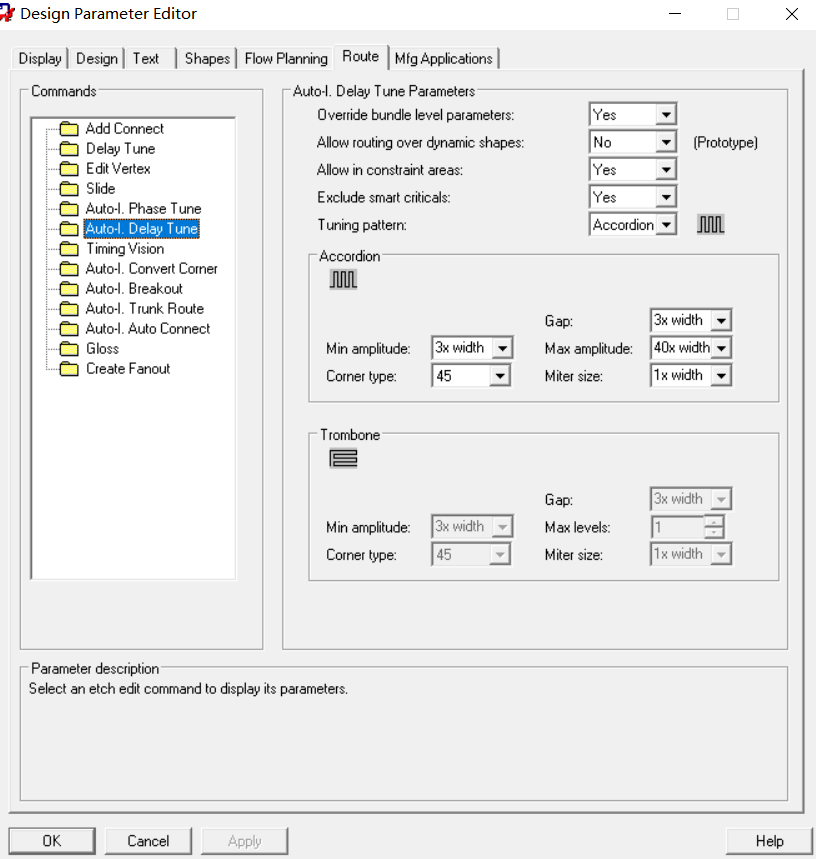

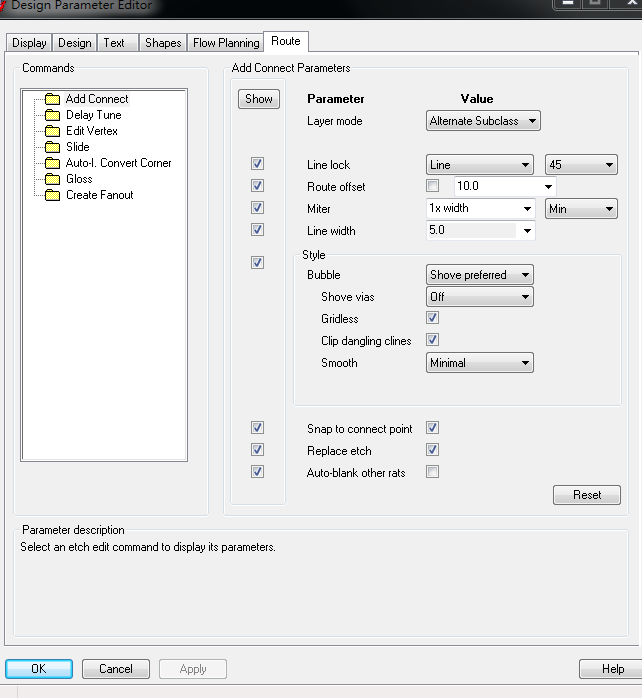

对于一些并行传输的数据而言,需要做到信号同步,以满足时序关系,如果信号的延时相差太大,可能会导致数据无法正确识别,此时就需要进行等长绕线处理。在布线空间较为充足的情况下,自动等长绕线工具能实现自动绕线(delay tune)。但在绕线前,必须把各种规则设置好,建议添加以下规则。

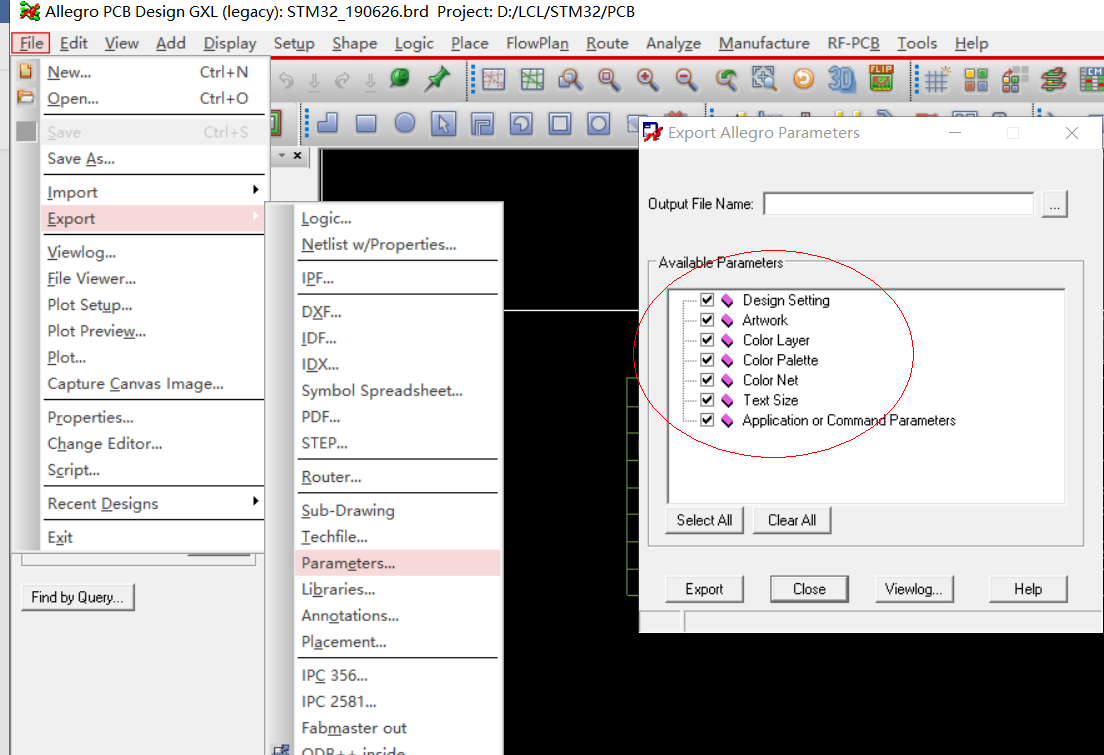

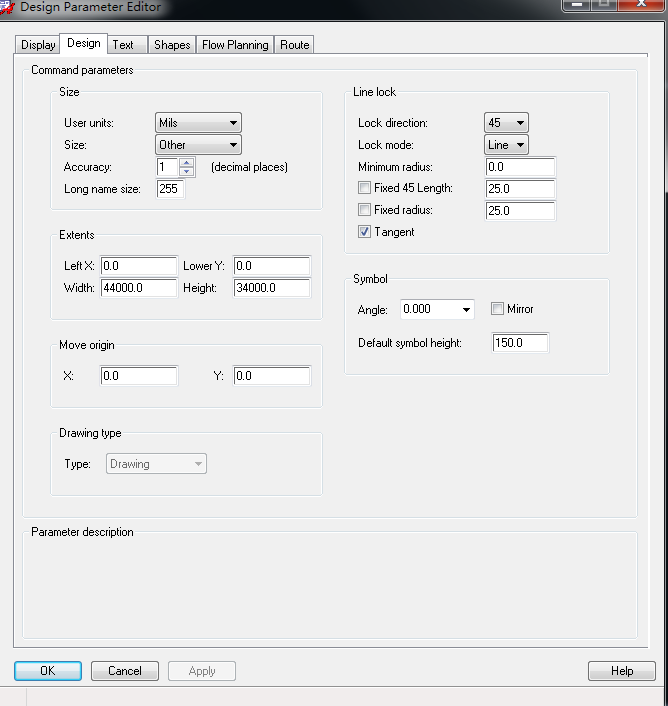

每个使用者可能都有自己的软件使用习惯,等使用者需要将已有的PCB文件中诸如显示效果、格点、Gerber设置、字号设置等参数导入到另一个PCB文件时,cadence提供了此类参数的导入/导出功能,方便使用者进行参数复用。

物理约束规则介绍

物理规则包括设置线宽和指定过孔库等的属性规则,在设置规则之前,需要把层叠等参数设置好。默认的为default规则。default规则是指铺铜的单线50Ω阻抗的信号线规则

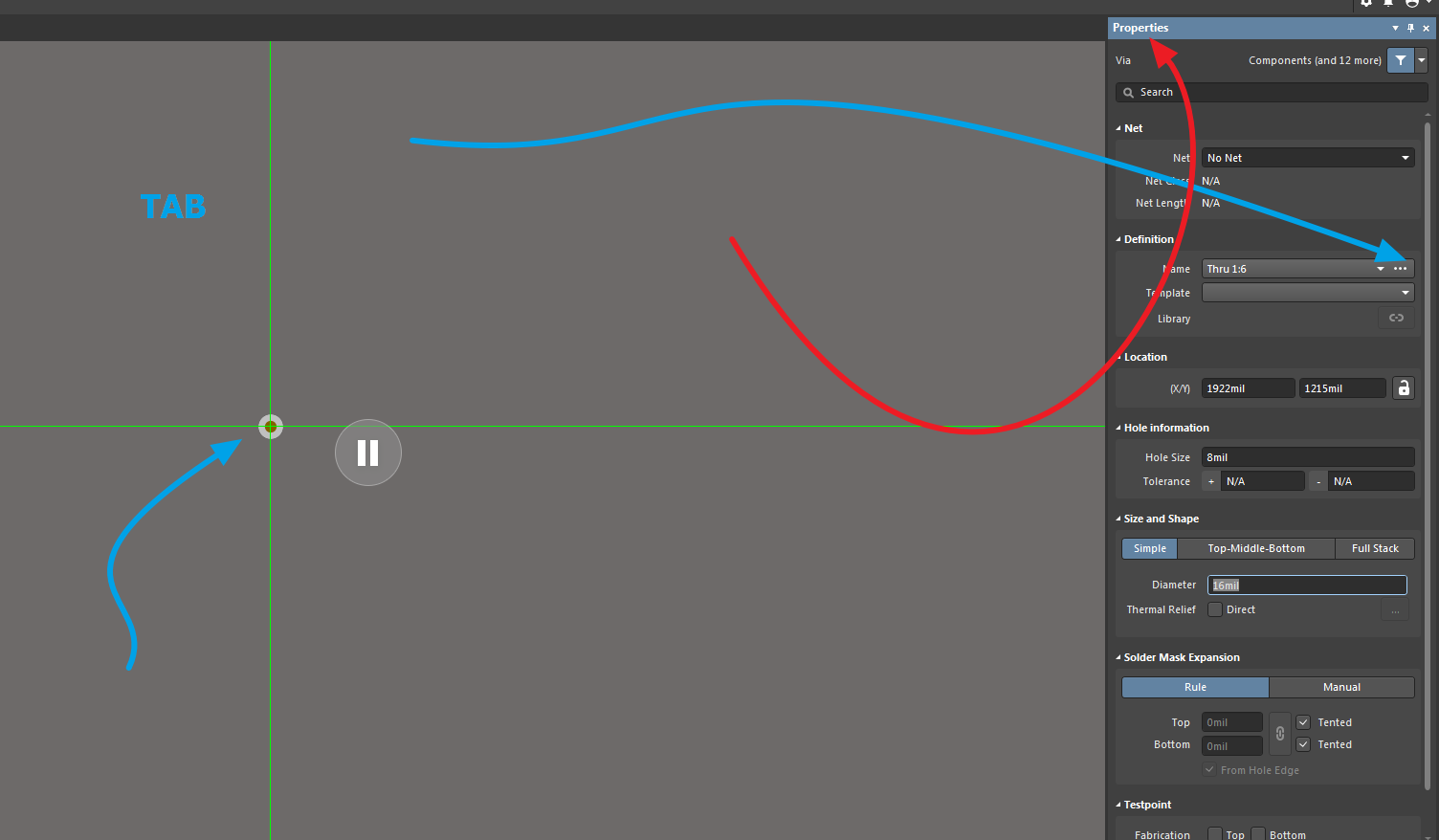

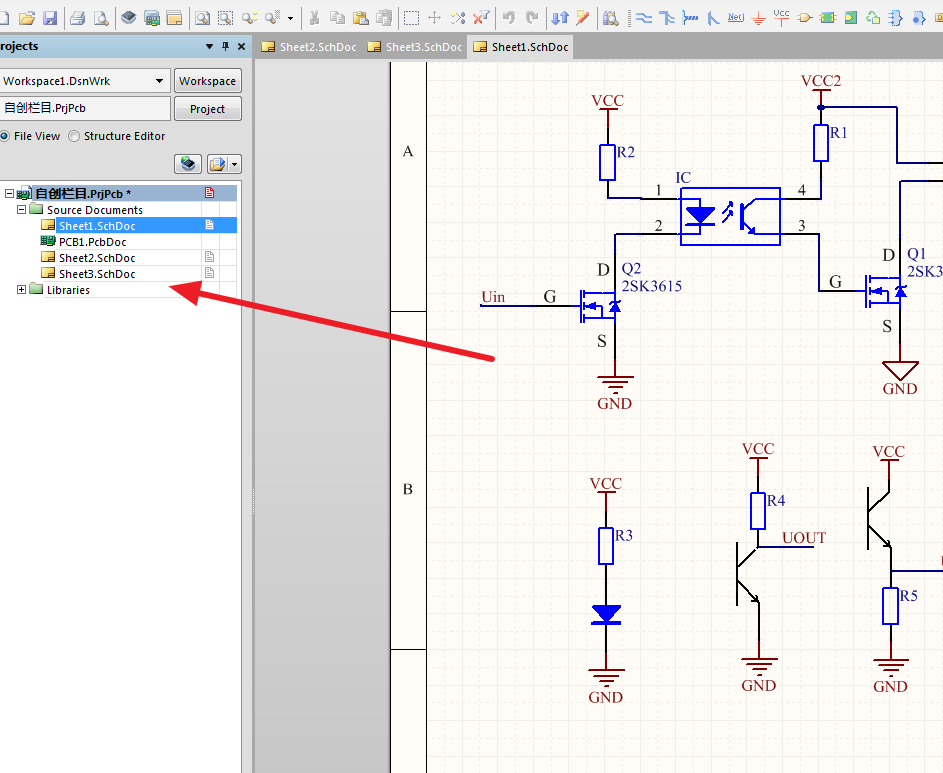

在AD的原理图绘制的时候我们想要只导入部分的原理图或者只导入单独一页的原理图如何进行操作。 这里目前有两种方式,第一种方式是直接放置屏蔽编译框,第二种就是进行网络比对的导入,就是我们使用导入网表比对的方法进行屏蔽部分原理图文件或者某些原理图。

扫码关注

扫码关注