- 全部

- 默认排序

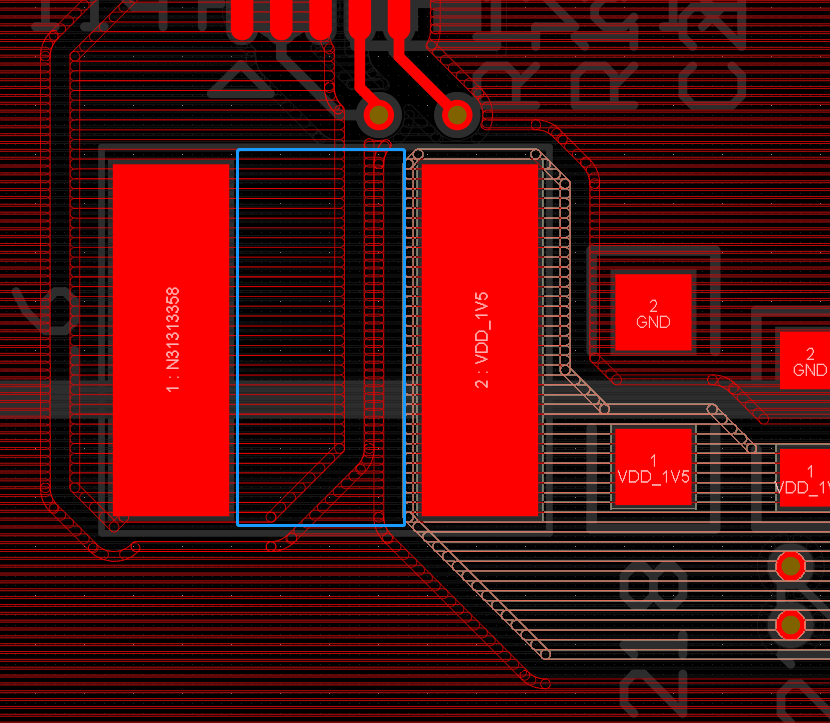

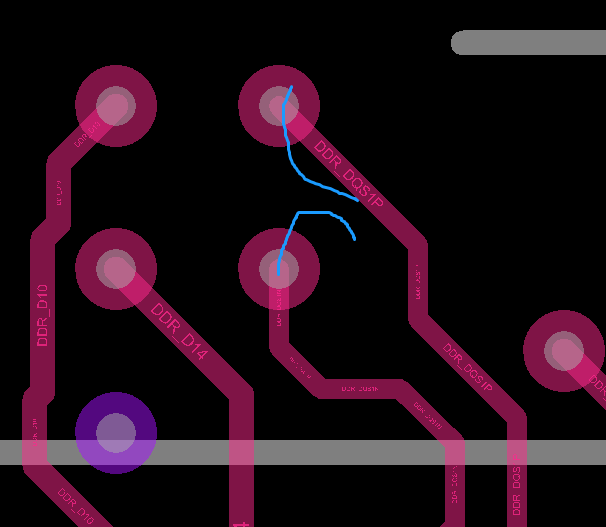

存在多出开路2.走线需要优化一下,尽量钝角3.此处铜皮出现载流瓶颈,后期自己把铜皮加宽一些4.存在多余的走线5.和孔需要优化一下,可以直接打孔,T点的臂可以不用满足3W6.注意过孔不要上焊盘以上评审报告来源于凡亿教育90天高速PCB特训班作

一、产品问题描述某车载产品进行EMC测试,发现1.6GHZ处超标,不能满足标准要求。① 远场测试图 图 1 远场测试图② 测试结果注:由上图测试结果可见,受测样机辐射发射骚扰测试在1600MHz频点存在超标情况,超标数值为5.34DB。二、定位与初步分析经与客户沟通得知样机内ddr通讯的时钟信

1SDRAM注意数据线等长存在报错2ddr注意差分出线呀尽量耦合2.差分线对内等长处理不当,锯齿状等长不能超过线距的两倍3.差分要设置对内等长误差5mil4.滤波电容尽量保证一个管脚一个,靠近管脚摆放5.注意电源管脚扇孔走线需要加粗以上评审

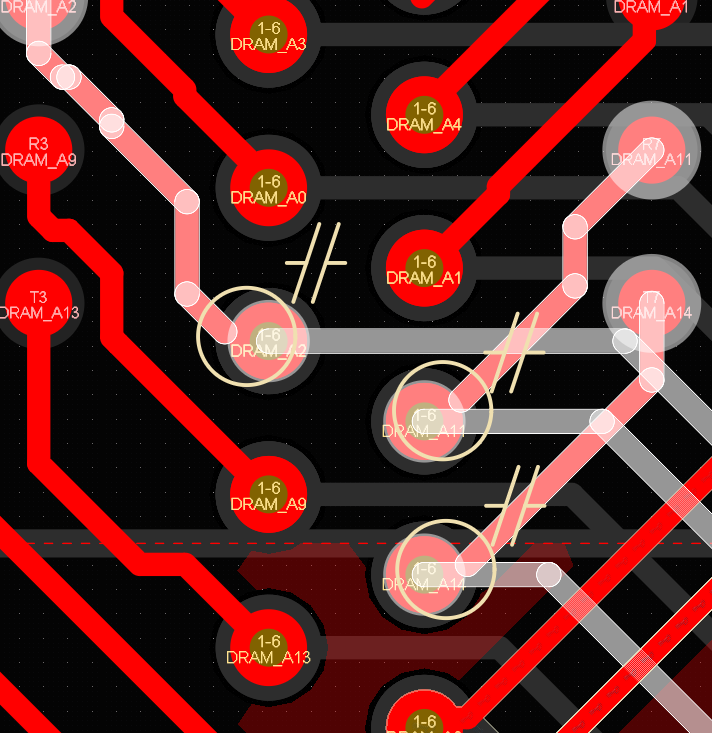

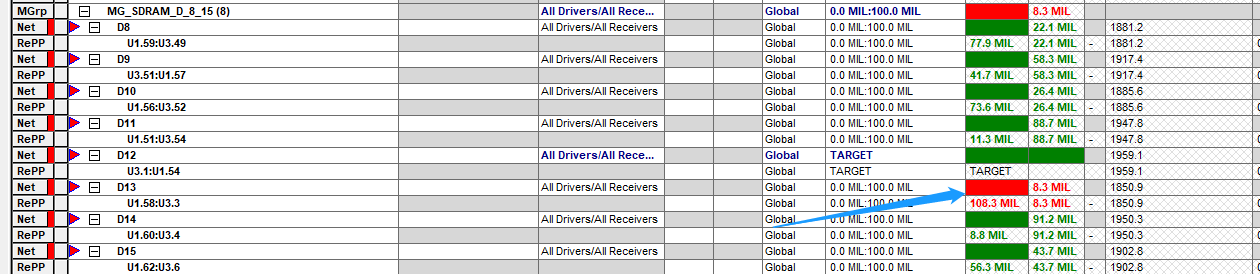

电感所在层的内部需要挖空处理2.反馈线走一根10mil的线即可,不用进行铺铜3.存在开路4.地址线等长存在报错5.注意电源线宽尽量保持一下,满足载流,走线最少需要加粗到15mil以上6.地网络需要就近打孔以上评审报告来源于凡亿教育90天高速

注意低脂线等长需要满足3W2.数据线之间等长也需要满足3W3.电感所在层的内部需要挖空4.VREF的电源走线需要加粗到15mil以上5.电容摆放尽量保证一个管脚一个,靠近管脚放置6.除了散热过孔,其他的都可以盖油处理以上评审报告来源于凡亿教

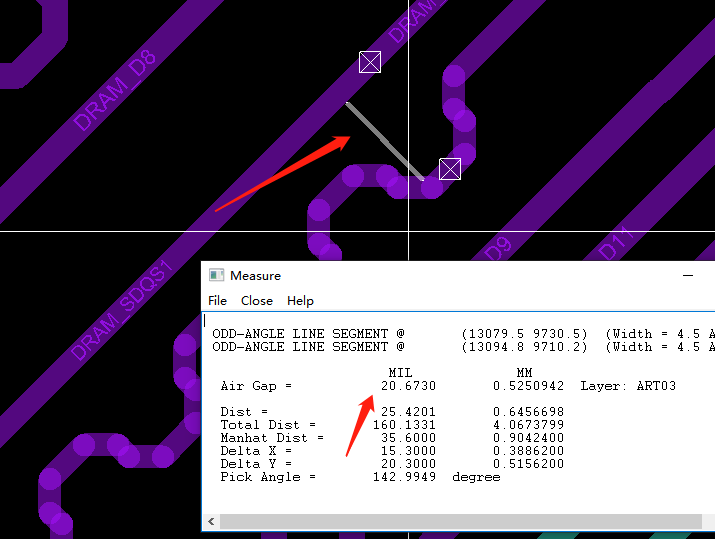

差分线锯齿状等长不能超过线距的两倍很多差分都存在同样的问题,后期自己修改一下2.注意差分走线要尽量耦合3.一对差分只用进行对内等长,不用两根都进行绕蛇形4.滤波电容尽量靠近管脚摆放,走线加粗,需要优化一下以上评审报告来源于凡亿教育90天高速

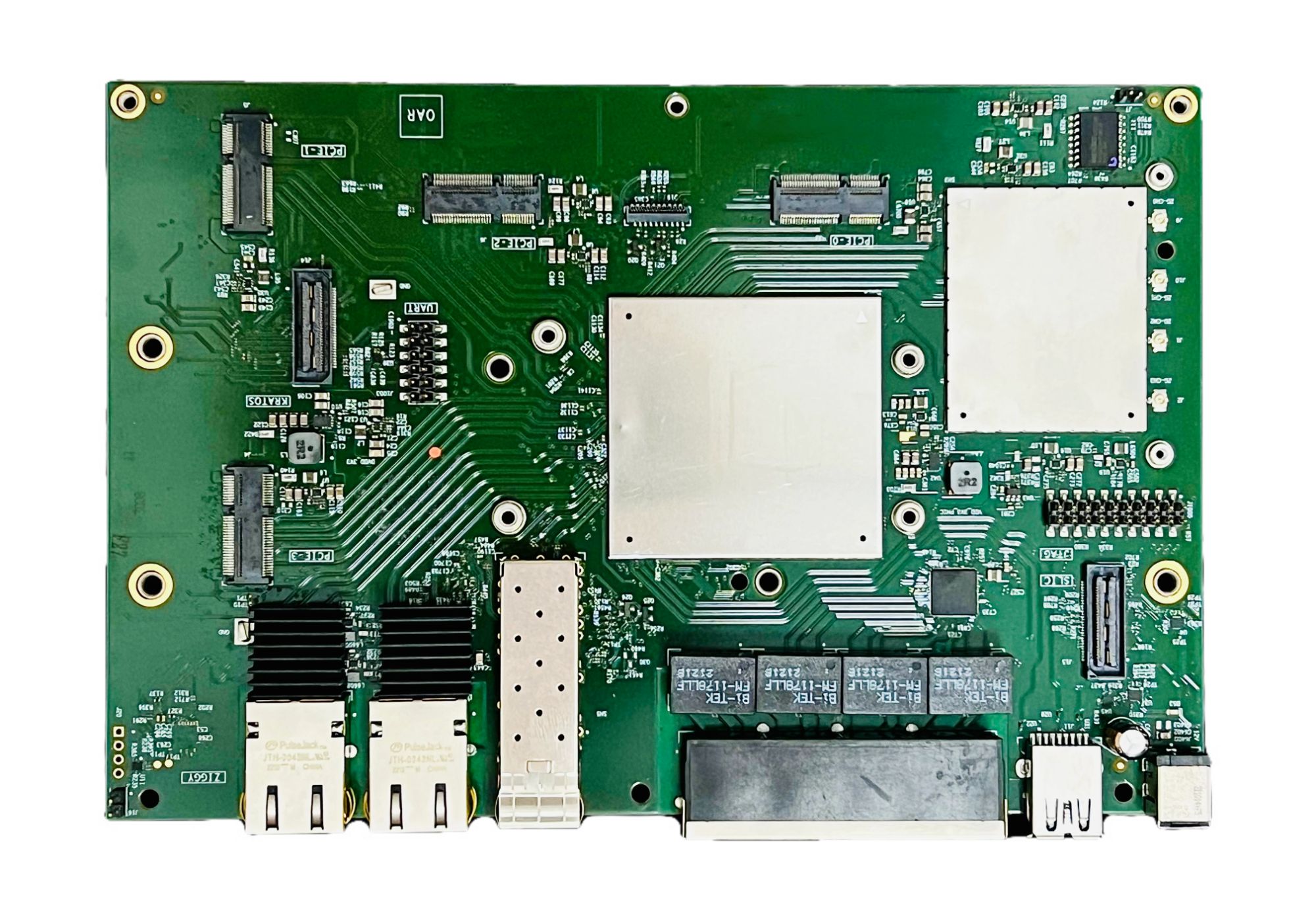

DR9574 is chipseted with Qualcomm-Atheros IPQ9574.This is the main chipset used in the system.Memory:ddr: ddr4 2GBF

差分走线要耦合出线2.差分对内等长凸起高度不能超过线距的两倍3.器件摆放干涉,后期自己调整一下放底层4.器件摆放太近5.滤波电容尽量保证一个管脚一个,原理图不够可以自己添加6.过孔不要上焊盘7.差分出线要尽量耦合以上评审报告来源于凡亿教育9

器件干涉2.地网络就近打孔,缩短回流路劲3.差分对内等长凸起高度不能超过线距的两倍4.差分走要耦合,且满足差分间距要求5.注意走线不要有直角,后期自己优化一下6.VREF的线宽最少要加粗到15mil以上7.差分对内等长误差5mil8.反馈线

扫码关注

扫码关注