- 全部

- 默认排序

注意一脚标识不要跟器件重叠了,注意调整下:注意电源信号的线宽是否满足载流:其他的没什么问题。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.

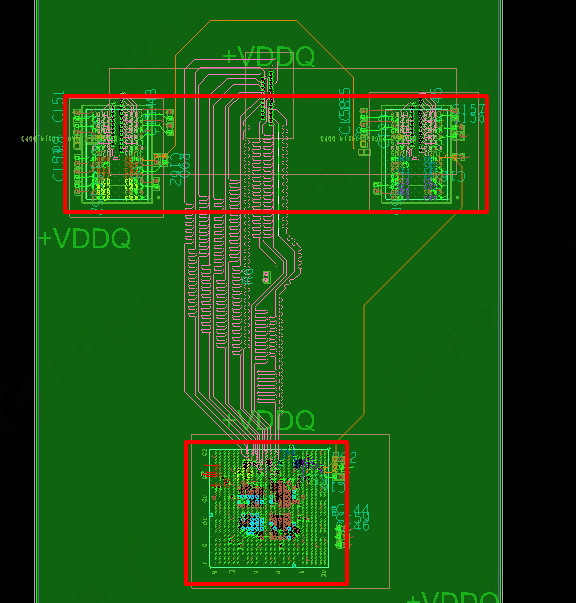

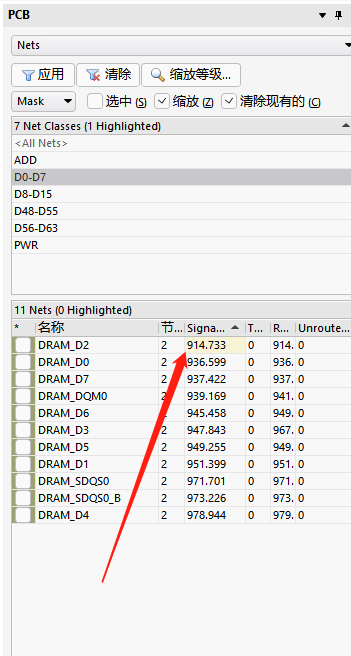

ddr之间ddr和芯片距离太远,ddr到芯片推荐600-800mil器件摆放太近丝印干涉,滤波电容推荐摆放到ddr背面靠近焊盘放置 过孔上焊盘,小器件焊盘尽量不要打孔到焊盘上差分线是主要时钟信号,尽量缩短走线电容靠近ddr中间放置差分线等长

在电子设计中,各种元件的工作电压特性是确定电源电压的关键。当工程师谈及ddr内存、CPU和硬盘等组件供电时,会发现每个组件都有其特定的电压需求,其中,+3.3V电压设置尤为常见,这是为什么?首先,ddr内存的工作电压是+3.3V,这意味着,

随着电子技术的不断发展,芯片生产工艺迭代更新,印制电路板(PCB)结构日益复杂,从最早的单片机到双面板,再到复杂的多层板结构,电路板上的布线密度越来越高。同时,随着DSP、ARM、FPGA、ddr等高速逻辑元件的应用,PCB的信号完整性和抗

多处存在开路报错焊盘应从短边出线,避免从长边和四角出线ddr和芯片放置太近,导致没有足够空间绕线,绕线很乱走线不能从同层器件中间穿过时钟线等长错误以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或

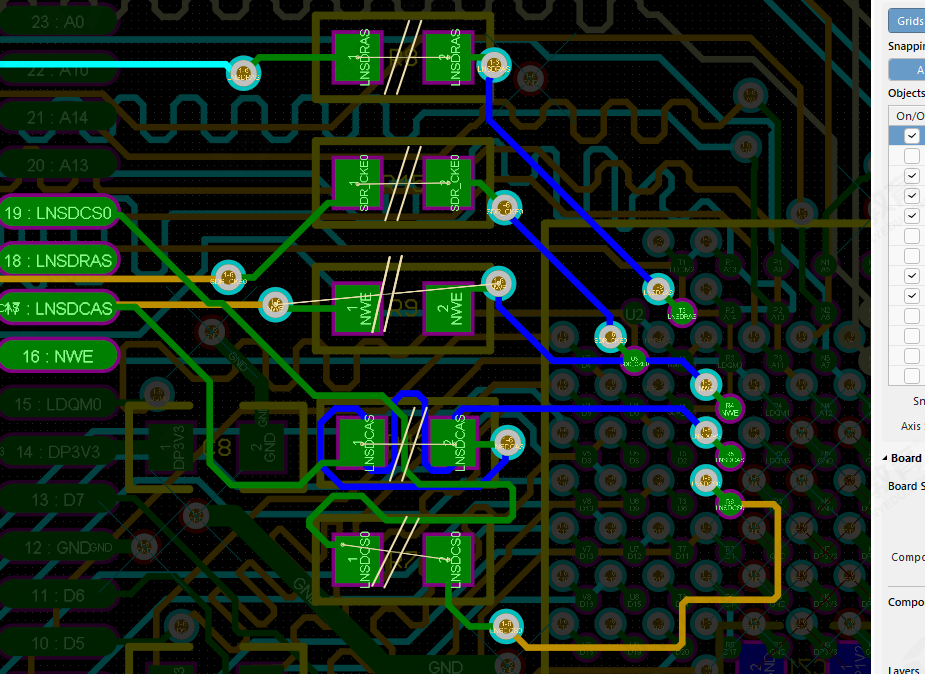

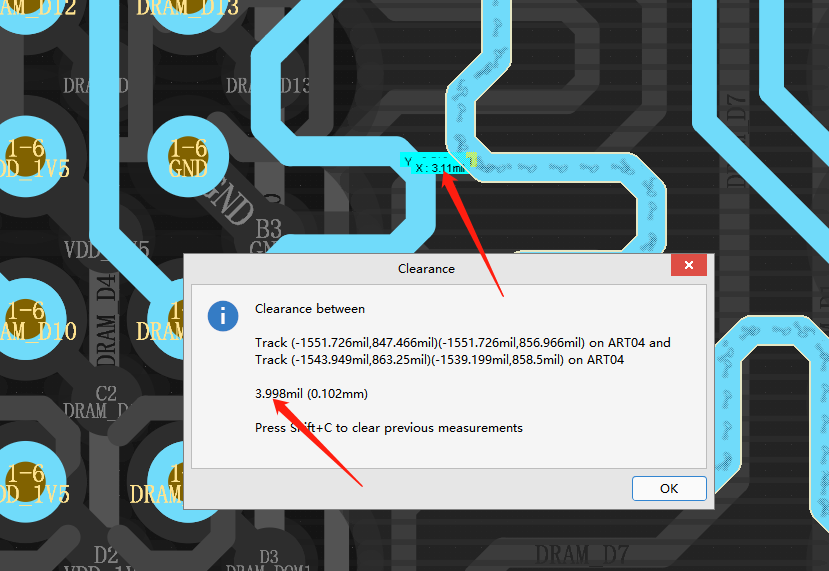

注意等长线之间需要满足3W规则2.VREF电源需要加粗到15mil以上3.等长超出误差值4.滤波电容尽量均匀摆放,确保一个管脚一个5.反馈需要加粗到10mil以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可

等长存在误差报错2.注意地址线之间等长也需要满足3W规则3.尺寸走线需要优化一下,尽量不要走直角4.地址线等长存在误差报错后期自己调整一下时钟差分信号中高端匹配电阻应该靠近T点放置等长可以在优化一下,满足3W的前提尽量紧凑一些,提高空间利用

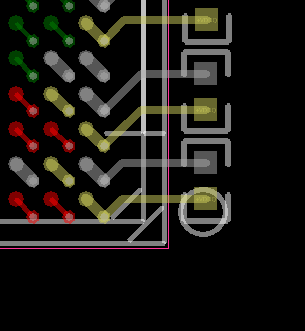

注意地址线之间等长需要满足3W间距规则2.差分对内等长凸起高度不能超过线距的两倍蛇形走线需要优化,等长尽量使用钝角,不要用圆弧或者直角,走线能拉直尽量拉直差分对内等长需要优化,原则哪里不耦合就在哪里绕等长走线到焊盘间距太近,后期容易造成短路

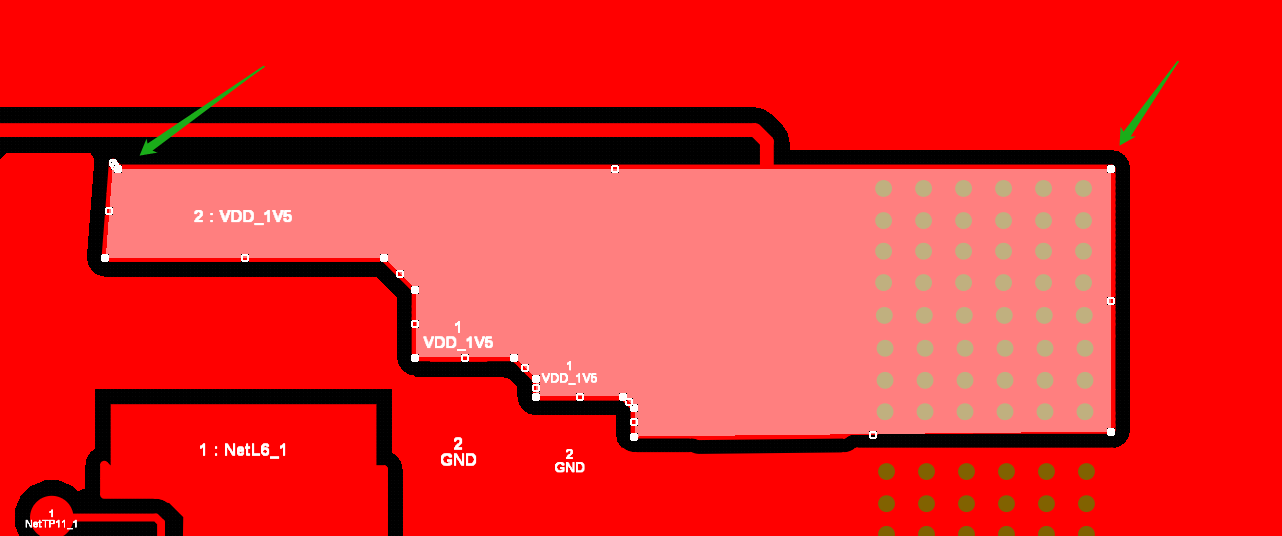

注意铜皮形状尽量钝角,不要直角以及尖角,类似情况自检修改下:走线也不能出现直角:电感内部的铜皮挖空处理:过孔按照对应的电流大小计算数量加2 或者4个裕量就行了:差分进过孔也是需要耦合连接的,优化下:注意下等长线之间需要满足3W间距:避免高速

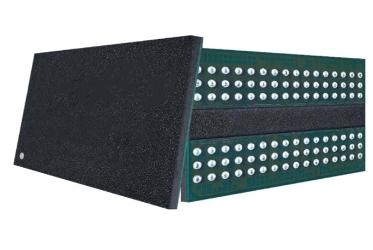

SMART ddr3(L) SDRAM组件与行业广泛兼容,并提供x8和x16配置。这些1.35v(ddr3L)和1.5V(ddr 3)器件采用标准78和96引脚网格阵列封装,时钟速度为1866 Mbps,密度为1Gb、2Gb和4Gb。KTD

扫码关注

扫码关注