- 全部

- 默认排序

类是某种特定类型设计的逻辑集合,是将多个元素进行的一个集合。在AD软件汇总结构类将这个概念进行了进一步的层次上升,结构类是一种特殊形式的类,可以归纳一下成员: 网络类 元件类 板层类 焊盘类 From To 类 差分对类设计通道类 多边形铺铜类 其他的结构类

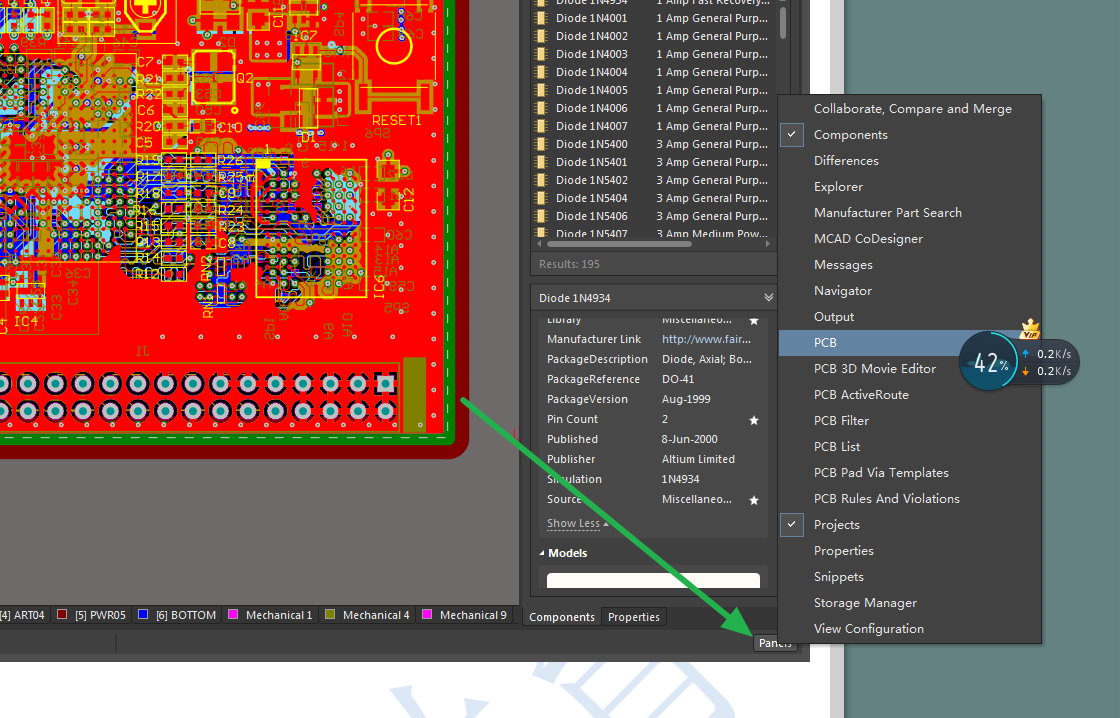

1.Altium Designer将需要做等长的线组成一个类:在Design-Classes中,右键Net Classes弹出菜单中,选择Add Class,为新New Class命名(Rename Class),加入需要的Net。

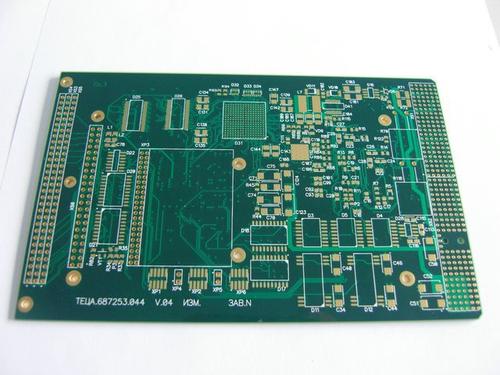

一、8 层 Allegro T 点星型拓核心板课程详情这个是一个非常经典的 T 点星型拓核心板设计,主要采用飞思卡尔 IMX6 主控芯片,4 片DDR3 同层设计,采用 DDR3 常见的 T 点拓扑结构,讲解了 DDR3 设计的信号 class 分组,信号的同组同层及常用规则注意事项,信号完整性的规划等。

一、Altium designer 6 层核心板实战视频教程详情 这个是一个非常经典的 6 层核心板设计,从新建工程到 Gerber 出具的全程视频录制;含有 BGA、Flash、DDR3 的学习,力求讲解完美完善,采用全程录制的方式,时间高达 9.5小时,不管是布局还是布线每个细节都有讲解到,力求让新手和初级工程师能够按部就班的上手学习。

此Altium Designer视频是专门针对 DDR3 设计来的,采用飞思卡尔 IMX6 主控芯片, 4 片 DDR3 同层设计,采用 DDR3 常见的 T 点拓扑结构,一个大 T 点两个小 T 点的方式。讲解了 DDR3 设计的信号 class 分组,信号的同组同层及常用规则注意事项,信号完整性的规划等,让学习者知其然知其所以然。

一、课程详情本次4 层 PADS DSP 芯片主控设计课程是一个难度适中的基于 DSP 芯片为主芯片的 4 层高速 PCB 设计项目,项目中涉及了 DSP、FPGA 芯片,使用了 SDRAM、FLasH、SRAM 等高速存储器模块。

一、PADS8层DDR3 Fly-by拓扑结构视频课程详情本pads视频课程基于飞思卡尔 i.MX6 处理器的 8层PCB设计,重点介绍 DDR3 内存的设计思路,一共四颗 DDR3,采用菊花链(Fly-By)的拓扑结构。讲解了 DDR3 设计的信号 class分组,信号的同组同层布线、信号时序等长及常用规则注意事项、信号完整性、电源完整性的规划等。

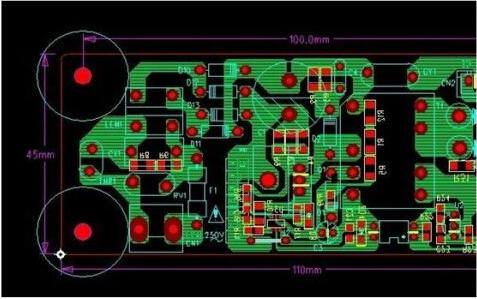

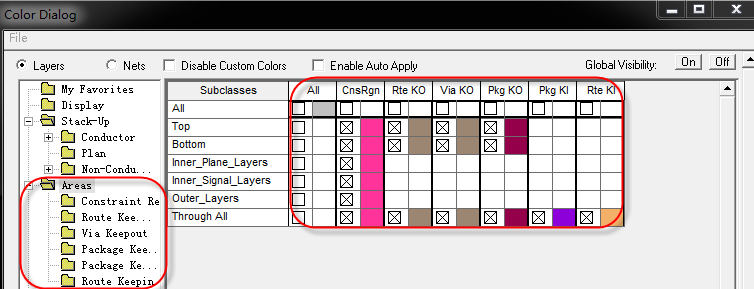

我们在进行PCB设计的时候,需要根据不同的PCB板结构以及一些电子产品的需求来进行各种不同区域的设计,包括允许布局区域设计、禁止布局区域设计。允许布线区域设计等等。在Allegro设计中,设置这些就在Areas,如图5-60所示。 图5-60 各类布局布线区域示意图Ø 在Allegro软件中有Route Keepout、Route Keepin、Package Keepout、Package Keepin、Via Keepout等多种类型的区域进行设置,对PCB工

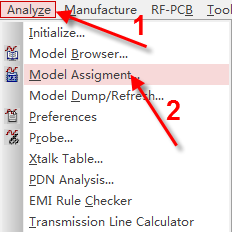

所谓的Xnet,是指在无源器件的两端,两个不同的网络,但是本质上其实是同一个网络的这种情况。比如一个源端串联电阻或者串容两端的网络。在实际设计情况中,我们需要对这种进行Xnet的设置,方便进行时序等长的设计,一般信号传输要求都是信号的传输总长度达到要求,而不是分段信号等长,这时采用Xnet就可以非常方便的实现这一功能,在Allegro软件中添加xnet的具体步骤如下所示:第一步,执行菜单命令Analyze-Model assigment,进行模型的指定,如图5-112所示; 图5-11

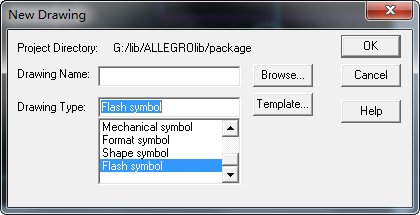

过孔也称金属化孔。在双面板和多层板中,为连通各层之间的印制导线,在各层需要连通的导线的交汇处钻上一个公共孔,公共孔一般被称为过孔。过孔制作可按以下步骤(以10/22大小过孔为例)。第一步,创建过孔所需要的Flash。打开Allegro软件,点击File-New,新建一个Flash,按图示参数创建好,保存名为Flash32,如图4-108所示, 图4-108 创建flash示意图第二步,打开Pad_Designer,按以下参数新建好过孔,如图4-109所示,设置钻孔参数,如图

扫码关注

扫码关注